# Charging-Induced Changes in Reverse Current–Voltage Characteristics of Al/Al-Rich Al<sub>2</sub>O<sub>3</sub>/p-Si Diodes

Wei Zhu, T. P. Chen, Yang Liu, Ming Yang, Student Member, IEEE, Sam Zhang, W. L. Zhang, and S. Fung

Abstract—An Al-rich  $Al_2O_3$  thin film was deposited on a p-type silicon substrate by radio frequency sputtering to form Al/Al-rich  $Al_2O_3/p$ -Si diodes. The current–voltage (I-V) characteristics of the diodes were determined by carrier injection from either the Si substrate or the Al gate and by carrier transport along the tunneling paths formed by Al nanocrystals distributed in the oxide layer. The reverse I-V characteristics were greatly affected by the charge trapping in the oxide layer, i.e., the electron trapping significantly reduced the reverse current while the hole trapping enhanced the current significantly. However, the charge trapping did not produce a large change in the forward I-V characteristic.

Index Terms—Aluminum-rich aluminum oxide, charge trapping, current transport, current-voltage characteristics, metal-insulator-semiconductor (MIS) diodes, memory effect, nanocrystals.

# I. Introduction

LUMINUM oxide  $(Al_2O_3)$  which has a high dielectric constant  $(k=\sim 8-10)$  and also a similar band gap and band alignment as silicon oxide has been proposed to be used in nonvolatile memory devices as a blocking layer or a charge storage layer [1]–[4]. Recently, Al-rich  $Al_2O_3$  thin film synthesized with electron-cyclotron-resonance sputtering at a reduced oxygen gas flow rate was shown to be a promising candidate for the charge storage layer [3]. In our previous work [5], we also observed that the Al-rich  $Al_2O_3$  thin film synthesized by reactive radio frequency (RF) sputtering had a good charge storage capability, and the charge storage behaviors were similar to that of Al-rich AlN thin films [6]. In this paper, we show that the charge trapping in the Al-rich  $Al_2O_3$  thin films

Manuscript received April 9, 2009; revised June 8, 2009. First published July 28, 2009; current version published August 21, 2009. This work was supported by the National Research Foundation of Singapore under Project NRF-G-CRP 2007-01. The work of Y. Liu was supported by the National Natural Science Foundation of China (NSFC) under Project 60806040. The review of this paper was arranged by Editor H. S. Momose.

W. Zhu, T. P. Chen, and M. Yang are with the School of Electrical and Electronic Engineering, Nanyang Technological University, Singapore 639798 (e-mail: zhuw0004@pmail.ntu.edu.sg; echentp@ntu.edu.sg).

- Y. Liu was with the School of Electrical and Electronic Engineering, Nanyang Technological University, Singapore 639798. He is now with the State Key Laboratory of Electronic Thin Films and Integrated Devices, University of Electronic Science and Technology of China, Chengdu 610054, China.

- S. Zhang and W. L. Zhang are with the School of Mechanical and Aerospace Engineering, Nanyang Technological University, Singapore 639798.

- S. Fung is with the Department of Physics, The University of Hong Kong, Hong Kong.

- Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2009.2026110

significantly changes the reverse current–voltage (I-V) characteristics of the Al/Al-rich  ${\rm Al_2O_3/p\text{-}Si}$  diodes while there is no significant change in the forward I-V characteristics. Such charging effect could be used for two-terminal charging-controlled resistive memory.

## II. EXPERIMENT

Al-rich Al<sub>2</sub>O<sub>3</sub> thin film with thickness of 60 nm was deposited on a p-type, (100)-oriented Si wafer with a resistivity of 9–12  $\Omega \cdot$  cm, which was precleaned using standard RCA process. The deposition was carried out by RF magnetron sputtering of an Al target with the purity of 99.99% in a mixed Ar/ O<sub>2</sub> atmosphere at a controlled flow rate. During deposition, the RF power was 300 W and the sputtering pressure was 0.93 Pa. The argon and oxygen flow rates were 60 and 1 sccm, respectively. No additional heating was applied during deposition; but the substrate temperature was slightly higher than the room temperature due to ion bombardment. A rapid thermal annealing was conducted at 550 °C for 30 s in N2 ambient. To fabricate the metal-insulator-semiconductor (MIS) diode structure, an ohmic contact on the Si wafer backside was formed by the deposition of a 200-nm aluminum layer, and an aluminum film of 100 nm was deposited on the surface of the Al-rich Al<sub>2</sub>O<sub>3</sub> thin film to form the gate electrode. Cross-sectional transmission electron microscopy (TEM) and X-ray photoemission spectroscopy (XPS) were used to investigate the structural and chemical properties of the Al-rich Al<sub>2</sub>O<sub>3</sub> thin film, respectively. The XPS result indicates that the as-fabricated thin film was indeed Al rich with an Al-to-Al<sub>2</sub>O<sub>3</sub> atomic ratio of 1.24, and the TEM images shows that Al nanocrystals (nc-Al) were formed in the Al<sub>2</sub>O<sub>3</sub> matrix. The details of the TEM and XPS experiments have been reported elsewhere [5]. The I-V measurement was carried out with a Keithley 4200 semiconductor characterization system, and capacitance-voltage (C-V) measurement was performed with an HP 4284A LCR meter at the frequency of 1 MHz. Both measurements were conducted at room temperature.

### III. RESULTS AND DISCUSSION

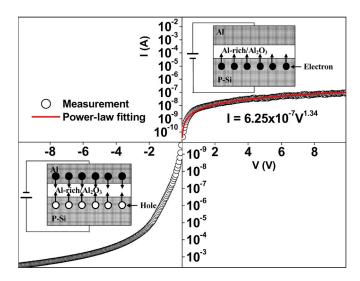

Fig. 1 shows the I-V characteristics of the MIS diode. As shown in the figure, the diode structure exhibited a "rectifying" behavior, namely, the current under the forward bias condition (i.e., the gate voltage was negative) was larger than that under

Fig. 1. I-V characteristic of the MIS diode structure. The insets in the upper right and lower left panes show the carrier injection under a reverse bias (i.e., a positive voltage is applied to the Al gate) and a forward bias (i.e., a negative voltage is applied to the gate), respectively.

the reverse bias condition (i.e., the gate voltage was positive). This behavior can be explained as follows. Both the electron injection from the Al gate and the hole (the majority carrier in the Si substrate) injection from the p-type Si substrate occurred simultaneously under a negative gate voltage; in contrast, only electron (the minority carrier in the Si substrate) injection from the Si substrate occurred under a positive gate voltage.

Fig. 1 also shows that the reverse I-V characteristic followed a power law, i.e.,  $I = I_0 V^{\zeta}$ , where the parameters  $\zeta$  and  $I_0$  were determined by both the structural properties of the oxide thin film and the charge trapping in the thin film [7]. The power law behavior suggests that the current transport was controlled by the Al-rich Al<sub>2</sub>O<sub>3</sub> layer rather than the electron injection from the Si substrate in the case of reverse bias. The powerlaw transport could be explained by a model similar to the one of collective charge transport in arrays of normal-metal quantum dots [8], [9]. The injected electrons can be transported along the tunneling paths formed by the nc-Al distributed in the aluminum oxide thin film [5], [7]. This mechanism is used to explain the observed charging-induced changes in the reversed I-V characteristics, as discussed later. On the other hand, the forward I-V characteristic cannot be described with the above power law, because the situation was more complicated as both the electrons injected from the gate electrode and the holes injected from the Si substrate were to be transported across the aluminum oxide layer.

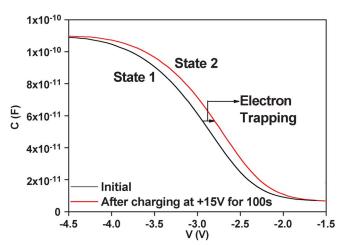

As previously mentioned, under a positive gate voltage, only electrons were injected from the Si substrate to the Al-rich  $Al_2O_3$  layer. Some of the injected electrons were trapped in the oxide layer, which caused a positive flatband voltage shift  $(\Delta V_{\rm FB})$  of the MIS structure. As shown in Fig. 2, the application of +15 V to the gate for 100 s shifted the C-V characteristic to the positive with a positive flatband voltage shift of 0.15 V  $(\Delta V_{\rm FB} = +0.15 \ {\rm V})$ , indicating that electron trapping occurred in the Al-rich  $Al_2O_3$  layer, with the possibility that the electrons could have been trapped in the nc-Al. On the other hand, as revealed by the TEM images, the interfaces between

Fig. 2. Shift in C-V characteristic after the application of +15~V for 100~s showing electron trapping in the oxide layer.

nc-Al and  $Al_2O_3$  were imperfect. Due to the imperfection of the  $Al_2O_3$  matrix with the embedded nc-Al, it is reasonable to assume that there was a large amount of defects at the interfacial regions between the embedded nc-Al and the  $Al_2O_3$  matrix. Therefore, the electrons could also be trapped in these defects. Nevertheless, the electron trapping was associated with the existence of the excess Al (i.e., nc-Al) distributed in the oxide layer. The electron trapping in either the nc-Al or the defects occurred when the injected electrons were transported along the tunneling paths formed by the nc-Al. The electron trapping, in turn, affected the carrier transport across the oxide layer, as discussed below.

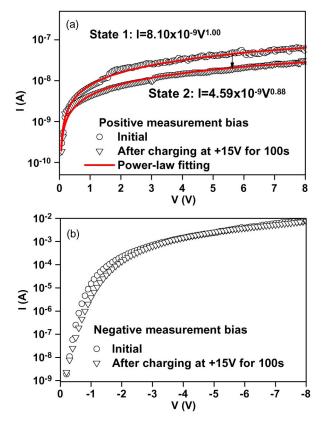

Fig. 3 shows the I-V characteristics before and after the electron trapping. The electron trapping was achieved under the same bias conditions with the same charging duration as those in Fig. 2. As shown in Fig. 3(a) for the reverse I-Vcharacteristics, the electron trapping led to a significant reduction in the current. The reverse I-V characteristic after the electron trapping also followed a power law, but with smaller values of power-law parameters,  $I_0$  and  $\zeta$ , as compared to those before the electron trapping. The influence of electron trapping on the current conduction is explained as follows. Electron trapping in an nc-Al or a defect increased the resistance of the tunneling paths involving the nc-Al or the defect because of the electrostatic interaction of the transported electrons with the trapped electrons, and the tunneling paths could also be broken due to the Coulomb blockade effect [7]. Therefore, the electron trapping suppressed the electron transport across the oxide layer. On the other hand, the electron trapping reduced the electric field in the region of the oxide/Si interface, thus decreased the electron injection from the Si substrate during the reverse I-V measurement. In contrast to the reverse I-V characteristic, the electron trapping did not have a large impact on the forward I-V characteristic, as shown in Fig. 3(b). This situation was due to the fact that both electron injection from the gate and the hole injection from the Si substrate occurred during the forward I–V measurement. The electron trapping suppressed the transport of the injected electrons but enhanced the transport of the injected holes. In addition, the electron injection was reduced while the hole injection was enhanced due to the

Fig. 3. I-V characteristics before and after the application of +15 V for 100 s. (a) Reverse I-V characteristics. (b) Forward I-V characteristics.

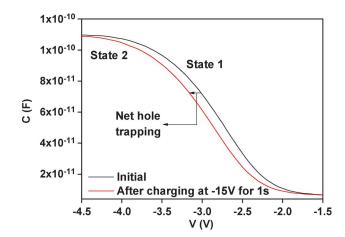

Fig. 4. Shift in C-V characteristic after the application of -15 V for 1 s showing net positive charge trapping in the oxide layer.

electron trapping. Therefore, the forward I-V characteristic was not significantly affected by the electron trapping.

Under a negative gate voltage, both the electron injection from the gate and the hole injection from the Si substrate occurred simultaneously, but the net charge trapping in the oxide layer could be either negative or positive, depending on the magnitude of the voltage and the charging duration. The net charge trapping tended to be positive for a larger voltage magnitude and a longer charging duration. As shown in Fig. 4, the application of  $-15~\rm V$  for 1 s shifted the C-V characteristic to the negative with a negative flatband voltage shift of 0.15 V  $(\Delta V_{\rm FB} = -0.15~\rm V)$ , indicating a net positive charge trapping

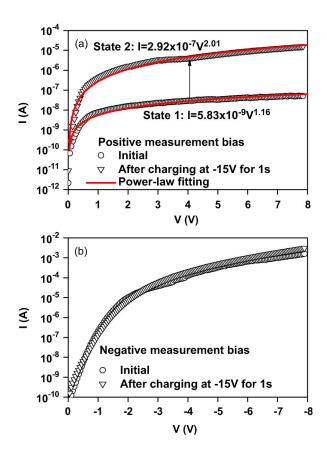

Fig. 5. I-V characteristics before and after the application of -15 V for 1 s. (a) Reverse I-V characteristics. (b) Forward I-V characteristics.

in the Al-rich  ${\rm Al_2O_3}$  layer (i.e., the hole trapping was dominant). The positive charge trapping had a strong impact on the reverse I-V characteristic. As shown in Fig. 5(a), the reverse current was increased by about two orders after the positive charge trapping. The increase in the reverse current was due to the enhancements in both the electron injection from the Si substrate and the transport of the injected electrons along the nc-Al tunneling paths during the reverse I-V measurement by the net positive charge trapping in the oxide layer. Being similar to the situation of the electron trapping discussed earlier, the positive charge trapping did not cause a large change in the forward I-V characteristics, as shown in Fig. 5(b), because both the electron injection from the gate and the hole injection from the Si substrate were involved in the forward I-V measurement.

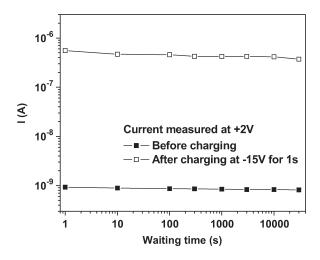

The charging effect on the reverse I-V characteristic could be used to realize a two-terminal charging-controlled resistive memory based on the MIS structure. The reverse resistance of the MIS diode can be changed by the charge trapping in the Al-rich aluminum oxide layer, i.e., the resistance is switched to a high- or low-resistance state by the electron trapping or the hole trapping, respectively. The memory states represented by the resistance states can be changed by a large voltage, and they can be distinguished by measuring the resistance (or current) at a small reverse bias. The two-terminal charging-controlled resistive memory offers a higher memory density and a lower fabrication cost. Fig. 6 shows a preliminary result of the retention performance of the memory device. The current measurement was conducted at a low bias of +2 V while the charging operation was carried out at -15 V for 1 s. As shown

Fig. 6. Currents of the two memory states (i.e., the states before and after the charging at -15 V for 1 s) measured at +2 V as a function of waiting time.

from the figure, the current ratio of the two memory states (i.e., the states before and after the charging) was large enough for distinguishing the two memory states. In addition, the currents of the two memory states had no significant changes after a waiting time of  $30\,000\,\mathrm{s}$ .

### IV. CONCLUSION

In summary, an Al-rich Al<sub>2</sub>O<sub>3</sub> thin film was deposited on a p-type silicon substrate by RF sputtering to form an Al/Al-rich Al<sub>2</sub>O<sub>3</sub>/p-Si MIS diode. Under a positive bias applied to the Al gate (i.e., reverse bias), electrons were injected from the Si substrate and some of them were trapped in the Al-rich Al<sub>2</sub>O<sub>3</sub> layer. In contrast, both the electron injection from the Al gate and the hole injection from the Si substrate occurred under a negative bias (i.e., forward bias), leading to both electron and hole trapping in the Al-rich Al<sub>2</sub>O<sub>3</sub> layer, and a positive charge trapping could be achieved with a large voltage magnitude and/or a longer charge duration. The electron trapping and hole trapping caused a significant reduction and a large increase in the reverse current, respectively. However, the charge trapping (either electron or hole trapping) did not produce a large change in the forward I-V characteristic. The charging effect on the reverse current could be used to realize a two-terminal chargingcontrolled resistive memory based on the MIS structure.

# REFERENCES

- [1] Y. Zhao, X. Wang, H. Shang, and M. H. White, "A low voltage SANOS nonvolatile semiconductor memory (NVSM) device," *Solid State Electron.*, vol. 50, no. 9/10, pp. 1667–1669, Sep./Oct. 2006.

- [2] M. Specht, H. Reisinger, F. Hofmann, T. Schulz, E. Landgraf, R. J. Luyken, W. Rösner, M. Grieb, and L. Risch, "Charge trapping memory structures with Al<sub>2</sub>O<sub>3</sub> trapping dielectric for high-temperature applications," *Solid State Electron.*, vol. 49, no. 5, pp. 716–720, May 2005.

- [3] S. Nakata, K. Saito, and M. Shimada, "Nonvolatile memory using Al<sub>2</sub>O<sub>3</sub> film with an embedded Al-rich layer," *Appl. Phys. Lett.*, vol. 87, no. 22, p. 223 110, Nov. 28, 2005.

- [4] C. H. Lee, K. I. Choi, M. K. Cho, Y. H. Song, K. C. Park, and K. Kim, "A novel SONOS structure of SiO<sub>2</sub>/SiN/Al<sub>2</sub>O<sub>3</sub> with TaN metal gate for multi-giga bit flash memories," in *IEDM Tech. Dig.*, 2003, pp. 26.5.1–26.5.4.

- [5] Y. Liu, T. P. Chen, W. Zhu, M. Yang, Z. H. Cen, J. I. Wong, Y. B. Li, S. Zhang, X. B. Chen, and S. Fung, "Charging effect of Al<sub>2</sub>O<sub>3</sub> thin films

- containing Al nanocrystals," Appl. Phys. Lett., vol. 93, no. 14, p. 142 106, Oct. 6, 2008.

- [6] Y. Liu, T. P. Chen, P. Zhao, S. Zhang, S. Fung, and Y. Q. Fu, "Memory effect of Al-rich AlN films synthesized with rf magnetron sputtering," *Appl. Phys. Lett.*, vol. 87, no. 3, p. 033 112, Jul. 18, 2005.

- [7] Y. Liu, T. P. Chen, H. W. Lau, J. I. Wong, L. Ding, S. Zhang, and S. Fung, "Charging effect on current conduction in aluminum nitride thin films containing Al nanocrystals," *Appl. Phys. Lett.*, vol. 89, no. 12, p. 123 101, Sep. 18, 2006.

- [8] A. A. Middleton and N. S. Wingreen, "Collective transport in arrays of small metallic dots," *Phys. Rev. Lett.*, vol. 71, no. 19, pp. 3198–3201, Nov. 8, 1993.

- [9] H. E. Romero and M. Drndic, "Coulomb blockade and hopping conduction in PbSe quantum dots," *Phys. Rev. Lett.*, vol. 95, no. 15, p. 156 801, Oct. 3, 2005.

**Wei Zhu** was born in Xian, China, in 1984. She received the B.Eng. degree in microelectronics from Nanyang Technological University, Singapore, in 2007, where she is currently working toward the Ph.D. degree.

Her research interest involves the electrical properties of metal-dielectric nanocomposites and their device applications.

**T. P. Chen** received the Ph.D. degree from The University of Hong Kong, Hong Kong, in 1994.

From February 1990 to October 1991, he was a Visiting Scientist with Fritz-Haber Institute of Max-Planck Society, Berlin, Germany. From 1994 to 1997, he was a Postdoctoral Fellow with The University of Hong Kong, and the National University of Singapore, Singapore. From June to December 1996, he was with Chartered Semiconductor Manufacturing, Ltd. He was with PSB Singapore for two and a half years, as a Senior Scientist, before he

joined Nanyang Technological University, Singapore, in February 2000. He is currently an Associate Professor with the Division of Microelectronics, School of Electrical and Electronic Engineering, Nanyang Technological University. He is the author or coauthor of more than 160 peer-reviewed journal papers, more than 80 conference proceeding papers, and one book chapter. He is the holder of two granted and one pending U.S. patents. His current research interests include nanoscale CMOS devices and reliability physics, semiconductor and metal nanocrystals/nanoparticles and their applications in nanoelectronic devices (memories and single/few-electron devices) and photonic/optoelectronic devices (light emitters, Plasmon waveguides, optical interconnects), Si optoelectronic integrated circuits for chip-to-chip and system-to-system communication, and flexible/printing electronics.

Yang Liu received the B.Sc. degree in microelectronics from Jilin University, Changchun, China, in 1998 and the Ph.D. degree from Nanyang Technological University, Singapore, Singapore, in 2005.

From May 2005 to July 2006, he was a Research Fellow with Nanyang Technological University. In the year of 2008, he joined University of Electronic Science and Technology of China, as a Full Professor. He is currently a Professor with the School of Microelectronics, University of Electronic Science and Technology of China, Chengdu, China. His cur-

rent research includes nanoscale CMOS device physics and reliability physics (reliability of CMOS device and memory devices, etc.), nanocrystals and their applications in electronic devices (nanocrystal-based Flash memory, resistive memory, few-electrons devices, etc.) and photonic/optoelectronic devices (Sibased light emitters, optoelectronic memory), and Si-based optical ICs. He is the author or coauthor of more than 50 journal papers and over 16 conference papers.

Dr. Liu was awarded the prestigious two-year Singapore Millennium Foundation Fellowship in 2006.

Ming Yang (S'06) was born in Xiamen, China, in 1982. He received the B.Eng. degree (first-class honors) in microelectronics from Nanyang Technological University, Singapore, in 2005, where he is currently working toward the Ph.D. degree.

His research interest involves the electrical and optoelectronic properties of nanoscale materials and their device applications.

W. L. Zhang was born in Kaifeng, Henan Province, China in 1980. He received the B.Eng. degree in material science from Dalian Jiaotong University, Dalian, China, in 2003 and the M.Eng. degree in material science from Shanghai Jiaotong University, Shanghai, China, in 2006. He is currently working toward the Ph.D. degree at Nanyang Technological University, Singapore, Singapore.

His research interest involves the electronic properties of Si nanostructure.

Sam Zhang received the Ph.D. degree in ceramics from The University of Wisconsin, Madison, in 1991.

He is currently a tenured Full Professor with the School of Mechanical and Aerospace Engineering, Nanyang Technological University, Singapore. He has been in processing and characterization of nanocomposite thin films and coatings for 17 years and has authored/coauthored more than 200 peer reviewed international journal papers, 14 book chapters, and edited 9 Journal volumes, published one

book in 2007, one book in 2008, and another set of 3 books are in press (2009). He also holds Guest Professorship with Zhejiang University (since 2006) and Harbin Institute of Technology (since 2007). He was featured in the first ever Who's Who in Engineering Singapore (2007), and featured in 26th (2009) edition of Who's Who in the World (published November 12, 2008). He became Fellow of the Institute of Materials, Minerals and Mining, U.K., in October 2007. His research and publications are detailed in his home page at http://www.ntu.edu.sg/home/msyzhang.

Dr. Zhang serves as Editor-in-Chief for Nanoscience and Nanotechnology Letters and Principal Editor for Journal of Materials Research (USA). In 2003, he was conferred the title of Honorary Fellow of Singapore Institute of Manufacturing Technology, and in 2004, he was an Honorary Professor of the Institute of Solid State Physics, Chinese Academy of Sciences.

**S. Fung** was born in Hong Kong in 1950. He received the B.A. degree in physics (first-class honors), the Ph.D. degree in semiconductor physics, and the D.Sc. degree from The University of Oxford, Oxford, U.K., in 1977, 1980, and 1996, respectively.

He is currently a Professor with the Department of Physics, The University of Hong Kong, Hong Kong. His research interests are nanomaterials, wide-bandgap semiconductors, and positron physics.

Dr. Fung is a Fellow of the Institute of Physics, U.K.