# Effects of Mismatch on CMOS Double-Balanced **Mixers: A Theoretical Analysis**

Jun Wang and Alfred K.K. Wong

Department of Electronic and Electrical Engineering University of Hong Kong, Pokfulam Road, Hong Kong

E-mail: junwang@eee.hku.hk

Abstract-Effects of mismatch on CMOS double-balanced mixers are studied. The mixer is analyzed as a two-stage circuit. The effects of mismatch, including second-order intermodulation, feedthrough and degradation of conversion gain, are discussed for each stage. A relation between processing-induced variances of transistor parameters and mixer performance is derived.

#### I. INTRODUCTION

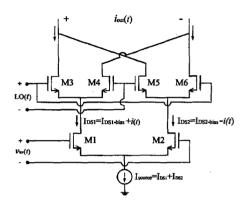

Processing-induced device mismatch causes independent random variations in physical quantities of identically designed devices [1-5]. The impact of MOS transistor mismatch becomes more important as dimensions of devices are reduced and the available signal swing decreases [1]. Mismatch is a fundamental design parameter for precision analog circuit design [2]. As critical blocks in wireless transceivers, mixers are very susceptible to mismatch effects. The double-balanced CMOS mixer [6][7], as shown in Fig.1, is a commonly used topology in CMOS integrated receivers for frequency translation of radio-frequency (RF) carrier signals by converting a localoscillator (LO) and the incoming RF signal into an intermediatefrequency (IF). Under normal conditions, this mixer produces only odd harmonics at its output  $i_{out}(t)$ . In the presence of mismatch, however, the input transistor pair (M1 and M2) introduces second-order intermodulation, which feeds through the cascaded mismatched switch pairs and cause undesirable spectral components at baseband. This is not a critical issue in high IF architectures, because a band pass filter following the mixer can eliminate the spurious signals in baseband. Therefore, in conventional double-conversion (Heterodyne) receivers that convert RF signals into high IFs, mixers are only required to have a high third-order intercept point (IP3) [8] in order to meet system linearity specifications. However, in zero and low IF architectures, the even-order distortion terms are also of particular concern [9]. As the direct-conversion receiver architecture [10], in which a zero IF is used, has been attracting attention as a possible solution to a single-chip receiver, mismatch effects in CMOS mixers deserve attention.

Mismatch in a mixer is induced by factors both intrinsic and extrinsic to the transistors. The intrinsic factors are those arising from transistor devices whereas the extrinsic ones include asymmetries in other parts of circuit such as wire length, feed-in and feed-out resistors. While the even-order distortion terms are also induced by factors such as single-ended input and output of a double-balanced mixer [11] in addition to mismatch, only effects originating from intrinsic transistor mismatch are considered in this study.

This paper introduces a theoretical analysis of mismatch effects on CMOS double-balance mixer. The model used to characterize MOSFET mismatch will be presented in Section II.

The effects of mismatch effects on the input V-I converter and switch pairs are discussed in Section III.

Fig.1. Double-balanced CMOS mixer.

#### II. MISMATCH MODEL

A MOSFET model is needed for the mismatch study. This model should be detailed enough such that it reflects accurately the behavior of sub-micrometer transistors. An acceptable MOSFET model in the saturation region is [12]

$$I_{DS} = \frac{1}{2} \beta \frac{(V_{GS} - V_T)^2}{1 + \theta(V_{GS} - V_T)} , \qquad (1)$$

$I_{DS} = \frac{1}{2}\beta \frac{(V_{GS} - V_T)^2}{1 + \theta(V_{GS} - V_T)} \quad , \tag{1}$  where  $I_{DS}$  is the drain current,  $V_{GS}$  is the gate-source voltage,  $V_T$ is the threshold voltage,  $\beta = C_{OX} \mu \frac{W}{L}$  is the current factor,

with  $C_{OX}$  being the gate-oxide capacitance per unit-area,  $\mu$  as the carrier mobility, W and L being the width and length of the transistor respectively. The parameter  $\theta$  is the effective mobility [13], which includes the effects of surface scattering and the source series resistance. For a minimum-length device of an existing 0.8-µm technology, it was estimated to be 0.9 V<sup>-1</sup>. For a different 0.25-µm technology, it was found to be approximately

Within this model, the parameter set  $\left\{\frac{\Delta\beta}{\beta}, \Delta V_T, \Delta\theta\right\}$  is

used for matching description. The mismatch model can be derived by differentiating Eq.(1) with respect to the parameter

$$\frac{\Delta I_{DS}}{I_{DS}} = \frac{\Delta \beta}{\beta} + \frac{1}{I_{DS}} \frac{\partial I_{DS}}{\partial V_T} \Delta V_T + \frac{1}{I_{DS}} \frac{\partial I_{DS}}{\partial \theta} \Delta \theta . \qquad (2)$$

Assuming Gaussian distribution for the mismatch parameters [1], these parameters can be characterized by their variances:  $\sigma^2 \frac{\Delta \beta}{\beta}$ ,  $\sigma^2 \Delta V_T$ ,  $\sigma^2 \Delta \theta$ , and their correlations coefficients. The variance of mismatch in the current is thus given by

$$\sigma^{2} \frac{\Delta I_{DS}}{I_{DS}} = \sigma^{2} \frac{\Delta \beta}{\beta} + \left(\frac{1}{I_{DS}} \frac{\partial I_{DS}}{\partial V_{T}}\right)^{2} \sigma^{2} \Delta V_{T} + \left(\frac{1}{I_{DS}} \frac{\partial I_{DS}}{\partial \theta}\right)^{2} \sigma^{2} \Delta \theta + \text{correlation terms}$$

(3)

The values of these standard deviations and correlation coefficients can be evaluated by various means [1–5]. In this paper, we assume that all of these values have been determined.

#### III. MISMATCH ANALYSIS IN MIXER

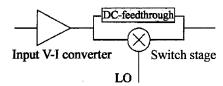

The operation of a double-balanced mixer can be modeled by the diagram in Fig.2. The RF input stage is a transconductance converter. This stage corresponds to transistors M1 and M2 in Fig.1. The LO signal drives the switching stage that is implemented by transistors M3–M6. There is also a feedthrough path from the RF input stage to the output of mixer in the presence of mismatch in the switch pairs [15], as we will discuss below.

Fig. 2. Mixer model with input V-I converter, switch stage and DC-feedthrough path [15].

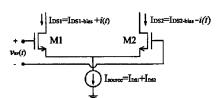

Fig.3. Input V-I converter

## A. Mismatch effects on input V-1 converter

Let us first consider the input V-I converter, as shown in Fig.3. It is convenient for later exposition to express  $V_{GS}$  of the transistor as a function of  $I_{DS}$ . We thus invert Eq.(1):

$$V_{GS} = f(I_{DS}, \beta, \theta, V_T)$$

$$= \frac{\theta}{\beta} I_{DS} \cdot \left( 1 + \sqrt{1 + \frac{2\beta}{\theta^2 I_{DS}}} \right) + V_T$$

(4)

In the presence of mismatch, the values of the parameters in Eq.(4) are different for the two transistors. Using the subscripts 1 and 2 to denote parameters of the transistors, we can express Eq.(4) as a Taylor series:

$$\begin{cases} v_{GS1} = \Delta V_{GS1} = \Delta f_1(I_{DS1}) = f_1'\hat{i}_1 + \frac{f_1''}{2}\hat{i}_1^2 + \frac{f_1'''}{6}\hat{i}_1^3 + \cdots \\ v_{GS2} = \Delta V_{GS2} = \Delta f_2(I_{DS2}) = f_2'\hat{i}_2 + \frac{f_2'''}{2}\hat{i}_2^2 + \frac{f_2'''}{6}\hat{i}_2^3 + \cdots \end{cases} , (5)$$

where f is the function in Eq.(4) with the subscripts denoting different parameters values of M1 and M2, f, f', f'' and f''' are the derivatives of this function respect to  $I_{DS}$ , and the number of primes denotes the order of the derivative.

number of primes denotes the order of the derivative.

Taking the difference between the expressions in Eq.(5) and noting that  $v_{RF} = v_{GS1} - v_{GS2}$  and  $i_1 = -i_2 = i$ , we obtain the input signal  $v_{RF}$  as a function of the output current i:

$$v_{RF} = \Delta V_{GS1} - \Delta V_{GS2}$$

$$= (f_1' + f_2')i + \frac{f_1'' - f_2''}{2}i^2 + \frac{f_1''' + f_2'''}{6}i^3 + \cdots$$

(6)

To express i in terms of  $v_{RF}$ , Eq.(6) can be rewritten as

$$i = \frac{1}{f_1' + f_2'} v_{RF} - \frac{1}{2} \frac{f_1'' - f_2''}{(f_1' + f_2')^3} v_{RF}^2 + \left[ \frac{1}{2} \frac{(f_1'' - f_2'')^2}{(f_1' + f_2')^5} - \frac{1}{6} \frac{f_1''' + f_2''}{(f_1' + f_2')^4} \right] v_{RF}^3 + \cdots$$

(7)

Because the mismatch in parameters is small compared with their values, we can approximate Eq.(7) by

$$i = \frac{1}{2f'} v_{RF} - \frac{1}{16} \frac{\Delta f''}{f'^3} v_{RF}^2 - \frac{1}{48} \frac{f'''}{f'^4} v_{RF}^3 , \qquad (8)$$

where

$$f' = \frac{f_1' + f_2'}{2}$$

,  $f''' = \frac{f_1''' + f_2'''}{2}$  and  $\Delta f'' = f_1'' - f_2''$ .

Without transistor mismatch,  $\Delta f'' = 0$ . The even-order term in Eq.(8) vanishes. Only odd harmonic terms appear at the output of the V-I converter. Furthermore, as we will prove later, the ideally matched switch pairs in double-balanced mixer will also prevent even-order terms in the input stage from appearing at the output of switch stage.

Equating the first-order and second-order terms in Eq.(8), the second-order intercept point (IIP2) [6] is

$$v_{IIP2} = \frac{\frac{1}{2f'}}{\frac{1}{16} \frac{\Delta f''}{f'^3}} = \frac{8f'^2}{\Delta f''} = \frac{8f'^2}{f''' \cdot \Delta I_{DS}} = \frac{8f'^2}{f''' \cdot I_{DS}} \cdot \frac{\Delta I_{DS}}{I_{DS}}.$$

(9)

Substituting Eq.(2) into Eq.(9), we obtain the relation between  $v_{\rm IIP2}$  and the transistor mismatch parameters.

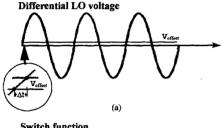

#### B. Mismatch effects on switch pair

Now let us consider the effects of mismatch on the switch pairs. Without loss of generality, consider only the left switch pair shown in Fig.1. The output of the RF V-I converter stage is  $I_{DS1} = I_{DS1-bias} + i(t)$ . We define the switch point of two transistors to be the point when the output differential current  $(I_{DS3} - I_{DS4})$  is zero. To further simplify the analysis, assume that the circuit switches sharply. Thus, in the absence of mismatch, for positive values of the LO voltage, M3 switches ON and M4 switches OFF, and a current equal to I<sub>DS1</sub> appears in the left branch. In the next half period, the current switches to the right branch. Thus, the output is a square-wave at frequency of  $\varpi_{LO}~$  with no DC value, where  $\varpi_{LO}~$  is the angular frequency of the LO. In the presence of mismatch, a bias voltage is needed to make the output differential current zero. This voltage arises from transistor mismatch and is time-independent if we ignore the effect of temperature. So we can say that the circuit has a DC offset voltage  $V_{\it offset}$  [16]. This offset voltage can be calculated by the following functions:

Throwing functions.

$$\begin{cases} V_{GS} + \Delta V = f(I_{DS}, \beta + \Delta \beta, \theta + \Delta \theta, V_T + \Delta V_T) \\ V_{GS} = f(I_{DS}, \beta, \theta, V_T) \end{cases}, (10)$$

$$V_{offset} = \Delta V \approx \frac{\partial f}{\partial \beta} \Delta \beta + \frac{\partial f}{\partial \theta} \Delta \theta + \frac{\partial f}{\partial V_T} \Delta V_T, \qquad (11)$$

where  $f(\bullet)$  denotes the function in (4).

Since the offset voltage arises from manufacture variations, we can characterize it statistically as follows:

$$\sigma^2 v_{\rm offset} = \left(\beta \cdot \frac{\partial f}{\partial \beta}\right)^2 \sigma_{\frac{\Delta \beta}{\beta}}^2 + \left(\frac{\partial f}{\partial \theta}\right)^2 \sigma_{\Delta \theta}^2 + \left(\frac{\partial f}{\partial V_T}\right)^2 \sigma_{\Delta V_T}^2 \ , \ (12)$$

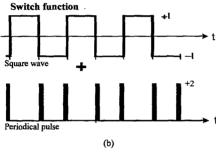

The transfer characteristic of the switch pair can thus be represented by the superposition of a periodic pulse and a squarewave as showed in Fig.4. [17].

Fig.4. Mixer output current can be represented by the superposition of a periodic pulse and a square wave in the presence of offset voltage [17].

Transistor mismatch can thus be represented by a skew in the switching time  $\Delta t$ . It is determined by the offset voltage  $V_{\it offset}$  and the slope of the LO voltage S at switching time:

$$\Delta t = \frac{V_{offset}}{S} \,. \tag{13}$$

Using the symbols  $\Pi(t)$  and  $\Lambda_{\Delta t}(t)$  respectively to represent a square-wave with no DC value at an angular frequency  $\varpi_{LO}$  and a periodic pulse with pulse width  $\Delta t$  and an angular frequency of  $2\varpi_{LO}$  , and letting  $i_{out}$  to be the output current of the double-balanced mixer in Fig.1, we can write  $i_{out}$

$$i_{out} = [I_{DS1-bias} + i(t)] [\Pi(t) + \Lambda_{\Delta t_1}(t)] - [I_{DS2-bias} - i(t)] [\Pi(t) + \Lambda_{\Delta t_2}(t)].$$

(14)

The equation can be re-written as

$$i_{out} = \underbrace{\begin{bmatrix} I_{DS1-bias} \cdot \Lambda_{\Delta I_1}(t) - I_{DS2-bias} \cdot \Lambda_{\Delta I_2}(t) \end{bmatrix}}_{\text{DC-Feedthrough}} + \underbrace{i(t) \begin{bmatrix} 2\Pi(t) + \Lambda_{\Delta I_1}(t) + \Lambda_{\Delta I_2}(t) \end{bmatrix}}_{\text{mixed output signal}},$$

(15)

#### i ) Feedthrough

Only the DC component of the first term in (15) affects the output of the mixer. Thus, the DC-feedthrough signal at the output of mixer is

$$\begin{split} I_{DC-Feedthrouh} &= I_{DS1-bias} \frac{4V_{offset1}}{T \cdot S} - I_{DS2-bias} \frac{4V_{offset2}}{T \cdot S} \\ &= \frac{4}{T \cdot S} \Big[ I_{DS-bias} \cdot \Delta V_{offset} - \Delta I_{DS-bias} \cdot V_{offset} \Big] \quad , \quad (16) \\ &\approx \frac{2}{T \cdot S} I_{source} \cdot \Delta V_{offset} \end{split}$$

where

$$I_{source} = 2I_{DS-bias} = I_{DS1-bias} + I_{DS2-bias} ,$$

$$\Delta I_{DS-bias} = I_{DS1-bias} - I_{DS2-bias} , \quad V_{offset} = \frac{V_{offset1} + V_{offset2}}{2} ,$$

$\Delta V_{offset} = V_{offset1} - V_{offset2}$  and T is the period of the LO. For a sine-wave LO,  $T \cdot S = 2\pi \cdot (2V_{LO}) = 4\pi V_{LO}$ , where  $V_{LO}$  is the amplitude of the LO and the factor of two accounts for the fact that  $\Delta V_{\it offset}$  is compared to a differential LO signal with an amplitude of  $2V_{LO}$  [12]. So we can get

$$I_{DC-feedthrough} = \frac{I_{source}}{2\pi V_{LO}} \Delta V_{offset} \,. \tag{17}$$

Since  $V_{\it offset1}$  and  $V_{\it offset2}$  are two independent random variables with the same distribution, the variance of the feedthrough gain can be calculated as

$$\sigma_{I_{DC-feedthrough}}^{2} = \left(\frac{2}{T \cdot S}\right)^{2} \sigma_{V_{offset1} - V_{offset2}}^{2}$$

$$= \left(\frac{2}{T \cdot S}\right)^{2} \cdot 2\sigma_{V_{offset}}^{2} = \frac{1}{2\pi^{2} V_{LO}^{2}} \sigma_{V_{offset}}^{2}$$

(18)

#### ii ) Conversion Gain

The desired output signal at the output of the mixer is the first-order term of the mixed output signal in Eq.(15)

> $-\frac{4}{\pi}\left[1+\left(\frac{e^{-j\varpi\Delta t_1}-1}{2}\right)^2+\left(\frac{e^{-j\varpi\Delta t_2}-1}{2}\right)^2\right]\cdot i(t),$  $\approx -\frac{4}{\pi} \left[ 1 + \left( \frac{-j\varpi\Delta t_1}{2} \right)^2 + \left( \frac{-j\varpi\Delta t_2}{2} \right)^2 \right] \cdot i(t)$

where  $j = \sqrt{-1}$  and  $\varpi = \varpi_{LO}$ . Substituting Eq.(13) into Eq.(19), we obtain

Gain<sub>switch</sub> =

$$\frac{i_{out-desired}}{i} = \frac{4}{\pi} \left( 1 - \frac{1}{16} \frac{V_{offset1}^2 + V_{offset2}^2}{V_{LO}^2} \right)$$

, (20)

Using the expression for  $V_{offset1}$  and  $V_{offset2}$  in the prior section, the expected value of the conversion gain is

$$E_{\text{Gain}_{\text{switch}}} = \frac{4}{\pi} \left( 1 - \frac{1}{8} \frac{\sigma_{V_{\text{offlatt}}}^2}{V_{LO}^2} \right)$$

(21)

## iii ) Gain of the second-order intermodulation (IM2)

When two close tones at  $\varpi_{RF1}$  and  $\varpi_{RF2}$  are presented at the input of RF V-I converter, the sum and the differential frequencies can be generated at the input of the switch pairs. The non-zero DC term of the mixed output signal in Eq.(15) will transfer the differential frequencies to the output of the mixer, causing even-order distortion. The IM2 conversion gain and its variance can be calculated as

$$Gain_{IM 2} = \frac{4}{T \cdot S} \left( v_{offset1} - v_{offset2} \right) = \frac{\Delta V_{offset}}{\pi V_{LO}}, \qquad (22)$$

$$\sigma_{Gain_{IM2}}^2 = \frac{2}{\pi^2 V_{IO}^2} \sigma_{V_{offset}}^2$$

(23)

#### C. Overall effects of Cascaded V-I Converter and Switch Pair

So far, the effects of mismatch on RF input V-I converter and switch pair has been discussed separately. To analyze the combined effects of mismatch in each stage, the second-order intermodulation product and the overall conversion gain of the cascaded stages will be examined.

First, consider the second-order intermodulation product. Using the equations we derived in prior sections, we obtain

$$\frac{\mathbf{i}_{IM2}}{v_{RF}} = \frac{1}{16} \frac{\Delta f''}{f'^3} \cdot \frac{\Delta V_{offset}}{\pi V_{LO}} \\

= \left(\frac{1}{16} \frac{f''''}{f'^3} \frac{I_{DS-bias}}{\pi V_{LO}}\right) \frac{\Delta I_{DS-bias}}{I_{DS-bias}} \Delta V_{offset}$$

(24)

The variance of second-order intermodulation transconductance is

$$\sigma_{\tilde{1}_{\underline{\text{IM}2}}}^{2} = 2 \left( \frac{1}{16} \frac{f'''}{f'^{3}} \frac{I_{DS-bias}}{\pi V_{LO}} \right)^{2} \sigma_{\frac{\Delta I_{DS-bias}}{I_{DS-bias}}}^{2} \sigma_{V_{offber}}^{2}.$$

(25)

The overall conversion gain of the desired signal is

$$Gain = \frac{i_{out-desired}}{v_{RF}} = Gain_{switch} \cdot \frac{1}{2f'}$$

$$= \frac{2}{\pi} \left( 1 - \frac{1}{16} \frac{V_{offset1}^2 + V_{offset2}^2}{V_{LO}^2} \right) \cdot \frac{1}{f'}$$

(26)

Similar to the calculation in the prior section, the expected value of conversion gain is

$$E_{Gain} = \frac{2}{\pi} \left( 1 - \frac{1}{8} \frac{\sigma_{V_{offset}}^2}{V_{LO}^2} \right) \cdot \frac{1}{f'} . \tag{27}$$

For a mixer with minimum-length transistors in a 0.8- $\mu$ m technology, the expected loss in gain is less than 5%. This effect can be alleviated by decreasing  $I_{source}$ , increasing  $V_{LO}$ , or using larger size transistors in mixer.

## IV. CONCLUSIONS

Processing-induced mismatch in CMOS double-balanced mixer can cause adverse effects such as DC feedthrough, decrease in IIP2, and the reduction in conversion gain. A relation between the variances of the mismatch parameters and the mismatch effects on the mixer has been presented. This model can provide estimates of the needed degree of transistor matching.

#### REFERENCES

- M. J. M. Pelgrom, A. C. J. Duinmaijer, and A. P. G. Wellbers, "Matching properties of MOS transistors," *IEEE J. Solid-state Circuits*, vol. 24, pp.1433-1440. 1989.

- R. Gregor, "On the relationship between topography and transistor matching in an analog CMOS technology," *IEEE*

- Transaction of Electron Devices, vol. 39, no. 2, pp. 271-282, Feb. 1992.

- E. Felt, A. Narayan and A. Sangiovanni-Vincentelli, "Measurement and modeling of MOS transistor current mismatch in analog IC's," ACM 0-89791-690-5/94/0011/0272, pp. 272-277, 1994.

- J. Bastos, M. Steyaert, R. Roovers, P. Kinget and W. Sansen, "Mismatch characterization of small zise MOS transistors," Proc. IEEE 1995 Int. Conf. On Microeletronic Test Structures, vol. 8, pp. 271-276, Mar. 1995.

- T. Serrano-Gotarredona and B. Linares-Barranco, "Cheap and easy systematic CMOS transistor mismatch characterization," *IEEE 0-7803-4455-3/98*, pp. II466-II469, 1998

- B. Gilbert, "A precise four quadrant multiplier with sub nanosecond response," *IEEE J. Solid-State Circuits*, vol. SC-3, pp.365-373, Dec. 1968.

- 7. T. H. Lee, The design of CMOD radio-frequency integrated circuits, pp. 319-322, Cambridge University, 1998.

- R. C. Meyer, "Intermodulation in high-frequency bipolar transistor integrated circuit mixers," *IEEE J. Solid-State Circuits*, vol. SC-21, pp. 534-537, Aug. 1986.

- B. Razavi, "Design considerations for direct conversion receiver," *IEEE Trans. Circuits Syst. II*, vol. 44, pp. 428-435, June 1997.

- A. A. Abidi, "Direct-conversion radio transceivers for digital communications," *IEEE J. Solid-State Circuits*, vol. 30, pp. 1399-1410, Dec. 1995.

- B. Razavi, RF microelectronics, pp. 185-187, Prentice Hall, 1998

- P. R. Gray and R. G. Meyer, Analysis and design of analog integrated circuits, 3<sup>rd</sup> Ed. pp. 71-76, New York: Wiley, 1993

- Y. P. Tsividis, Operation and modeling of the MOS transistor, 2<sup>nd</sup> Ed. pp. 181-189, New York: McGraw-Hill, 1999.

- M. T. Terrovitis and R. G. Meyer, "Intermodulation distortion in current-commutating CMOS mixers," *IEEE J. Solid-State Circuits*, vol. 35, NO. 10, pp. 1461-1473, Oct. 2000

- D. Coffing and E. Main, "Effects of offsets on bipolar integrated circuits mixer even-order distortion terms," *IEEE Trans. on Microwave theory and Techniques*, vol. 49, no. 1, pp. 23-30, Jan. 2001.

- B. Razavi, Design of analog CMOS integrated circuits, pp. 465-471, McGraw-Hill, 2001.

- H. Darabi and A. A. Abidi, "Noise in RF-CMOS mixers: a simple physical model," *IEEE Trans. on Solid State Circuits*, vol. 35, no. 1, pp. 15-25, Jan. 2000.