# Suppressed Growth of Interlayer GeO<sub>x</sub> in Ge MOS Capacitors with Gate Dielectric Prepared in Wet NO Ambient

P. T. Lai,<sup>1</sup> C. X. Li,<sup>1</sup> \*J. P. Xu,<sup>2</sup> X. Zou,<sup>2</sup> C. L. Chan,<sup>1</sup>

Abstract — Wet NO oxidation with wet  $N_2$ anneal is used to grow GeON gate dielectric on Ge substrate. As compared to dry NO oxidation, negligible growth of GeO<sub>x</sub> interlayer and thus a near-perfect GeON dielectric can be obtained by the wet NO oxidation. As a result, MOS capacitors prepared by this method show greatly reduced interface-state and oxide-charge densities and gate leakage current. This should be attributed to the hydrolysable property of GeO<sub>x</sub> in water-containing atmosphere.

## I. INTRODUCTION

Germanium MOSFETs with high-k gate dielectrics ( $ZrO_2$  [1], HfO\_2 [2-5] and Al<sub>2</sub>O<sub>3</sub> [5]) have received more and more attention for the future high-speed CMOS technology due to the much higher carrier mobilities of Ge than Si (two times higher for electrons and four times for holes). However, higher since the deposition of high-k material usually occurs in an oxidizing ambient [6-7], germanium substrate could be oxidized to form the water-soluble and unstable germanium oxide  $(GeO_x)$  [8-9]. For overcoming this problem, various processes were used to improve the interface quality, including  $NH_3$ surface treatment [2-5] to form a GeO<sub>x</sub>N<sub>y</sub> interlayer, and Si interlayer technique with several monolayers of Si grown between the dielectric and the substrate by SiH<sub>4</sub> surface annealing [10-11]. But nitrogen incorporation in the former method may not be sufficient to fully passivate the dangling bonds on the Ge surface and prevent its oxidation, while the thickness of the Si interlayer in the latter method has to be accurately controlled to prevent parasitic Si channel, thus increasing the processing difficulty. In this work, a novel process is proposed to fabricate high-quality GeO<sub>x</sub>N<sub>y</sub> gate

dielectric by oxidizing Ge in an NO plus water-vapor atmosphere. As a result, growth of the  $GeO_x$  interlayer is effectively suppressed, and high-quality GeO<sub>x</sub>N<sub>y</sub> bulk and GeO<sub>x</sub>N<sub>y</sub>/Ge interface with low oxide-charge and interface-state densities and greatly reduced gate leakage current are obtained. This should be due to the water-soluble property of  $GeO_x$  in the wet ambient. For comparison, Ge MOS capacitors are also prepared in dry NO ambient. Obvious differences in electrical properties between the wet and dry NO-oxidized samples can be observed.

## II. EXPERIMENTS

MOS capacitors were fabricated on (100)-oriented n-type Ge substrate with a doping concentration of  $2.65 \times 10^{16}$  cm<sup>-3</sup>. The wafers were cleaned using trichloroethylene and acetone followed by cyclic HF (50:1 diluted HF solution) dip with DI water rinsing to remove Ge native oxide [2]. Thermal oxidation at 550 °C was carried out in dry or wet NO ambients (denoted as RNOG and WNOG samples respectively). For better evaluating the performance of the GeON dielectric and the influence of the  $GeO_x$ interlayer, a relatively long oxidation time of 20 min was used. Then, the WNOG sample received a wet N<sub>2</sub> anneal, while the DNOG sample had a dry  $N_2$  anneal, all for 5 min at the same temperature. The wet NO and N<sub>2</sub> atmospheres were realized by bubbling pure NO and N<sub>2</sub> gases through de-ionized water at 95 °C with a flow rate of 250 ml/min for NO and 500 ml/min for  $N_2$ . Al was thermally

<sup>&</sup>lt;sup>1</sup> Department of Electrical and Electronic Engineering, the University of Hong Kong, Pokfulam Road, Hong Kong. E-mail: laip@eee.hku.hk

<sup>&</sup>lt;sup>2</sup> Department of Electronic Science & Technology, Huazhong University of Science & Technology, Wuhan, P. R. China E-mail: <u>jpxu@mail.hust.edu.cn</u>

evaporated and patterned as the gate electrode of the MOS capacitors with an area of  $7.85 \times 10^{-5}$  cm<sup>2</sup>. Finally, a thermal anneal was carried out in forming gas (H<sub>2</sub>/N<sub>2</sub>) ambient for 20 min at 300 <sup>0</sup>C.

High-frequency (HF, 100 kHz and 1 MHz) capacitance-voltage (C-V) characteristics were measured at room temperature using HP4284A precision LCR meter. Oxide capacitance (hence flat-band voltage, oxide thickness), and oxide-charge density were extracted from the 100-kHz C-V curve. The interface-state density at midgap was extracted also from the 100-kHz C–V curve using the Terman method [12]. The gate leakage current was measured by HP 4156A precision semiconductor parameter analyzer. All measurements were carried out under a light-tight and electrically-shielded condition.

#### **III. RESULTS AND DISCUSSION**

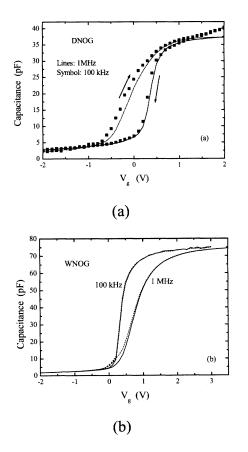

Fig. 1 shows the typical HF C-V curves of the samples under dark condition, swept in both directions and measured at frequencies of 1 MHz and 100 kHz respectively. As expected, a large hysteresis is observed for the DNOG sample due to growth of the GeO<sub>x</sub> interlayer during dry-NO oxidation, leading to high interface and near-interface trap densities. However, growth of the GeO<sub>x</sub> interlayer gets effectively suppressed when the oxidation is carried out in wet NO ambient, as shown by the very small hysteresis in the C-V curves of the WNOG sample and its identical C<sub>ox</sub> at 1 MHz and 100 kHz, implying less interface and near-interface traps.

Table 1 Oxide capacitance and thickness, oxide-charge and interface-state densities, and flatband voltage of the samples extracted from 100-kHz HF C-V curve.

| Sample | Cox  | t <sub>ox</sub> | Qox                   | D <sub>it</sub> at midgap            | V <sub>fb</sub> |

|--------|------|-----------------|-----------------------|--------------------------------------|-----------------|

|        | (pF) | (nm)            | $(cm^{-2})$           | $(\mathrm{cm}^{-2}\mathrm{eV}^{-1})$ | (V)             |

| DNOG   | 46.1 | 121             | $-1.3 \times 10^{12}$ | 1×10 <sup>12</sup>                   | 0.33            |

| WNOG   | 60.6 | 92              | -5.7×10 <sup>11</sup> | 6×10 <sup>11</sup>                   | 0.28            |

Fig. 1 Typical high-frequency C-V curves of the samples under dark condition at room temperature, swept in both directions at frequencies of 1 MHz and 100 kHz respectively. Area of capacitor is  $7.85 \times 10^{-5}$  cm<sup>2</sup>. (a) DNOG sample and (b) WNOG sample.

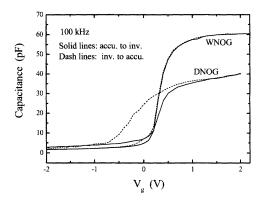

For comparing the qualities of the oxynitride and its interface properties with Ge substrate more clearly, their C-V curves measured at 100 kHz are replotted in Fig. 2. The values of electrical thickness (tox) of the gate oxynitride and flat-band voltage (V<sub>fb</sub>) extracted from the 100-kHz C-V curves are listed in Table 1. The equivalent oxide-charge density (Q<sub>ox</sub>) is calculated as  $-C_{ox}(V_{fb} - \phi_{ms})/q$ , where the work-function difference  $\phi_{ms}$ between Al and Ge is calculated to be -0.0311 V. Obviously, the DNOG sample has the smallest Cox, and thus the largest thickness, mainly due to the growth of  $GeO_x$  interlayer during dry-NO oxidation. However, the GeO<sub>x</sub> growth is considerably suppressed due to hydrolyzation of GeO<sub>x</sub> in the water-vapor

atmosphere (i.e. once the  $GeO_x$  is grown, it is hydrolyzed in the wet ambient), thus giving an almost perfect GeON gate dielectric with a smaller thickness for the sample oxidized in wet NO ambient. The suppressed growth of GeO<sub>x</sub> interlayer in the wet NO ambient is highly desirable for fabricating advanced small-scaled Ge MOSFET with the GeON as gate dielectric or as ultrathin interlayer of dielectrics. high-k stack gate The wet-NO-oxidized sample exhibits excellent oxynitride bulk and interface properties with reduced Qox and Dit as compared to the DNOG sample, further supporting the negligible growth of the GeO<sub>x</sub> interlayer and thus better interface quality. Therefore, the wet NO oxidation is beneficial for preparing high-quality thin GeON as the gate dielectric or interlayer of high-k stack gate dielectric in Ge MOSFET.

Fig. 2 High-frequency C-V curves of the samples under dark condition at room temperature, swept in both directions at 100 kHz. Area of capacitor is  $7.85 \times 10^{-5}$  cm<sup>2</sup>

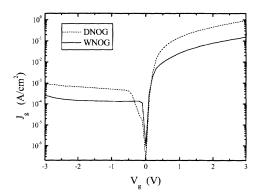

Fig. 3 Gate leakage properties of the samples.

Fig. 3 is the gate leakage properties of the samples. The DNOG sample shows the large

gate leakage current due to the existence of the  $GeO_x$  interlayer. For the wet-NO-oxidized sample, lower gate leakage current is observed, despite its smaller tox than that of the DNOG sample. This should be due to the greatly suppressed  $GeO_x$  growth and thus low oxide-charge and interface-state densities when the oxidation is performed in the wet NO ambient, as mentioned above. The negative equivalent oxide charge should be related to the forming-gas anneal and wet oxidation/anneal ambient. The former tends to decrease the positive fixed oxide charge generated by nitridation [14] while the latter could induce negative charges near/at the interface [15]. The origin of the negative charges might be OH<sup>-</sup>. which cannot diffuse out from the interface at the low temperature of 550 °C [15]. For the DNOG sample, the negative  $Q_{ox}$  should be mainly due to the high acceptor-like interface and near-interface trap densities of the GeO<sub>x</sub> interlayer because the equivalent oxide charge includes not only fixed oxide charge but also interface and near-interface trap charges.

### **IV. SUMMARY**

A new wet-NO oxidation is employed to fabricate GeON gate dielectric on Ge substrate. Compared with dry NO oxidation, the wet NO oxidation followed by a wet N2 anneal gives an almost perfect GeON gate dielectric with a negligible GeO<sub>x</sub> interlayer, greatly reduced interface-state and oxide-charge densities and gate leakage current. The mechanisms involved probably lie in the hydrolysable property of GeO<sub>x</sub> in water-containing atmosphere. In a word, this technique is highly promising for preparing high-quality GeON gate dielectric in Ge MOS devices. Moreover, it can easily make excellent ultrathin GeON interlayer when HfO2 or other high-k dielectrics is used as the gate dielectric of Ge MOSFET.

#### ACKNOWLEDGEMENT

This work is financially supported by the National Natural Science Foundation of China (NSFC, Grant No. 60576021), and the RGC of HKSAR, China (Project No. HKU 7142/05E).

- [1] C. O. Chui, H. Kim, D. Chi, B. B. Triplett, P. C. McIntyre, and K. C. Saraswat, "A sub-400 <sup>0</sup>C germanium MOSFET technology with high-k dielectric and metal gate," in *IEDM Tech. Dig.*, 2002, pp. 437-440.

- [2] W. P. Bai, N. Lu, J. Liu, A. Ramirez, D. L. Kwong, D. Wristers, A. Ritenour, L. Lee, and D. Antoniadis, "Ge MOS characteristics with CVD HfO<sub>2</sub> gate dielectrics and TaN gate electrode," in *VLSI Symp. Tech. Dig.*, 2003, pp. 121-122.

- [3] A. Ritenour, S. Yu, M. L. Lee, N. Lu, W. Bai, A. Pitera, E. A. Fitzgerald, D. L. Kwong, and D. A. Antoniadis, "Epitaxial strained germanium p-MOSFETs with HfO<sub>2</sub> gate dielectric and TaN gate electrode," in *IEDM Tech. Dig.*, 2003, pp. 433-436.

- [4] C. O. Chui, H. Kim, P. C. Mcintyre, and K. C. Saraswat, "A germanium nMOSFET process integrating metal gate and improved hi-k dielectrics," in *IEDM Tech. Dig.*, 2003, pp. 437-440.

- [5] J. J. Chen, N. A. Bojarczuk, H. Shang, M. Copel, J. B. Hannon, et al., "Ultrathin Al<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub> gate dielectrics on surface-nitrided Ge," *IEEE Trans. Electron Devices*, vol. 51, no. 11, pp. 1441-1447, Nov. 2004.

- [6] M. Cho, J. Park, H. B. Park, C. S. Hwang, J. Jeong, and K. S. Hyun, "Chemical interaction between atomic-layer-deposited HfO<sub>2</sub> thin films and the Si substrate," *Appl. Phys. Lett.*, vol. 81, pp. 334-336, 2002.

- [7] J. Park, B.K. Park, M. Cho, C.S. Hwang, K. Oh, D.Y. Yang, "Chemical vapor deposition of HfO<sub>2</sub> thin films using a novel carbon-free precursor: Characterization of the interface with the silicon substrate," *J. Electrochem Soc*, vol.149, pp.G89-G94, 2002.

- [8] N. Wu, Q. Zhang, C. Zhu, C. C. Yeo, S. J.

Whang, et al., "Effect of surface  $NH_3$  anneal on the physical and electrical properties of  $HfO_2$  films on Ge substrate," *Appl. Phys. Lett.*, vol. 84, pp. 3741-3743, 2004.

- [9] Y. A. Hu, J. –T. Zettler. S. Chongsawangvirod, Y. Q. Wang, and E. A. "Spectroscopic Irene, ellipsometric measurements of the dielectric function of germanium dioxide films on crystal germanium," Appl. Phys. Lett., vol. 61, pp. 1098-1100, 1992.

- [10] W. P. Bai, N. Lu, and D. -L. Kwong, "Si interlayer passivation on germanium MOS capacitors with high-k dielectric and metal gate," *IEEE Electron Deavice Lett.*, vol. 26 no. 6, pp. 378-380, 2005.

- [11] N. Wu, Q. Zhang, C. Zhu, D. S. H. Chan, et al., "A TaN-HfO<sub>2</sub>-Ge pMOSFET with novel SiH<sub>4</sub> surface passivation," *IEEE Electron Deavice Lett.*, vol. 25 no. 9, pp. 631-633, 2004.

- [12] L. M. Terman, "An investigation of surface states at a silicon/silicon oxide interface employing metal-oxide-silicon diodes," *Solid-State Electron.*, vol. 5, pp. 285–299, 1962.

- [13] T. Hori, H. Iwasaki, Y. Naito, and H. Esaki, "Electrical and physical characteristics of thin nitrided oxides prepared by rapid thermal nitridation," *IEEE Trans. Electron Devices*, vol. 34, p. 2238, 1987.

- [14] C. O. Chui, F. Ito, K. C. Saraswat, "Scalability and electrical properties of germanium oxynitride MOS dielectrics," *IEEE Electron Device Lett.*, vol. 25, no. 9, p. 613, 2004.

- [15] H. Yano, F. Katafuchi, T. Kimoto, et al., "Effects of wet oxidation/anneal on interface properties of thermally oxidized SiO<sub>2</sub>/SiC MOS system and MOSFET's," *IEEE Trans. Electron Devices*, vol. 46 (3), pp. 504-510, 1999.