# Effects of oxidation temperature on Ga<sub>2</sub>O<sub>3</sub> film thermally grown on GaN

Limin Lin, Yi Luo, P.T. Lai, and Kei May Lau

Abstract - The effects of oxidation temperature on thermally oxidized GaN film were investigated. The GaN wafers were oxidzied at 750 °C, 800 °C and 850 °C respectively. The electrical characteristics and interface quality of MOS capacitors were compared among different oxidation temperatures. The sample oxidized at 800 °C presented best current-voltage, capacitance-voltage characteristics and smoothest surface morphology, while the higher oxidation temperature of 850 °C gave best interface quality. The electrical breakdown field was increased by one order of magnitude when the sample was oxidized at 800 °C as compared with 750 °C and 850 °C. Lastly, after the sample oxidized at 800 °C was annealed at 850 °C for 10 min, the quality of its oxide was significantly degraded.

## I. INTRODUCTION

GaN is one kind of wide-bandgap III-V semiconductor materials and has many advantages such as high breakdown field and low thermal generation rate. Lots of researches for GaN have focused on light- emitting diodes (LEDs) [1]. On the other hand, it can also be suitable candidate for high-power and high-temperature electronic applications. A number of dielectrics such as SiO<sub>2</sub> [2], Ga<sub>2</sub>O<sub>3</sub> (Gd<sub>2</sub>O<sub>3</sub>) [3], Sc<sub>2</sub>O<sub>3</sub> [4], MgO [5] have been applied in GaN MIS devices. Ga<sub>2</sub>O<sub>3</sub> thermally grown in dry oxygen achieved a low interface-state density at the level of 10<sup>10</sup> cm<sup>-2</sup>eV<sup>-1</sup> [6] and its breakdown field could reach 3.85 MVcm<sup>-1</sup> [7].

Stability at high temperature is critical for GaN to be applied in high-temperature and high-power systems. It been found that the low-temperature photoluminescence (PL) intensity increased after GaN samples were annealed at up to 700 °C, but degraded with inferior crystalline quality due to point defects and antisite defects when the annealing temperature was further increased to 900 °C [8]. The sheet resistance of GaN dropped approximately 3 orders of magnitude after annealing up to 900 °C, which should be due to N vacancies as confirmed by AES [9]. Moreover, the surface of GaN became pitted after RTA at 1000 °C [9]. According to Groh. Et al., loss of nitrogen began at 710 °C and significant loss happened when temperature was higher than 980 °C [10]. SiO<sub>2</sub> deposited on GaN by LPCVD was claimed to be degraded after NO or NH3 annealing at 1100 °C for 5 min [11].

Limin Lin, Yi Luo and P.T. Lai are with the department of Electrical and Electronic Engineering, The University of Hong Kong, Hong Kong, E-mail: <a href="mailto:laip@eee.hku.hk">laip@eee.hku.hk</a>. Kei May Lau is with the department of Electrical and Electronic Engineering, The Hong Kong University of Science and Technology, Hong Kong.

Dry oxidation at 900 °C was found to form a rough surface morphology [12], while wet oxidation at 800 °C achieved better surface morphology but poorer electrical characteristic compared with dry oxidation [13]. In this work, we report on the effects of oxidation temperature ranging from 750 °C to 850 °C. The electrical characteristics, interface quality and surface morphology were compared among different oxidation temperatures.

# II. EXPERIMENT

A layer of Si-doped n-type GaN with a doping level of 5×10<sup>17</sup> cm<sup>-3</sup> was grown by MOCVD on c-plane sapphire with a layer of un-doped GaN buffer layer. The wafer was cleaned in trichloroethylene, acetone and ethanol in an ultrasonic bath for 5 min respectively and rinsed in de-ionized water. Then the wafer was dipped into 1:10 NH<sub>4</sub>OH solvent for 15 min at 50 °C to remove the native oxide and contaminants. 300 nm SiO<sub>2</sub> layer was deposited on the GaN surface by rf sputtering to work as mask for oxidation. The samples were loaded into a furnace at 300 °C in argon ambient. After raise the temperature to 750 °C (sample denoted as 750) or 800 °C (sample denoted as 800), a 12-h oxidation was carried out in dry oxygen ambient and followed by a 0.5-h annealing in argon at the same temperature. Also a 5-h oxidation was performed at a higher temperature of 850 °C (sample denoted as 850). Another sample had oxidation at 800 °C and was further annealed at a higher temperature of 850 °C for 10 min (denoted as 800-850). It took about 5 min to raise the temperature from 800 °C to 850 °C and drop from 850 °C to 800 °C at a speed of 3 °C/min. After removing the SiO<sub>2</sub> mask, Al was evaporated to form the electrodes. Finally, the MOS capacitors were annealed at 450 °C for 30 min in nitrogen ambient to get good contacts.

## III. RESULTS AND DISCUSSIONS

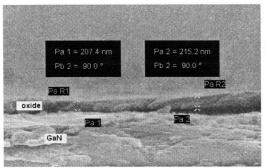

About 240 nm, 220 nm, 100 nm oxide layers were formed after thermal oxidation at 850 °C for 5 h, 800 °C for 12 h and 750 °C for 12 h respectively, which were confirmed by both cross-sectional SEM and high-frequency capacitance in accumulation region. Fig. 1 shows the measurement of oxide thickness after a 12-h oxidation at 800 °C by SEM.

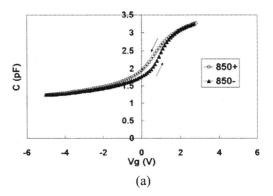

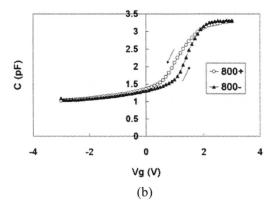

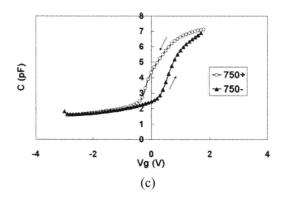

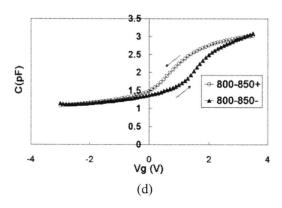

The high-frequency capacitance-voltage curves for different oxidation temperatures are shown in Fig. 2 (a $\sim$  d). It can be seen that the sample with oxidation and annealing at 800 °C presents best shape in the accumulation region and sharp transition from accumulation to deep depletion region. When gate voltage was swept in different directions, the 850 and 800 samples presented smaller hysterisis than the 750 and 800-850 samples, implying

Fig. 1. Cross-sectional SEM image of thermally oxidized GaN at 800 °C for 12 h.

Table I: Electrical and physical parameters extracted from the high-frequency C-V curves.

| Sample                                           | 850   | 800   | 750   | 850-800 |

|--------------------------------------------------|-------|-------|-------|---------|

| $T_{ox}(A)$                                      | 2406  | 2218  | 1022  | 2335    |

| $V_{fb}(V)$                                      | 3.24  | 2.25  | 1.17  | 2.35    |

| $Q_{ox}$ (×10 <sup>11</sup> cm <sup>-2</sup> )   | -6.48 | -5.27 | -5.41 | -5.24   |

| D <sub>it</sub>                                  | 9.84  | 51    | 56.5  | 7.12    |

| $(\times 10^{11} \text{cm}^{-2} \text{eV}^{-1})$ | 7.04  | 51    | 50.5  | 7.12    |

fewer slow traps in the oxides. The parameters extracted from the high-frequency C-V curves can be seen in Table I. The oxide thickness  $T_{ox}$  in Table I was calculated from the  $C_{ox}$ , which was approximated by the maximum value at the accumulation region. The positive  $V_{fb}$  indicates generation of acceptor-type interface states or negative fixed charges.

Oxide-charge density is determined from the shift of flatband voltage:

$$V_{fb} = \phi_{Al,GaN} - \frac{Q_{ox}}{C_{ox}} \tag{1}$$

where  $\phi_{{\scriptscriptstyle Al,GaN}}$  is the work-function difference between Al and GaN,

$$\phi_{Al,GaN} = \chi + E_g / 2 - (kT/q) \ln(N_d / n_i)$$

(2)

$\chi$  is the electron affinity of GaN (4.07 eV);  $E_g$  is the forbidden bandgap of GaN (3.4 eV); k is the Boltzman's constant and T is the measurement temperature (298 K);  $n_i$  is the intrinsic carrier concentration of GaN (2.0×10<sup>-10</sup> cm <sup>-3</sup>) at room temperature;  $N_d$  is the doping level of the GaN wafer (5×10<sup>17</sup> cm<sup>-3</sup>). The flatband voltage corresponds to the value of  $C_{tb}$ .

$$C_{fb} = \frac{C_{ox}C_S}{C_{ox} + C_S} \tag{3}$$

where

$$C_s = \varepsilon_{GaN} \varepsilon_0 / L_D$$

(*L<sub>D</sub>* is the Debye length) (4)

$$L_D = (kT\varepsilon_{GaN}\varepsilon_0/q^2N_d)^{1/2}$$

(5)

Therefore,

$$\frac{C_{fb}}{C_{ox}} = \left(1 + \frac{396\sqrt{T/300}}{T_{ox}\sqrt{N_d}}\right) \tag{6}$$

Fig. 2 High-frequency C-V curves of MOS capacitors measured in a dark chamber. (a) 5-h oxidation and 30-min annealing at 850 °C; (b) 12-h oxidation and 30-min annealing at 800 °C; (c) 12-h oxidation and 30-min annealing at 750 °C; (d)12-h oxidation at 800 °C and 10-min annealing at 850 °C. '+' means the gate voltage is swept from positive to negative direction; '-' means the opposite sweeping direction.

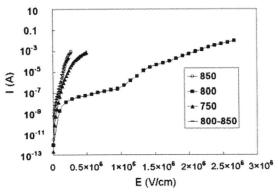

Fig. 3. Gate leakage current versus electrical field. The cross–sectional area of the MOS capacitor is  $7.85 \times 10^{-5}$  cm<sup>2</sup>.

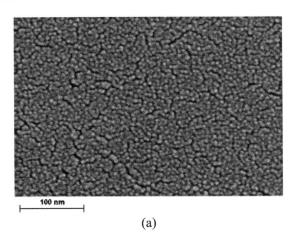

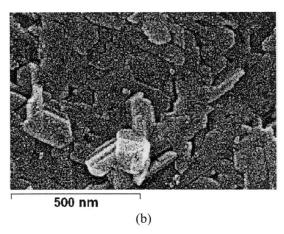

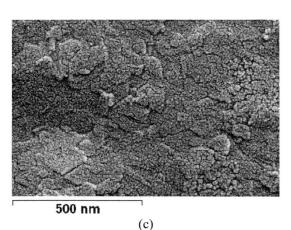

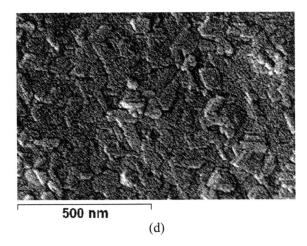

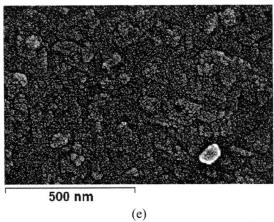

Fig. 4. Surface morphology by scanning electron microscopy. (a) original GaN; (b) oxide grown at 850 °C; (c) oxide grown at 800 °C; (d) oxide grown at 750 °C; (e) oxide grown at 800 °C and annealed at 850 °C for 10 min.

The interface-state density  $D_{it}$  is calculated by using the single-frequency approximation [14].

$$D_{it} = \frac{2}{qA} \frac{G_{m,\text{max}}/\omega}{(\frac{G_{m,\text{max}}}{\omega C_{ox}})^2 + (1 - \frac{C_m}{C_{ox}})^2}$$

(7)

where  $G_{m,max}$  corresponds to the maximum conductance on the G-V curve;  $\omega$  is the measurement frequency;  $C_m$  is the measured capacitance; A is the capacitance area.

It can be seen that the interface states are suppressed when the annealing temperature is 850 °C. The high-temperature annealing can restore the crystallinity of the oxide and improve the interface quality between GaN and oxide layer. However, it increases the intrinsic defects, such as Ga or O vacancies to form acceptor or donor traps and antisite defects. Therefore, after the high-temperature processing at 850 °C, the current-voltage characteristic was degraded significantly (see Fig. 3). The sample oxidized at 800 °C and annealed at 850 °C has similar characteristic as the one with oxidation and annealing at 850 °C, which should be due to the decomposition of GaN and oxide layer at 850 °C. The sample with oxidation at 750 °C also presents poor I-V characteristic, which is probably due to incomplete oxidation at low temperature and lack of

crystallinity for annealing at 750 °C. The sample with oxidation at 800 °C presents much better current-voltage characteristic compared with the others. If the breakdown current density is defined as 3 mA/cm<sup>2</sup>, the breakdown field of the sample 800 is 1 MV/cm.

Fig. 4 shows the surface morphology of the oxide layer formed at different temperatures. There are some dark lines on the surface of the original GaN sample (Fig. 4 (a)), which can be threading dislocation due to the lattice mismatch and thermal conductivity mismatch between sapphire and GaN. The samples were oxidized faster around the regions of dislocation, thus forming rough oxide surface (Fig. 4 (b)~(e)). The samples with oxidation at 800 °C and 750 °C have surfaces smoother and denser than the one formed at 850 °C. It can be seen that the 850 sample has larger granular structures than the 800 and 750 samples because of much faster oxidation rate at 850 °C and decomposition of oxide layer to increase the roughness and defects of oxide layer, which agrees with its much poorer current-voltage characteristic. The 800-850 sample seems not to form as large granular structures as the 850 sample due to its lower oxidation temperature, but it presents poor electrical characteristic as well, which should be due to the decomposition of oxide during the annealing at 850 °C. There are also some white droplets remained on the surfaces of the 850 and 800-850 samples, which could be associated with atoms diffusing out of the oxide. The surface of the 750 sample has rougher morphology than that of the 800 sample, which maybe due to incomplete oxidation and lack of crystallinity of the film.

The energy-dispersive X-ray analysis (EDX) results of the oxides are shown in Table II. The ratio of Ga to O is about 0.77 for the sample with oxidation at 850  $^{\circ}$ C without any annealing, which is close to the ratio of Ga<sub>2</sub>O<sub>3</sub> (Ga:O=0.67). After the annealing at 850  $^{\circ}$ C for 0.5 h, oxygen loss happened and the ratio of Ga to O was increased to 1.28. For the other samples, nitrogen atoms were detected in the dielectric, which should be due to the incomplete oxidation at lower temperature.

Table II: EDX results and oxide composition ratio.

| Sample              | Ga<br>(%) | O<br>(%) | N<br>(%) | Ratio             |

|---------------------|-----------|----------|----------|-------------------|

| 850-<br>nonannealed | 43.5      | 56.1     | 0        | Ga: O=0.77        |

| 850                 | 56.1      | 43.9     | 0        | Ga:O=1.28         |

| 800                 | 45.2      | 34.6     | 20.3     | Ga:O:N=1.3:1:0.6  |

| 750                 | 45.9      | 33.9     | 20.3     | Ga:O:N=1.35:1:0.6 |

| 800-850             | 54.6      | 31.7     | 13.8     | Ga:O:N=1.7:1:0.4  |

### IV. CONCLUSION

In summary, the sample with oxidation at 800 °C has best current-voltage, capacitance-voltage characteristics and surface morphology. However, the sample oxidized at higher temperature of 850 °C presents better interface quality. More traps formed at the interface between GaN and the dielectric may be due to the incomplete oxidation at low temperature. The sample with oxidation at 800 °C and annealing at 850 °C has poor current-voltage

characteristic and degraded performance like the one oxidized at 850 °C, which should be due to the decomposition of oxide and GaN at this temperature.

### ACKNOWLEDGEMENT

This work is supported by the RGC of HKSAR, China (Project No.: HKU 7163/03E).

# REFERENCES

- [1] S. Nakamura, T. Mukai, and M. Senoh, "High-Power GaN P-N Junction Blue-Light-Emitting Diodes", *Jpn .J. Appl. Phys. 1*, 30(12A), p. L1998-L2001,1991.

- [2] S. Arulkumaran, T.Egawa, H. Ishikawa, T. Jimbo, and M.Umeno, "Investigations of SiO<sub>2</sub>/n-GaN and Si<sub>3</sub>N<sub>4</sub>/n-GaN insulator-semiconductor interfaces with low interface state density", *Appl. Phys. Lett.*, 73(6), p. 809-811,1998.

- [3] F. Ren, M. Hong, S. N. G. Chu, M. A. Marcus, M. J. Schuurman, A. Baca, S. J. Pearton, and C. R. Abernathy, "Effect of temperature on Ga<sub>2</sub>O<sub>3</sub> (Gd<sub>2</sub>O<sub>3</sub>)/GaN metal-oxide-semiconductor-field-effect transistors", *Appl. Phys. Lett.*, 73(26), p. 3893-3895, 1998.

- [4] B. P. Gila, J. W. Johnson, R. Mehandru, B. Luo, A. H. Onstine, K. K. Allums, V. Krishnamoorthy, S. Bates, C. R. Abernathy, F. Ren, and S. J. Pearton, "Gadolinium Oxide and Scandium Oxide: Gate Dielectrics for GaN MOSFETs", *Phys. Stat. Sol. (a)*, 188(1), p. 239-2422001.

- [5] Jihyun Kim, R. Mehandru, B. Luo, and F. Ren, B. P. Gila, A. H. Onstine, C. R. Abernathy, and S. J. Pearton, and Y. Iroawa, "Characteristics of MgO/GaN gate-controlled metal-oxide-semiconductor diodes", *Appl. Phys. Lett.*, 80(24), p. 4555-4557, 1998.

- [6] Yoshitaka Nakano, Tetsu Kachi, and Takashi Jimbo, "Electrical properties of thermally oxidized p-GaN metal-oxide-semiconductor diodes", Appl. Phys. Lett., 82(15), p. 2443-2445, 2003.

- [7] Hyunsoo Kim, Seong-Ju Park, and Hyunsang Hwang, "Thermally oxidized GaN film for use as gate insulators", J. Vac. Sci. Technolo. B, 19(2), p. 579-581, 1999.

- [8] M. E. Lin, B. N. Sverdlov, and H. Morkoç, "Thermal stability of GaN investigated by low-temperature photoluminescence spectroscopy", Appl. Phys. Lett., 63(26), 3625-3627, 1993.

- [9] C. B. Vartuli, S. J. Pearton, C. R. Abernathy, J. D. MacKenzie, E. S. Lambers, and J. C. Zolper, "High temperature surface degradation of III-V nitrides", *J. Vac. Sci. Technol. B*, 14(6), p. 3523-3531, 1996.

- [10] R. Groh, G. Gerey, L. Bartha, and J. I. Pankove, "On the thermal decomposition of GaN in vacuum", *Physica (a)*, 26(1), p. 353-357, 1974.

- [11] Kevin Matocha, Ronald J. Gutmann, and T. Paul Chow, "Effect of Annealing on GaN-Insulator Interfaces Characterized by Metal-Insulator-Semiconductor Capacitors", *IEEE Trans. On Electron Devices*, 50(5), p. 1200-1204, May 2003.

- 12] S. D. Wolter, S. E. Mohney, and H. Venugopalan, "Kinetic Study of the Ocidation of Gallium Nitride in Dry Air", J. Electrochem. Soc., 145(2), p. 629-632, 1998.

- [13] E. D. Radinger, S. D. Wolter, D. L. Waltemyer, J. M. Delucca, S. E. Mohner, B. I. Prenitzer, L. A. Giannuzzi, and R. J. Molnar, "Wet Thermal Oxidation of GaN", *Journal of Electronic Materials*, 28(3), p. 257-260, 1999.

- [14] W. A. Hill and C. C. Coleman, "A Single-frequency Approximation For Interface-State Density Determination", Solid-State Electronics, 23(9), 1980, 987-993.