# Influence of Si Nanocrystal Distributed in the Gate Oxide on the MOS Capacitance

C. Y. Ng, Student Member, IEEE, T. P. Chen, Member, IEEE, L. Ding, M. Yang, Student Member, IEEE, J. I. Wong, P. Zhao, X. H. Yang, K. Y. Liu, M. S. Tse, A. D. Trigg, Member, IEEE, and S. Fung

Abstract—In this paper, the authors have studied the influence of silicon nanocrystal (nc-Si) distributed in the gate oxide on the capacitance for the circumstances that the nc-Si does not form conductive percolation tunneling paths connecting the gate to the substrate. The nc-Si is synthesized by Si-ion implantation. The effective dielectric constant of the gate oxide in the nc-Si distributed region is calculated based on a sublayer model of the nc-Si distribution and the Maxwell-Garnett effective medium approximation. After the depth distribution of the effective dielectric constant is obtained, the MOS capacitance is determined. Two different nc-Si distributions, i.e., partial and full nc-Si distributions in the gate oxide, have been considered. The MOS capacitance obtained from the modeling has been compared to the capacitance measurement for a number of samples with various gate-oxide thicknesses, implantation energies and dosages, and an excellent agreement has been achieved for all the samples. A detailed picture of the influence of implantation energy and implantation dosage on the MOS capacitance has been obtained.

Index Terms—Dielectric constant, MOS capacitance, silicon nanocrystal.

# I. INTRODUCTION

RESEARCH on silicon nanocrystals (nc-Si) embedded in the gate oxide of a MOS structure has been carried out intensively over the past decade due to the potential applications of nc-Si in memory device applications [1]–[12]. One of the promising techniques to incorporate nc-Si into SiO<sub>2</sub> is Si-ion implantation followed by high-temperature annealing. With this technique, the fabrication is fully compatible with the mainstream CMOS process, and the distribution of nc-Si in the gate oxide can be easily controlled. When the nc-Si is embedded in the SiO<sub>2</sub> film, the dielectric constant of the film will be different from that of pure SiO<sub>2</sub> film. Therefore, for memory devices with the nc-Si embedded in the gate oxide, the inclusion of the nc-Si will definitely affect the MOS capacitance as a result of the change in the dielectric

Manuscript received October 21, 2005. This work was supported by the Ministry of Education Singapore under Project ARC 1/04 and also by the Singapore Millennium Foundation. The review of this paper was arranged by Editor R. Shrivastava.

- C. Y. Ng, T. P. Chen, L. Ding, M. Yang, J. I. Wong, P. Zhao, X. H. Yang, K. Y. Liu, and M. S. Tse are with the School of Electrical and Electronic Engineering, Nanyang Technological University, Singapore 639798 (e-mail: echentp@ntu.edu.sg).

- A. D. Trigg is with the Institute of Microelectronics, Singapore 117685.

- S. Fung is with the Physics Department, The University of Hong Kong,

Digital Object Identifier 10.1109/TED.2006.870872

constant of the gate oxide. The effect of the nc-Si on the MOS capacitance has been observed experimentally [13]. The change in the MOS capacitance due to the influence of the nc-Si will then affect the electrical characteristics of the device. Obviously, a precise knowledge on the influence of the nc-Si on the MOS capacitance is very useful to the design and modeling of the memory devices. In particular, an approach to calculate the MOS capacitance, with the nc-Si distribution in the gate oxide taken into account, is highly desirable. However, a quantitative study on the influence of nc-Si on the MOS capacitance is still lacking.

In the present paper, we have developed an approach to the calculation of the MOS capacitance for any nc-Si distribution in the gate oxide, for the circumstances that the nc-Si does not form conductive percolation tunneling paths connecting the gate to the substrate. The approach is based on the calculation of the effective dielectric constant of the gate oxide in the nc-Si distributed region with a sublayer model of nc-Si distribution and the Maxwell–Garnett effective medium approximation (EMA). The MOS capacitance calculated using this approach has been compared to the capacitance measurement for a number of samples with various gate-oxide thicknesses, implantation energies and dosages, and an excellent agreement has been achieved for all the samples. A detailed picture of the influence of implantation energy and implantation dosage on the MOS capacitance has been obtained.

### II. MODELING

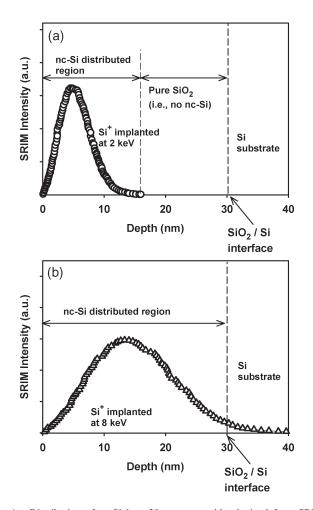

The distribution of the nc-Si in the gate oxide can be obtained from the stopping and range of ions in matter (SRIM) simulation. There are two cases of nc-Si distribution in the gate oxide: partial and full distributions in the gate oxide. For the partial distribution, the oxide can be divided into two regions: the nc-Si distributed region and the pure SiO<sub>2</sub> region (i.e., without nc-Si). One example of the partial distribution, which is achieved with the ion implantation energy of 2 keV for a 30-nm gate oxide, is shown in Fig. 1(a). For the full distribution, nc-Si is distributed in the entire gate oxide. Note that for the full distribution, the nc-Si concentration should not be too high to avoid the formation of conductive percolation tunneling paths connecting the gate to the substrate. Fig. 1(b) shows one example of the full distribution achieved with the ion implantation energy of 8 keV for a 30-nm gate oxide. The SRIM simulation shows that for a 30-nm gate oxide, the full distribution can be achieved with implantation energy higher than 7 keV.

Fig. 1. Distribution of nc-Si in a 30-nm gate oxide obtained from SRIM simulation. (a) Partial distribution under the ion implantation energy of 2 keV. (b) Full distribution under the implantation energy of 8 keV.

From the nc-Si SRIM profile, we can obtain the depth distribution of the nc-Si volume fraction in the  $SiO_2$ . The volume fraction can be expressed as

$$v(x) = \frac{QI(x)}{N_{\rm Si} \int_0^{d_{\rm max}} I(x) dx} \tag{1}$$

where Q is the dosage of implanted Si ions,  $N_{\rm Si}$  is the silicon density,  $d_{\rm max}$  is the maximum depth of the Si-implantation profile, i.e., the width of the nc-Si distributed region. Note that  $d_{\rm max}$  is equal to the gate-oxide thickness for the case of full distribution, and I(x) is the Si SRIM intensity. The information of the volume fraction is required for the calculation of the effective dielectric constant of SiO $_2$  containing nc-Si, as discussed below.

As the nc-Si volume fraction varies with the depth in the oxide, the effective dielectric constant of the oxide is not uniform and should vary with the depth also. The nc-Si distributed region [note that its width is equal to  $d_{\rm max}$  of (1)] can be virtually divided into  $m~(m=30,40,~{\rm and}~100~{\rm for}~30,40,~{\rm and}~100~{\rm nm}$  of SiO $_2$  thickness, respectively, in the present study) sublayers with equal thickness of  $(d_{\rm max}/m)$  nm (namely: sublayer 1, sublayer 2,..., sublayer m) starting from the surface to the depth of  $d_{\rm max}$ . The nc-Si volume fraction within a sublayer is

approximately constant. Thus, the effective dielectric constant  $\varepsilon_i$   $(i=1,2,\ldots,m)$  of the ith sublayer can be calculated with the Maxwell–Garnett EMA, as given by [14]

$$\frac{\varepsilon_i - \varepsilon_{\text{SiO}_2}}{\varepsilon_i + 2\varepsilon_{\text{SiO}_2}} = v_i \frac{\varepsilon_{\text{nc-Si}} - \varepsilon_{\text{SiO}_2}}{\varepsilon_{\text{nc-Si}} + 2\varepsilon_{\text{SiO}_2}}$$

(2)

where  $v_i$   $(i=1,2,\ldots,m)$  is the volume fraction of the nc-Si in the ith sublayer,  $\varepsilon_{\rm nc-Si}$  is the static dielectric constant of nc-Si, and  $\varepsilon_{\rm SiO_2}$  is the dielectric constant of pure SiO<sub>2</sub>.

The screening dielectric constant of nc-Si can be theoretically calculated with the formula below [15]

$$\varepsilon_{\text{nc-Si}}(D) = 1 + \frac{\varepsilon_b - 1}{1 + \left(\frac{1.38}{D}\right)^{1.37}}$$

(3)

where  $\varepsilon_b$  is the dielectric constant of bulk crystalline silicon (note that in [15], the two constants 1.37 and 1.38 used in (3) are obtained under the assumption of  $\varepsilon_b=11.4$ ). This  $\varepsilon_b$  value is slightly different from the widely used value 11.9 [16], and D is the diameter of nc-Si in the unit of nanometer. As discussed later, the mean nc-Si size is 4.5 nm as determined from the X-ray diffraction (XRD) measurement. The  $\varepsilon_{\rm nc-Si}$  calculated with (3) is 9.7 under the assumption of D=4.5 nm. This  $\varepsilon_{\rm nc-Si}$  value is consistent with that from the optical study reported in [17]. Most importantly, the calculated MOS capacitance based on this  $\varepsilon_{\rm nc-Si}$  value is in excellent agreement with the measured capacitance, indicating that the  $\varepsilon_{\rm nc-Si}$  value is correct. The details will be discussed later.

After determining the dielectric constant of the nc-Si, the effective dielectric constant  $\varepsilon_i$   $(i=1,2,\ldots,m)$  of each sublayer of the nc-Si distributed region can be calculated with (2). With the depth distribution of the effective dielectric constant taken into account, the MOS capacitance in the accumulation regime is calculated, as described below. For the case of partial nc-Si distribution in the gate oxide, the MOS capacitance (C) per unit area can be expressed as

$$\frac{1}{C} = \sum_{i=1}^{m} \left[ \frac{m\varepsilon_i \varepsilon_0}{d_{\text{max}}} \right]^{-1} + \left[ \frac{3.9 \times \varepsilon_0}{T_{\text{oxide}} - d_{\text{max}}} \right]^{-1} \tag{4}$$

where  $T_{\rm oxide}$  is the gate-oxide thickness, and  $\varepsilon_0$  is the permittivity in vacuum. On the other hand, for the case of full nc-Si distribution in the gate oxide, the MOS capacitance is given by

$$\frac{1}{C} = \sum_{i=1}^{m} \left[ \frac{m\varepsilon_i \varepsilon_0}{T_{\text{oxide}}} \right]^{-1}.$$

(5)

It should be pointed out that the above calculations of the MOS capacitance [i.e., (4) and (5)] are valid only for the circumstances that the nanocrystals themselves are not charged and discharged in response to the small ac signal applied during a capacitance measurement. If there is a high concentration of nanocrystals distributed throughout the gate oxide, these nanocrystals can form conductive percolation tunneling paths

Fig. 2. TEM image of nc-Si embedded in a 30-nm gate oxide. (a) Partial distribution under the implantation energy of 2 keV. (b) Full distribution under the implantation energy of 10 keV.

connecting the substrate to the gate [18]. Thus, they can be charged and discharged easily under the influence of the ac signal. In this case, the nanocrystal acts like a capacitor and, therefore, the MOS capacitance should be calculated based on an equivalent circuit that takes the contribution of the nanocrystal capacitance into account [18].

# III. EXPERIMENTAL

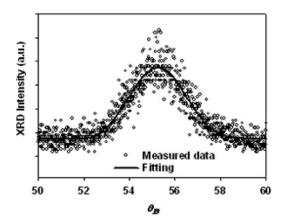

The gate oxide was thermally grown to 30, 40, and 100 nm, respectively, on p-type (100) Si wafers in dry oxygen at 950 °C.  $\mathrm{Si}^+$  ions with a dosage ranging from  $3 \times 10^{14}$  to  $8 \times 10^{16}$  cm<sup>-2</sup> were then implanted to the gate oxide at various implantation energies from 2 to 28 keV. Thermal annealing was carried out at 1000 °C in N<sub>2</sub> ambient for 1 h to induce nc-Si formation for all samples. Fig. 2 shows the cross-sectional transmission electron microscopy (TEM) images of nc-Si embedded in the gate oxide for both partial nc-Si distribution [Fig. 2(a)] and full nc-Si distribution [Fig. 2(b)]. For both cases, from the TEM measurement, the nc-Si size is found to be  $\sim 4 - \sim 5$  nm for all the samples used in the present study. The average size of nc-Si can also be determined from the full width of half maximum (FWHM) of the Bragg peak after correction for instrumental broadening in the XRD measurement [14], [19]. Fig. 3 shows an example of the XRD measurement. The mean size of the nc-Si obtained from the XRD measurement is  $4.5 \pm 0.3$  nm for all the samples, and it is found to be insensitive to the annealing temperature/time. For the capacitance measurement, aluminum was deposited and patterned to form the top and bottom electrodes. Capacitance-voltage (C-V) measurement was performed at the frequency of 1 MHz with an HP4284A LCR meter.

Fig. 3. Example of XRD measurement of nc-Si embedded in the gate oxide. The gate-oxide thickness and the implantation energy of the sample used in this measurement are 30 nm and 2 keV, respectively.

### IV. RESULTS AND DISCUSSIONS

To verify the above modeling approach and to check the correctness of the  $\varepsilon_{\rm nc-Si}$  (= 9.7, which corresponds to the nc-Si size of 4.5 nm) value, MOS capacitance measurement under a strong accumulation has been carried out on many samples with various gate-oxide thicknesses, implantation energies, and dosages. Table I summarizes the comparison between the measured capacitance and the capacitance calculated using  $\varepsilon_{\rm nc-Si} = 9.7$ , with (4) for the partial distribution or (5) for the full distribution. The agreement between the measurement and the calculation can be easily described by the ratio R =calculated capacitance/measured capacitance. As can be seen in the table, the R value is very close to one (in the range from 0.982 to 1.002) for all the samples. This indicates that the calculation is in excellent agreement with the measurement. On the other hand, we have also compared the measured capacitance with the capacitances calculated with  $\varepsilon_{\rm nc-Si} = 9.7$ and  $\varepsilon_{\rm nc-Si} = 11.9$  (the value of the bulk crystalline silicon) for various implantation energies, as shown in Fig. 4. It is evident from Fig. 4 that  $\varepsilon_{\rm nc-Si}=9.7$  can yield an excellent agreement between the calculation and the measurement while such an agreement cannot be achieved with  $\varepsilon_{\rm nc-Si} = 11.9$ . Therefore, it can be concluded that both the above modeling approach and the  $\varepsilon_{\rm nc-Si}$  (= 9.7) value are reliable and accurate.

Fig. 4 also shows the influence of implantation energy on the MOS capacitance. The capacitance is calculated at various implantation energies ranging from 1 to 11 keV for the fixed implantation dosage of  $1 \times 10^{16}$  cm<sup>-2</sup> and the gate-oxide thickness of 30 nm. According to the SRIM output, for a 30-nm gate oxide, the partial distribution corresponds to the implantation energies lower than 7 keV, while the full distribution is achieved with implantation energies higher than 7 keV. For the partial distribution, as the implantation energy increases, the width  $(d_{\text{max}})$  of the nc-Si distributed region increases, but the effective dielectric constant  $\varepsilon_i$  (i = 1, 2, ..., m) decreases as the nc-Si volume fraction  $(v_i)$  decreases when  $d_{\mathrm{max}}$  increases for a constant implantation dosage. Thus, the overall effect of implantation energy on the MOS capacitance for the partial distribution is that the MOS capacitance first decreases with the implantation energy and then it

| TABLE I                                                                                                |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| COMPARISON BETWEEN THE MEASURED AND CALCULATED MOS CAPACITANCE FOR VARIOUS SAMPLES. THE CALCULATION IS |  |  |  |  |  |

| Based on (4) for the Partial Distribution or (5) for the Full Distribution                             |  |  |  |  |  |

| nc-Si<br>distribution | SiO <sub>2</sub> thickness (nm) | Implantation energy (keV) | Dosage<br>(cm <sup>-2</sup> ) | Measured capacitance (F/m²) | Calculated capacitance $(\epsilon_{nc}=9.7)$ $(F/m^2)$ | $R = \frac{\text{calculated cap.}}{\text{measured cap.}}$ |

|-----------------------|---------------------------------|---------------------------|-------------------------------|-----------------------------|--------------------------------------------------------|-----------------------------------------------------------|

| Partial distribution  | 30                              | 2                         | 1×10 <sup>16</sup>            | 1.209×10 <sup>-3</sup>      | 1.209×10 <sup>-3</sup>                                 | 1.000                                                     |

|                       | 30                              | 5                         | 1×10 <sup>16</sup>            | 1.211×10 <sup>-3</sup>      | 1.211×10 <sup>-3</sup>                                 | 1.000                                                     |

|                       | 100                             | 28                        | 8×10 <sup>16</sup>            | 3.907×10 <sup>-4</sup>      | 3.913×10 <sup>-4</sup>                                 | 1.002                                                     |

| Full<br>distribution  | 30                              | 8                         | 3×10 <sup>14</sup>            | 1.153×10 <sup>-3</sup>      | 1.153×10 <sup>-3</sup>                                 | 1.000                                                     |

|                       | 30                              | 8                         | 2×10 <sup>15</sup>            | 1.169×10 <sup>-3</sup>      | 1.163×10 <sup>-3</sup>                                 | 0.995                                                     |

|                       | 30                              | 8                         | 1×10 <sup>16</sup>            | 1.209×10 <sup>-3</sup>      | 1.21×10 <sup>-3</sup>                                  | 1.001                                                     |

|                       | 30                              | 10                        | 3×10 <sup>16</sup>            | 1.335×10 <sup>-3</sup>      | 1.328×10 <sup>-3</sup>                                 | 0.995                                                     |

|                       | 40                              | 18                        | 5×10 <sup>16</sup>            | 1.033×10 <sup>-3</sup>      | 1.014×10 <sup>-3</sup>                                 | 0.982                                                     |

12.8

SiO<sub>2</sub> = 30 nm, Si<sup>+</sup> energy = 8 keV

Simulation

Measurement

11.6

11.4

10<sup>14</sup>

10<sup>15</sup>

Si<sup>+</sup> dosage (cm<sup>-2</sup>)

Fig. 4. Influence of Si $^+$  implantation energy on the MOS capacitance. The gate-oxide thickness is 30 nm, and the implantation dosage is  $1\times10^{16}~cm^{-2}$ .

Fig. 5. Influence of Si<sup>+</sup> dosage on the MOS capacitance. The gate-oxide thickness is 30 nm, and the implantation energy is 8 keV.

increases slowly when the energy is larger than  $\sim 2$  keV, as shown in Fig. 4. For the full distribution, when the implantation energy is larger than 7 keV, some of the Si ions are implanted into the Si substrate and, thus, the effective dielectric constant  $\varepsilon_i$   $(i=1,2,\ldots,m)$  decreases as the nc-Si volume fraction  $(v_i)$  decreases with the implantation energy. Therefore, as given by (5), the MOS capacitance decreases with the implantation energy. Such a picture is also shown in Fig. 4.

Fig. 5 shows the MOS capacitance calculated with (5) as a function of the implantation dosage. The gate-oxide thickness is 30 nm, the implantation energy is fixed at 8 keV, which corresponds to the full distribution, and the  $\varepsilon_{\rm nc-Si}$  value used is 9.7. For comparison, the measured MOS capacitances for the implantation dosages of  $3\times 10^{14},\ 2\times 10^{15},\ {\rm and}\ 1\times 10^{16}\ {\rm cm}^{-2}$  are also included in Fig. 5. As can be seen in the figure, there is a good agreement between the calculation and the measurement. Fig. 5 shows that the MOS capacitance increases with the implantation dosage, and the increase becomes significant when the dosage is higher than  $\sim 3\times 10^{14}\ {\rm cm}^{-2}$ . The increase of the MOS capacitance is due to the increase of the effective

dielectric constant as a result of the increase in the nc-Si volume fraction with the dosage.

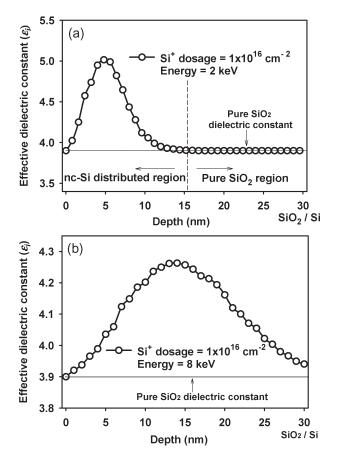

It has been clear from the above discussions that the increase in the MOS capacitance is actually due to the increase in the effective dielectric constant of the gate oxide as a result of the introduction of the nc-Si into the gate oxide. As the nc-Si volume fraction is a function of the depth, the effective dielectric constant also varies with the depth. We have calculated the depth distribution of the effective dielectric constant in the gate oxide based on (2). Fig. 6 shows the effective dielectric constant as a function of the depth in a 30-nm gate oxide for the partial distribution [Fig. 6(a)] and the full distribution [Fig. 6(b)]. For the case of partial distribution, the sample was implanted with  $1 \times 10^{16} \text{ cm}^{-2}$  of Si<sup>+</sup> at 2 keV. There is a large increment of 1.12 in the effective dielectric constant at the peak position of the nc-Si distribution as compared to the dielectric constant of pure SiO<sub>2</sub>. The effective dielectric constant is the same as the dielectric constant (3.9) of pure SiO<sub>2</sub> when the depth is larger than  $\sim 15$  nm as there is no nc-Si in the region. For the case of full distribution, the sample was implanted with  $1 \times 10^{16} \text{ cm}^{-2}$ of Si<sup>+</sup> at 8 keV. The effective dielectric constant at the peak

Fig. 6. Depth distribution of the effective dielectric constant of the gate oxide. (a) Partial distribution under the implantation energy of 2 keV. (b) Full distribution under the implantation energy of 8 keV. For both cases, the gate-oxide thickness is 30 nm, and the implantation dosage is  $1 \times 10^{16}$  cm<sup>-2</sup>.

position of the nc-Si distribution is larger than the dielectric constant of pure  $\mathrm{SiO}_2$  by 0.36. For both the partial and full distributions, the depth distribution of the effective dielectric constant follows the nc-Si distribution approximately.

# V. CONCLUSION

In this paper, nc-Si embedded in the gate oxide is synthesized by Si-ion implantation. The influence of nc-Si distribution in the gate oxide on the MOS capacitance has been investigated through modeling and experiment for the circumstances that the nc-Si does not form conductive percolation tunneling paths connecting the gate to the substrate. The nc-Si volume fraction as a function of the depth in the gate oxide is calculated from the SRIM simulation. With the nc-Si volume fraction obtained, the effective dielectric constant of the gate oxide in the nc-Si distributed region can be calculated based on a sublayer model and the Maxwell-Garnett EMA. After the depth distribution of the effective dielectric constant is obtained, the MOS capacitance is determined. Two different nc-Si distributions, i.e., partial and full nc-Si distributions in the gate oxide, have been considered. MOS capacitance measurement has been carried out on many samples with various gate-oxide thicknesses, implantation energies, and dosages to verify the modeling of the MOS capacitance. An excellent agreement between the measurement and the modeling has been achieved. A detailed picture of the influence of the implantation energy and the implantation dosage on the MOS capacitance has been obtained. In addition, the depth distribution of the effective dielectric constant of the gate oxide is also determined for the two nc-Si distributions.

## REFERENCES

- S. Tiwari, F. Rana, K. Chan, H. Hanafi, W. Chan, and D. Buchanan, "Volatile and non-volatile memories in silicon with nano-crystal storage," in *IEDM Tech. Dig.*, Washington, DC, 1995, pp. 521–524.

- [2] S. Tiwari, F. Rana, H. Hanafi, A. Hartstein, E. F. Crabbe, and K. Chan, "A silicon nanocrystals based memory," *Appl. Phys. Lett.*, vol. 68, no. 10, pp. 1377–1379, Mar. 1996.

- [3] G. Ammendola, V. Ancarani, V. Triolo, M. Bileci, D. Corso, I. Crupi, L. Perniola, C. Gerardi, S. Lombardo, and B. DeSalvo, "Nanocrystal memories for FLASH device applications," *Solid State Electron.*, vol. 48, no. 9, pp. 1483–1488, Sep. 2004.

- [4] F. Yun, B. J. Hinds, S. Hatatani, and S. Oda, "Room temperature single-electron narrow-channel memory with silicon nanodots embedded in SiO<sub>2</sub> matrix," *Jpn. J. Appl. Phys. 2, Lett.*, vol. 39, no. 8A, pp. L792–L795, Aug. 2000.

- [5] I. Kim, S. Han, K. Han, K. Lee, and H. Shin, "Si nanocrystal memory cell with room-temperature single electron effects," *Jpn. J. Appl. Phys. 1, Regul. Rap. Short Notes*, vol. 40, no. 2A, pp. 447–451, Feb. 2001.

- [6] T. Gebel, J. von Borany, H.-J. Thees, M. Wittmaack, K.-H. Stegemann, and W. Skorupa, "Non-volatile memories based on Si<sup>+</sup>-implanted gate oxides," *Microelectron. Eng.*, vol. 59, no. 1, pp. 247–252, Nov. 2001.

- [7] C. Y. Ng, T. P. Chen, H. W. Lau, Y. Liu, M. S. Tse, O. K. Tan, and V. S. W. Lim, "Visualizing charge transport in silicon nanocrystals embedded in SiO<sub>2</sub> films with electrostatic force microscopy," *Appl. Phys. Lett.*, vol. 85, no. 14, pp. 2941–2943, Oct. 2004.

- [8] C. Y. Ng, T. P. Chen, Y. Liu, M. S. Tse, and D. Gui, "Modulation of capacitance magnitude by charging/discharging in silicon nanocrystals distributed throughout the gate oxide in MOS structures," *Electrochem. Solid-State Lett.*, vol. 8, no. 1, pp. G8–G10, 2005.

- [9] Y. Shi, K. Saito, H. Ishikuro, and T. Hiramoto, "Effects of interface traps on charge retention characteristics in silicon-quantum-dot-based metaloxide-semiconductor diodes," *Jpn. J. Appl. Phys. 1, Regul. Rap. Short Notes*, vol. 38, no. 1B, pp. 425–428, Jan. 1999.

- [10] Y. Liu, T. P. Chen, C. Y. Ng, M. S. Tse, P. Zhao, Y. Q. Fu, S. Zhang, and S. Fung, "Random capacitance modulation due to charging/discharging in Si nanocrystals embedded in gate dielectric," *Nanotechnol.*, vol. 16, no. 8, pp. 1119–1122, Aug. 2005.

- [11] S. Lombardo, B. De Salvo, C. Gerardi, and T. Baron, "Silicon nanocrystal memories," *Microlectron. Eng.*, vol. 72, no. 1–4, pp. 388–394, Apr. 2004.

- [12] P. Dimitrakis, E. Kapetanakis, D. Tsoukalas, D. Skarlatos, C. Bonafos, G. B. Asssayag, A. Claverie, M. Perego, M. Fanciulli, V. Soncini, R. Sotgiu, A. Agarwal, M. Ameen, C. Sohl, and P. Normand, "Silicon nanocrystal memory devices obtained by ultra-low-energy ion-beam synthesis," *Solid State Electron.*, vol. 48, no. 9, pp. 1511–1517, Sep. 2004.

- [13] C. Y. Ng, T. P. Chen, and M. S. Tse, "Electrical characteristics of ion-beam synthesized Si nanocrystals in SiO<sub>2</sub> matrix," in *Proc. Int. Symp. Integrated Circuits, Devices and Systems (ISIC)*, Singapore, 2004, pp. 281–283.

- [14] T. P. Chen, Y. Liu, M. S. Tse, O. K. Tan, P. F. Ho, K. Y. Liu, D. Gui, and A. L. K. Tan, "Dielectric functions of Si nanocrystals embedded in a SiO<sub>2</sub> matrix," *Phys. Rev. B, Condens. Matter*, vol. 68, no. 15, pp. 153301–153304, Oct. 2003.

- [15] L. W. Wang and A. Zunger, "Dielectric constants of silicon quantum dots," *Phys. Rev. Lett.*, vol. 73, no. 7, pp. 1039–1042, Aug. 1994.

- [16] S. M. Sze, Physics of Semiconductor Devices, 2nd ed. New York: Wiley, 1981.

- [17] L. Ding, T. P. Chen, Y. Liu, C. Y. Ng, Y. C. Liu, and S. Fung, "Thermal annealing effect on the bandgap and dielectric functions of silicon nanocrystals embedded in SiO<sub>2</sub> matrix," *Appl. Phys. Lett.*, vol. 87, no. 12, pp. 121903-1–121903-3, Sep. 2005.

- [18] C. Y. Ng, Y. Liu, T. P. Chen, and M. S. Tse, "Charging/discharging of silicon nanocrystals embedded in an SiO<sub>2</sub> matrix inducing reduction/recovery in the total capacitance and tunneling current," *Smart Mater. Struct.*, vol. 15, no. 1, pp. S43–S46, Feb. 2006.

- [19] R. Govindaraj, R. Kesavamoorthy, R. Mythili, and B. Viswanathan, "The formation and characterization of silver clusters in zirconia," *J. Appl. Phys.*, vol. 90, no. 2, pp. 958–963, Jul. 2001.

**C. Y. Ng** (S'03) was born in Penang, Malaysia, in 1979. He received the B.Eng. degree in electrical and electronics from the University Technology of Malaysia, Johor, Malaysia, in 2002. He is currently working toward the Ph.D. degree in microelectronics at the Nanyang Technological University, Singapore.

From July 2002 to February 2003, he was a Test Product Engineer at Advance Semiconductor Engineering (ASE) Malaysia. He has authored or coauthored more than 15 international peer-reviewed journal papers and 12 conference papers. His re-

search interests include physical properties and device applications based on semiconductor nanocrystal, coulomb blockade effect, and single-electron tunneling in silicon nanocrystal.

Mr. Ng was the recipient of Nanyang Postgraduate Scholarship from 2003 to 2005 and The Singapore Millennium Foundation (SMF) Ph.D. scholarship from 2005 onwards (up to three years).

**J. I. Wong** was born in Johor Baru, Malaysia, on February 28, 1982. He received the B.Eng. degree in electrical and electronic engineering from the Nanyang Technological University, Singapore, in 2005. He is currently working toward the Ph.D. degree in electrical and electronic engineering at the same university.

His research interest focuses on the studies of semiconductor nanocrystals.

T. P. Chen (M'98) was born in China in 1964. He received the B.Sc. and M.Sc. degrees in physics, in which he focused on semiconductors and devices, from Zhongshan (Sun Yat-Sen) University, Guangzhou, China, in 1983 and 1987, and the Ph.D. degree in semiconductor physics from The University of Hong Kong, Hong Kong, in 1994.

From 1990 to 1991, he was a Visiting Scientist at the Fritz-Haber Institute of The Max-Planck Society, Germany. From 1994 to 1997, he was a Postdoctoral Fellow at the University of Hong Kong

and the National University of Singapore. He also served two and half years for PSB Singapore as a Senior Scientist before he joined Nanyang Technological University, in February 2000. His current research interests include nanoscale CMOS devices and reliability physics, semiconductor nanocrystals and their applications in memory devices and photonic/optoelectronic devices, and molecular devices. He is currently an Associate Professor in the Division of Microelectronics, School of Electrical and Electronic Engineering, Nanyang Technological University, Singapore. He has authored or coauthored more than 100 international peer-reviewed journal papers and 50 conference papers.

P. Zhao was born in China in 1976. He received the B.S. degree in physics from Hebei Normal University, China, in 1995 and the M.S. degree in physics from Jilin University, China, in 1999. He is currently working toward the Ph.D. degree in electrical and electronic at Nanyang Technological University, Singapore.

His research interests include fabrication and characterization of SiC MOS fieldeffect devices, as well as advanced CMOS reliability physics and modeling.

**X. H. Yang**, photograph and biography not available at the time of publication.

L. Ding was born in China in 1982. He received the B.Sc degree in physics, in which he focused on optical and optoelectronic physics, from Huazhong University of Science and Technology, Hubei, China, in 2004. He is currently working toward the Ph.D. degree, focusing on optical and optoelectronic properties of nc-Si and its applications, from Nanyang Technological University, Singapore.

**K. Y. Liu** was born in China in 1968. He received the B.Sc. degree in semiconductor device and physics from the Southeast University, Nanjing, China, in 1991 and the M.Eng degree in microelectronics from Nanyang Technological University (NTU), Singapore, in 2000.

He joined the Institute of Semiconductors, Chinese Academy of Sciences in 1991 as a Device and Process Engineer working on silicon-on-insulator (SOI) devices and their application. Since 1999, he was with the School of Electrical and Electronic

Engineering, NTU. His major research interests include MOS device characterization and reliability, process integration, novel wafer fabrication technology, and microelectromechanical system technology.

M. Yang (S'06) was born in Xiamen, China, in June 17, 1982. He received the B.Eng. degree in microelectronics (first class honors) from Nanyang Technological University (NTU), Singapore, in 2005. Currently, he is working toward the Ph.D. degree in NTU, in which his work focuses on optical and electrical properties of semiconductor nanocrystals embedded in gate oxide of MOS structure.

Mr. Yang was awarded a full scholarship to study in Singapore in 2000.

M. S. Tse, photograph and biography not available at the time of publication.

**A. D. Trigg** (M'97) received the B.Sc. degree from Exeter University, Exeter, U.K., in 1972 and the Ph.D. degree from London University, London, U.K., in 1978.

From 1987 to 1990, he was a Deputy Director of the Research Initiative on Silicon Hybrids (MCMs) and, subsequently, became a Project Leader for manufacture of high-stability oscillators for space applications. From 1975 to 1995, he worked for the Hirst Research Centre of the GEC Marconi, U.K. In 1995, he joined the Institute of Microelectronics,

Singapore, where he worked on infrared photoemission microscopy, surface analysis, failure analysis, and the development of MCMs.

Dr. Trigg is currently General Chair of the 13th International Symposium on the Physical and Failure Analysis of Integrated Circuits (IPFA 2006).

**S. Fung** was born in Hong Kong, in 1950. He received the B.A. degree in physics (first class honors), the Ph.D. degree in semiconductor physics, and the D.Sc. degree from The University of Oxford, Oxford, U.K., in 1977, 1980, and 1996, respectively.

He is currently a Professor at the Department of Physics, The University of Hong Kong, Hong Kong. His major research interests are nanomaterials, widebandgap semiconductors, and positron physics.

Dr. Fung is a Fellow of the Institute of Physics, U.K.