## Static dielectric constant of isolated silicon nanocrystals embedded in a SiO<sub>2</sub> thin film

C. Y. Ng, T. P. Chen, a) L. Ding, Y. Liu, and M. S. Tse School of Electrical and Electronic Engineering, Nanyang Technological University, Singapore 639798

## S. Fung

Department of Physics, The University of Hong Kong, Hong Kong, People's Republic of China

## Z. L. Dong

School of Material Sciences and Engineering, Nanyang Technological University, Singapore 639798

(Received 18 August 2005; accepted 16 December 2005; published online 6 February 2006)

The static dielectric constant of isolated silicon nanocrystals (nc-Si) embedded in a SiO<sub>2</sub> thin film synthesized by Si<sup>+</sup> implantation has been determined from capacitance measurement based on the Maxwell–Garnett effective medium approximation and the stopping and range of ions in matter simulation. For the nc-Si with a mean size of  $\sim$ 4.5 nm, the dielectric constant so determined is 9.8, being consistent with a theoretical prediction. This value is significantly lower than the static dielectric constant (11.9) of bulk crystalline Si, indicating the significance of nc-Si size effect. The information of nc-Si dielectric constant is not only important to the fundamental physics but also useful to the design and modeling of nc-Si-based memory devices. © 2006 American Institute of Physics. [DOI: 10.1063/1.2172009]

In recent years, research on silicon nanocrystal (nc-Si) embedded in SiO2 thin film has been carried out intensively due to its potential applications in memory devices as well as optoelectronic devices. <sup>1–5</sup> One promising technique for incorporating nc-Si into SiO2 is to use Si ion implantation followed by high temperature annealing. With this technique the nc-Si synthesis is fully compatible with the mainstream complementary metal-oxide-semiconductor (MOS) process and the distribution of the nc-Si can easily be controlled. When the nc-Si is embedded in the SiO<sub>2</sub> film, the dielectric properties of the film will be different from that of the pure  $SiO_2$  film. Therefore, for flash memory devices with the nc-Si embedded in the gate oxide,  $^{4,6,7}$  the inclusion of the nc-Si will definitely affect the gate capacitance. However, a quantitative study on the influence of the nc-Si on the gate capacitance is still lacking, although it is very important to the design and modeling of the memory devices. On the other hand, as the nc-Si is an isolated nanoscale structure with a size of less than  $\sim$ 5 nm embedded in the SiO<sub>2</sub> matrix, its physical properties should be different from that of bulk crystalline Si. Thus understanding the dielectric properties of the nc-Si is undoubtedly important to the fundamental physics. In addition, if the dielectric properties of the nc-Si are known, the dielectric properties of a SiO<sub>2</sub> thin film containing the nc-Si can also be obtained based on an appropriate effective medium approximation (EMA), and the information is useful to the device applications of the nc-Si. In this work, we have determined the static dielectric constant of isolated nc-Si embedded in a SiO2 thin film synthesized with the technique of Si ion implantation.

The SiO<sub>2</sub> films were thermally grown to a thickness of 100 nm on n-type (100) oriented Si wafers in dry oxygen at 950 °C. Si<sup>+</sup> ions with a dose of  $8 \times 10^{16}$  cm<sup>-2</sup> were then implanted to the SiO<sub>2</sub> thin films at the energy of 28 keV. Thermal annealing was subsequently carried out at 1000 °C

in  $N_2$  ambient for 1 h in order to induce nc-Si formation. Metal-oxide-semiconductor (MOS) capacitors with an area of  $80\times80~\mu\text{m}^2$  are formed by depositing a 20 nm aluminum film onto the SiO<sub>2</sub> thin film. The backsides of wafers were coated with a layer of aluminum with a thickness of about 1  $\mu$ m after removing the backside oxide. Capacitance-voltage (C-V) measurements were performed at a frequency of 1 MHz with a HP4284A LCR meter.

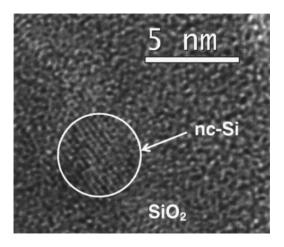

Figure 1 shows the cross-section measurement of the sample using high-resolution transmission electron microscope (TEM) with a Jeol JEM-2010 apparatus. The TEM measurement shows that the size of the nc-Si embedded in the SiO<sub>2</sub> matrix is  $\sim$ 4.5 nm. The nc-Si size can also be determined from the broadening of the Bragg peak in x-ray diffraction (XRD) measurements. The mean size of the nc-Si was determined from the full width at half maximum of the Bragg peak after correction for instrumental broadening in the XRD measurement and was found to be  $\sim$ 4.5 nm, comparable with the size obtained from the TEM measurement.

FIG. 1. High-resolution TEM image of nc-Si embedded in a SiO<sub>2</sub> thin film.

a) Electronic mail: echentp@ntu.edu.sg

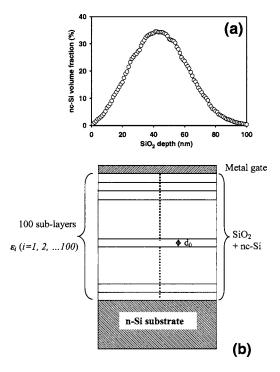

FIG. 2. (a) Depth profile of volume fraction of the nc-Si in the SiO<sub>2</sub> as determined from the SRIM calculation; and (b) the multi-sublayer model used for the EMA calculation.

The profile of excess Si in the 100 nm SiO<sub>2</sub> films due to the Si ion implantation can be obtained from the stopping and range of ions in matter (SRIM)<sup>9</sup> simulation. From the simulation, the peak concentration was found to be at a depth of about 42 nm, and the volume fraction of the peak concentration was calculated to be 34.5%. Figure 2(a) shows the depth distribution of the nc-Si volume fraction. The nc-Si is distributed throughout the oxide from the SiO<sub>2</sub> surface to the SiO<sub>2</sub>/Si interface. As such, the dielectric constant of the oxide film is no longer equal to that (3.9) of pure SiO<sub>2</sub>. Therefore, the MOS capacitance of the structure with nc-Si distributed in the oxide will be different from the capacitance of a MOS capacitor with a pure SiO<sub>2</sub> thin film (i.e., without the nc-Si) of the same thickness.

As the nc-Si volume fraction varies with the depth in the oxide layer, the effective dielectric constant of the oxide layer is not uniform and should vary with the depth. In the present study, the 100 nm oxide layer is virtually divided into 100 sublayers with an equal thickness of  $d_0=1$  nm (namely sublayer 1, sublayer 2, ..., sublayer 100), as shown in Fig. 2(b). The nc-Si volume fraction is considered to be constant within each sublayer. Each sublayer has its own effective dielectric constant,  $\varepsilon_i$  ( $i=1,2,\ldots,100$ ) characterized by the volume fraction  $(v_i)$  of the sublayer. Each sublayer can be schematized as an effective medium, in which the  $SiO_2$  is the host matrix while the nc-Si is an inclusion embedded in the SiO<sub>2</sub> matrix, represented by the Maxwell-Garnett effective medium approximation (EMA)<sup>8,10-14</sup>

$$\frac{\varepsilon_{i} - \varepsilon_{\text{SiO}_{2}}}{\varepsilon_{i} + 2\varepsilon_{\text{SiO}_{2}}} = v_{i} \frac{\varepsilon_{nc-\text{Si}} - \varepsilon_{\text{SiO}_{2}}}{\varepsilon_{nc-\text{Si}} + 2\varepsilon_{\text{SiO}_{2}}},\tag{1}$$

where  $\varepsilon_{SiO_2}$  (=3.9) is the dielectric constant of pure SiO<sub>2</sub> and  $\varepsilon_{nc\text{-Si}}$  is the dielectric constant of the nc-Si. Note that  $\varepsilon_{nc\text{-Si}}$  is a parameter that is to be determined. Taking the depth distribution of the dielectric constant in the oxide layer into ac-

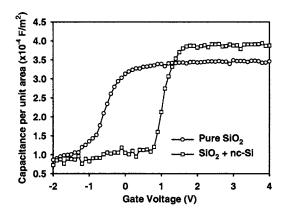

FIG. 3. Comparison of C-V characteristics between the MOS structures with and without the nc-Si embedded in the oxide. Both structures have identical oxide thickness.

count and based on the above sublayer model, the MOS capacitance (C) per unit area can be expressed as

$$\frac{1}{C} = \sum_{i=1}^{100} \left[ \frac{\varepsilon_i \varepsilon_0}{d_0} \right]^{-1},\tag{2}$$

where  $\varepsilon_0$  is the permittivity in vacuum.

One can expect that the dielectric constant of the nc-Si is larger than  $\varepsilon_{SiO_2}$  (=3.9) if the dielectric constant (11.9) of bulk crystalline Ši is taken as a reference. If this is the case,  $\varepsilon_i$  (i=1,2,...,100) should be larger than  $\varepsilon_{SiO_2}$  as predicted by Eq. (1). According to Eq. (2), then the MOS capacitance of the structure with nc-Si distributed in the oxide should be larger than that of the structure without the nc-Si (i.e., a MOS capacitor with a pure SiO<sub>2</sub> thin film of the same thickness). This situation has been observed in the experiment. Figure 3 shows the *C-V* characteristics of the MOS structures with and without the nc-Si distributed in the oxide. As can be seen in this figure, the inclusion of the nc-Si in the oxide leads to a significant increase in the MOS capacitance (i.e., the capacitance under strong accumulation). This indicates that the dielectric constant of the nc-Si is larger than  $\varepsilon_{SiO_2}$ . Besides the increase in the capacitance, Fig. 3 also shows that the inclusion of the nc-Si leads to a flatband voltage shift. The shift is due to the charge trapping in the nc-Si during the C-V measurement and the difference in the work function between the nc-Si and the SiO<sub>2</sub>.

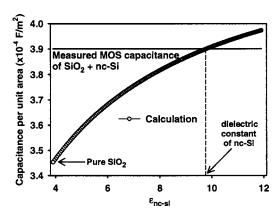

As the volume fraction  $(v_i)$  of nc-Si in each sublayer and  $\varepsilon_{SiO_2}$  are known, the dielectric constant  $(\varepsilon_i)$  of each sublayer can be calculated with Eq. (1) for a given  $\varepsilon_{nc\text{-Si}}$ , and then the MOS capacitance (C) can be calculated with Eq. (2). Figure 4 shows the calculated MOS capacitance as a function of  $\varepsilon_{nc\text{-Si}}$  which varies from 3.9 (dielectric constant of SiO<sub>2</sub>) to 11.9 (dielectric constant of bulk crystalline silicon). As can be seen in this figure, the capacitance increases with the  $\varepsilon_{nc\text{-Si}}$ . From the curve of the capacitance versus the  $\varepsilon_{nc\text{-Si}}$ shown in Fig. 4, one can easily find the value of  $\varepsilon_{nc\text{-Si}}$  corresponding to the measured MOS capacitance of the structure with the nc-Si distributed in the oxide. The value obtained is 9.8, and it is actually the dielectric constant of the nc-Si embedded in the oxide. As expected, the dielectric constant of the nc-Si is much larger than that of pure SiO<sub>2</sub> but significantly smaller than that of bulk crystalline Si.

FIG. 4. MOS capacitance calculated with Eqs. (1) and (2) as a function of  $\varepsilon_{nc\text{-Si}}$ . The intercept between the calculated and the measured capacitance yields the dielectric constant of the nc-Si embedded in the SiO<sub>2</sub>.

According to Wang and Zunger,  $^{15}$  the screening static dielectric constant of the nc-Si as a function of the nc-Si size can be expressed as follows:

$$\varepsilon_{\text{static}}(D) = 1 + \frac{\varepsilon_b - 1}{1 + \left(\frac{1.38}{D}\right)^{1.37}},\tag{3}$$

where  $\varepsilon_b$  is the dielectric constant of bulk crystalline silicon (note that in Ref. 15 the two constants, 1.38 and 1.37, used in Eq. (3) are obtained under the assumption of  $\varepsilon_b$ =11.4. This  $\varepsilon_b$  value is slightly different from the widely used value, 11.9 [Ref. 16] and D is the nc-Si size in the unit of nm. From Eq. (3), in setting the size of nc-Si to be 4.5 nm, the static dielectric constant of nc-Si is found to be 9.7. This number is consistent with the above value of dielectric constant obtained from Fig. 4.

It is obvious from the above discussions that the dielectric constant of nc-Si is significantly reduced from its bulk value. There are a number of studies on the reduction of the dielectric constants of nanoscale systems. 15,17-20 Originally, the reduction in the dielectric constant of small quantum dots (such as the nanocrystal here) was attributed to the band gap increase inside the quantum dots. However, it was only recently argued by Delerue, Lannoo, and Allan that the reduction is due to the breaking of polarizable bonds at the surface and is not due to the opening of the band gap induced by the confinement.<sup>20</sup> This argument is supported by the following two latest studies.<sup>21,22</sup> Based on the first-principle calculation of the microscopic dielectric response function for quantum dots, Cartoix and Wang have found that the reduction of the macroscopic dielectric constants is a surface effect.<sup>21</sup> Giustino and Pasquarello have also shown that for Si slabs of finite size the decrease of the permittivity with slab thickness is related to surface rather than bulk effects.<sup>2</sup>

In conclusion, the static dielectric constant of isolated nc-Si synthesized by Si ion implantation embedded in a SiO<sub>2</sub> thin film can be determined from C-V measurement based on the Maxwell–Garnett EMA and the SRIM simulation. For the nc-Si with a mean size of  $\sim$ 4.5 nm, the dielectric constant so determined is 9.8, being consistent with a theoretical prediction. This value is significantly lower than the static dielectric constant (11.9) of bulk crystalline Si, indicating the significance of nc-Si size effect. On the other hand, since the dielectric constant of the nc-Si is known, the depth profile of the effective dielectric constant of the oxide layer containing the nc-Si can be calculated with the EMA, and the information is useful to the design and modeling of nc-Si-based memory devices.

This work has been financially supported by the Ministry of Education Singapore under Project No. ARC 1/04.

<sup>1</sup>L. Pavesi, L. Dal Negro, C. Mazzoleni, G. Franzo, and F. Priolo, Nature (London) **408**, 440 (2000).

<sup>2</sup>R. J. Walters, G. I. Bourianoff, and H. A. Atwater, Nat. Mater. **4**, 143 (2005).

<sup>3</sup>C. Y. Ng, T. P. Chen, Y. Liu, M. S. Tse, and D. Gui, Electrochem. Solid-State Lett. **8**, G8 (2005).

<sup>4</sup>S. Tiwari, F. Rana, H. Hanafi, A. Hartstein, E. F. Crabbé, and K. Chan, Appl. Phys. Lett. **68**, 1377 (1996).

<sup>5</sup>Y. Liu, T. P. Chen, C. Y. Ng, M. S. Tse, P. Zhao, Y. Q. Fu, S. Zhang, and S. Fung, Nanotechnology **16**, 1119 (2005).

<sup>6</sup>S. Lombardo, B. De Salvo, C. Gerardi, and T. Baron, Microelectron. Eng. **72**, 388 (2004).

<sup>7</sup>P. Dimitrakis, E. Kapetanakis, D. Tsoukalas, D. Skarlatos, C. Bonafos, G. B. Asssayag, A. Claverie, M. Perego, M. Fanciulli, V. Soncini, R. Sotgiu, A. Agarwal, M. Ameen, C. Sohl, and P. Normand, Solid-State Electron. 48, 1511 (2004).

<sup>8</sup>T. P. Chen, Y. Liu, M. S. Tse, O. K. Tan, P. F. Ho, K. Y. Liu, D. Gui, and A. L. K. Tan, Phys. Rev. B **68**, 153301 (2003).

<sup>9</sup>J. F. Ziegler, J. P. Biersack, and U. Littmark, *The Stopping and Range of Ions in Solids* (Pergamon, New York, 1985), Vol. 1.

<sup>10</sup>H.-Ch. Weissker, J. Furthmuller, and F. Bechstedt, Phys. Rev. B 67, 165322 (2003).

<sup>11</sup>L. N. Dinh, L. L. Chase, M. Balooch, W. K. Siekhaus, and F. Wooten, Phys. Rev. B **54**, 5029 (1996).

<sup>12</sup>T. P. Chen, Y. Liu, M. S. Tse, P. F. Ho, D. Gui, and S. Fung, Appl. Phys. Lett. **81**, 4724 (2002).

<sup>13</sup>L. Ding, T. P. Chen, Y. Liu, C. Y. Ng, Y. C. Liu, and S. Fung, Appl. Phys. Lett. 87, 121903 (2005).

<sup>14</sup>L. Ding, T. P. Chen, Y. Liu, C. Y. Ng, and S. Fung, Phys. Rev. B 72, 125419 (2005).

<sup>15</sup>L.-W. Wang and A. Zunger, Phys. Rev. Lett. **73**, 1039 (1994).

<sup>16</sup>S. M. Sze, *Physics of Semiconductor Devices*, 2nd ed. (Wiley, New York, 1981)

<sup>17</sup>D. R. Penn, Phys. Rev. **128**, 2093 (1962).

<sup>18</sup>R. Tsu, D. Babic, and L. Ioriatti, Jr., J. Appl. Phys. **82**, 1327 (1997).

<sup>19</sup>L.-W. Wang and A. Zunger, Phys. Rev. B **53**, 9579 (1996).

<sup>20</sup>C. Delerue, M. Lannoo, and G. Allan, Phys. Rev. B **68**, 115411 (2003).

<sup>21</sup>X. Cartoixa and L. W. Wang, Phys. Rev. Lett. **94**, 236804 (2005).

<sup>22</sup>F. Giustino and A. Pasquarello, Phys. Rev. B **71**, 144104 (2005).