# A study on interface and charge trapping properties of nitrided *n*-channel metal-oxide-semiconductor field-effect transistors by backsurface argon bombardment

P. T. Laia)

Department of Electrical and Electronic Engineering, The University of Hong Kong, Hong Kong

J. P. Xu

Department of Solid State Electronics, Huazhong University of Science and Technology, 430074 People's Republic of China

H. B. Lo and Y. C. Cheng

Department of Electrical and Electronic Engineering, The University of Hong Kong, Hong Kong

(Received 27 February 1997; accepted for publication 15 May 1997)

A low-energy (550 eV) argon-ion beam was used to directly bombard the backsurface of nitrided n-channel metal-oxide-semiconductor field-effect transistors (n-MOSFETs) after the completion of all conventional processing steps. The interface and oxide-charge trapping characteristics of the bombarded MOSFETs were investigated as compared to nonbombarded and reoxidized-nitrided n-MOSFETs. It was found that after bombardment, interface state density decreases and interface hardness against hot-carrier bombardment enhances, and oxide charge trapping properties were also improved. The improvements exhibit a turnaround behavior depending on bombardment conditions and could be attributed to stress compensation in the vicinity of the Si/SiO<sub>2</sub> interface and an annealing effect. © 1997 American Institute of Physics. [S0021-8979(97)05616-8]

## I. INTRODUCTION

With the shrinking of transistors to submicrometer dimensions in recent years, high quality thin gate dielectrics are required which possess excellent robustness against hotcarrier bombardment and radiation exposure, good blocking property against diffusion of dopants and impurities, etc. Thermal nitridation of SiO<sub>2</sub> using NH<sub>3</sub> has been reported to have many advantages over thermal oxide. 1-4 However, residual tensile stress exists at the Si/SiO2 interface of the nitrided oxide film and increases with higher interfacial nitrogen concentration.<sup>5</sup> In our previous work,<sup>6,7</sup> the backsurface Ar<sup>+</sup> bombardment method was proposed to improve the electrical characteristics of *n*-channel metal-oxidesemiconductor field-effect transistors (n-MOSFETs) with thermally grown and NH3-nitrided oxides as gate dielectrics after they were completely fabricated. It was shown that the channel mobility of n-MOSFETs and the interface properties of MOS capacitors can be improved by this technique. In this work, studies on hot-carrier-induced degradation of interface properties, and oxide charge trapping characteristics of bombarded *n*-MOSFETs with nitrided gate oxides are performed, and results are expressed in terms of bombardment effects on hot-carrier-induced degradations of peak linear transconductance  $(G_m)$ , shift of threshold voltage  $(V_T)$  and increase of interface state density  $(D_{it})$ . NH<sub>3</sub> nitridation is chosen to introduce electron traps in the gate oxide so as to facilitate a comparison between the effects of bombardment and reoxidation on the charge trapping behavior of the oxide.

## **II. EXPERIMENT**

The *n*-MOSFETs and MOS capacitances used in this study were fabricated on *p*-type (100) silicon wafers with a resistivity of  $6-8~\Omega$  cm by the self-aligned  $n^+$  polysilicon

gate process. Thermal gate oxide was grown at 100 °C in Ar-diluted O2, and then nitrided at 1000 °C for 60 min in pure NH<sub>3</sub>. Finally, samples were annealed at 1000 °C for 30 min either in  $N_2$  (denoted as NO) or in dry  $O_2$  (reoxidation, denoted as RNO). The gate oxides had a thickness of 250 Å for NO samples and 275 Å for RNO samples as determined by capacitance-voltage (C-V) measurements. After completing all conventional processing steps for the n-MOSFETs, the wafers of NO samples were put into a vacuum chamber and a low-energy (550 eV) Ar<sup>+</sup> beam with 0.5 mA/cm<sup>2</sup> intensity was applied to directly bombard the backsurface of the wafers at room temperature under a vacuum of 3.2 mPa. Four different bombardment durations 0, 10, 20, and 40 min, were performed, with the corresponding samples denoted as NO0, NO10, NO20, and NO40, respectively. Subsequently, the wafers were annealed in N<sub>2</sub> at 450 °C for 20 min. Hotcarrier stress with maximum substrate current ( $V_D = 2V_G$ = 8 V) on the transistors and high-field injection with a constant current density  $(-1 \text{ mA/cm}^2)$  on the capacitances were then performed to study their interface properties. After this, their Si/SiO<sub>2</sub> interfaces were characterized by chargepumping technique on the MOSFETs and high-frequency, quasi-static C-V measurements on the capacitors. Hole trapping was depicted by the changes of peak linear transconductance  $(\Delta G_m)$  and threshold voltage  $(\Delta V_T)$  of the nMOSFETs after low-gate-voltage stress ( $V_G = 1$  V and  $V_D = 7$  V), while electron trapping was characterized by the change in gate voltage ( $\Delta V_G$ ) during stressing with a constant current density  $(-1 \text{ mA/cm}^2)$  on the MOS capacitors. The channel length L and width W of the MOSFETs are 1 and 24  $\mu$ m, respectively, and the area of the capacitors are 10<sup>-4</sup> cm<sup>2</sup>. All measurements were carried out under lighttight and electrically shielded condition.

TABLE I. Comparison between interface-state densities before and after bombardment for different times (10, 20, and 40 min).

|                                                   | NO10        | NO20        | NO40        |

|---------------------------------------------------|-------------|-------------|-------------|

| Pre-bombardment                                   |             |             |             |

| $D_{it}(10^{11} \text{ cm}^{-2} \text{ eV}^{-1})$ | 2.36 - 2.46 | 1.44 - 1.53 | 1.51 - 1.79 |

| Post-bombardment                                  |             |             |             |

| $D_{it}(10^{10} \text{ cm}^{-2} \text{ eV}^{-1})$ | 8.15-8.32   | 4.75 - 4.93 | 7.19 - 7.51 |

| $\Delta D_{it}(\%)$                               | 65.5-66.2   | 66.9-67.8   | 52.4-58.1   |

### III. RESULTS AND DISCUSSIONS

# A. Si/SiO<sub>2</sub> interface properties

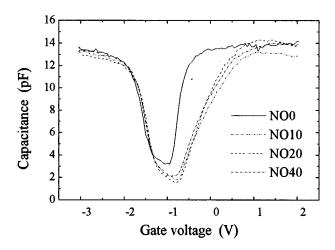

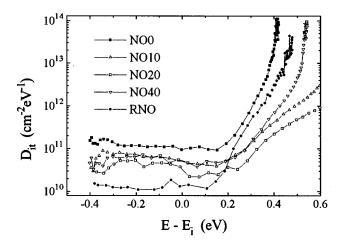

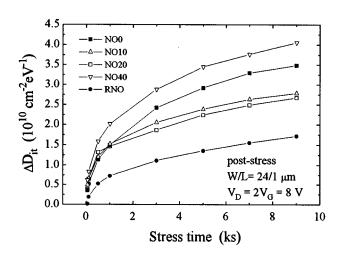

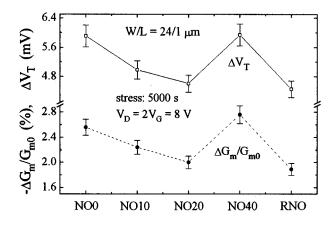

Table I lists comparison between interface state densities  $D_{it}$  before and after bombardment measured on the same transistors for NO10, NO20, and NO40 samples. It can be clearly seen that  $D_{it}$  is decreased to a different extent after bombardment for a different duration, with a minimum value for 20 min. The fact is further supported by C-V results on the MOS capacitors adjacent to the transistors. Figure 1 gives some typical quasi-static C-V characteristics before and after bombardment for different time. The extracted distribution of interface state density in the energy band gap is presented in Fig. 2, which is obviously in good agreement with the results in Table I. Furthermore, results of hot-carrier stress on the bombarded MOSFETs in Fig. 3 and high-field stress on the MOS capacitors in Table II show that a corresponding improvement of interface hardness against hotcarrier bombardment is obtained as compared to the nonbombarded sample, even though it is not as large as that of the RNO sample. It can be observed that as bombardment time increases, interface state creation ( $\Delta D_{it}$ ) decreases to a minimum value (NO20 sample), and then increases to a value comparable with NO0 sample (NO40 sample), indicating a turnaround behavior. Corresponding to  $\Delta D_{it}$  behaviors,  $\Delta V_T$  and  $\Delta G_m$  for all the samples also exhibit a similar variation trend after hot-carrier stress, as shown in Fig. 4, suggesting that  $\Delta V_T$  and  $\Delta G_m$  should mainly rely on the change of interface states under maximum substrate current stress.

FIG. 1. Typical quasi-static C-V characteristics for NO samples with different bombardment time.

FIG. 2. Distributions of interface state density in the energy bandgap before and after bombardment for different times (10, 20, and 40 min).

The above facts might be attributed to relaxation of mechanical stress, or recovery of distorted bonds at Si/SiO2 interface after bombardment. Measurement and simulation<sup>5</sup> showed that the higher residual tensile stress exists in the nitrided oxide film than in pure oxide film due to nitrogen incorporation near the Si/SiO2 interface. In other words, there is a distorted interfacial region because of the formation of mismatched Si-N bonds in the Si-O network. The backsurface bombardment could generate a lattice-damaged layer at the back of the wafer which is likely to give rise to a compressive stress at the surface of the wafer, thus compensating the original tensile stress. The resulting type and amount of net stress depend on bombardment duration under a given ion energy and density. If compressive stress just cancels tensile stress, a strainless Si/SiO2 interface, hence the lowest  $D_{it}$  and smallest  $\Delta D_{it}$  would be obtained. The results of NO20 sample seem to correspond to this case. Naturally, it can be deduced that if bombardment duration is too long, an overcompensation would result, and the initial tensile stress would become compressive after bombardment, thus a

FIG. 3. Interface state creation as a function of stress time at  $V_D=2\,V_G=8\,$  V for all n-MOSFETs.

1948

TABLE II. Increase in midgap interface-state densities of MOS capacitances after high-field injection stress  $(-1 \text{ mA/cm}^2)$  for 100 s.

|                                                                    | NO0       | NO10      | NO20      | NO40      | RNO       |

|--------------------------------------------------------------------|-----------|-----------|-----------|-----------|-----------|

| $\frac{\Delta D_{itm}}{(10^{12} \text{ cm}^{-2} \text{ eV}^{-1})}$ | 2.93-3.43 | 1.35–1.57 | 1.12–1.33 | 2.69-3.25 | 1.00-1.15 |

turnaround behavior occurs, as observed for the NO40 sample. Therefore, a suitable bombardment time should be chosen for a given ion energy and density to obtain the best interface properties. For RNO samples, besides the relaxation of interfacial stress, considerable elimination of hydrogen-related species near the interface (as described below) is mainly responsible for its least interface state generation.

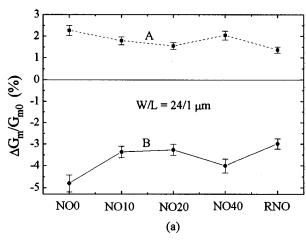

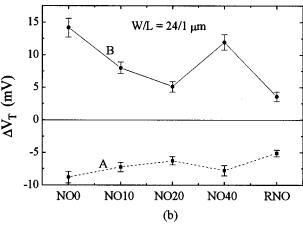

## B. Hole trapping properties

For all the smples, a low  $V_G$  stress ( $V_D$ =7 V and  $V_G$ = 1 V) for 2000 s followed by 20 s of electron injection at  $V_D = V_G = 8$  V were employed to investigate the effects of hole trapping on the change of peak linear transconductance  $(\Delta G_m)$  and shift of threshold voltage  $(\Delta V_T)$ , and the corresponding results are given in Figs. 5(a) and 5(b), respectively. A positive  $\Delta G_m$  and a negative  $\Delta V_T$  are observed in the low  $V_G$  stress phase, which can be attributed to the channel shortening effect caused by hole trapping in the gate oxide localized near the drain junction.<sup>8,9</sup> Subsequent short electron injection results in a large positive  $V_T$  shift and  $G_m$  degradation as a result of the compensation of the trapped holes and the filling of generated neutral electron traps by the injected electrons. As can be seen in Fig. 5, NO20 oxide has minimum hole trapping among the bombarded samples based on the changes of  $G_m$  and  $V_T$ , and a turnaround behavior similar to that in Figs. 1 and 2 is again found for the hole-trapping characteristics. Therefore, it can be concluded that bombardment with suitable duration can also effectively reduce the hole traps in the oxide to a level close to that in RNO oxide, possibly by means of stress compensation near the Si/SiO<sub>2</sub> interface.

FIG. 4. Degradation of peak linear transconductance and shift of threshold voltage after 5000 s stress at  $V_D=2\,V_G=8\,$  V for all n-MOSFETs.

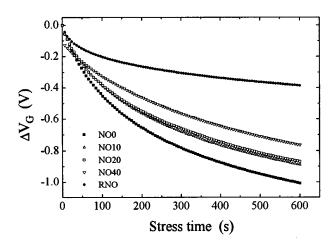

# C. Electron trapping properties

Electron trapping properties of the gate oxides of the bombarded samples were also studied by monitoring the change in gate voltage ( $\Delta V_G$ ) to maintain a constant current density ( $-1~\text{mA/cm}^2$ ) through the MOS capacitors adjacent to corresponding transistors. As shown in Fig. 6, NO0 and RNO oxides exhibit largest and smallest  $\Delta V_G$ , respectively. The former results from significant trapping at electron traps generated by hydrogen-related species decomposed from NH<sub>3</sub> during nitridation processing,  $^{10-12}$  which are effectively eliminated in the latter by the reoxidation step. While the bombarded samples show a gradually decreased  $\Delta V_G$  with bombardment time, suggesting suppressed electron trapping to some extent, this can be ascribed to an annealing effect on the gate oxide during  $\Lambda^+$  bombardment,  $^7$  which can remove

FIG. 5. (a) Percentage change of peak linear transconductance and (b) threshold voltage shift for all n-MOSFETs. Curve A immediately after low  $V_G$  stress at  $V_G=1$  V and  $V_D=7$ V for 2000 s. Curve B after a subsequent short electron injection phase at  $V_G=V_D=8$  V for 20 s.

FIG. 6. Change in gate voltage vs time during constant current stressing  $(-1 \text{ mA/cm}^2)$  for all capacitors adjacent to their corresponding transistors.

part of the hydrogen-related species. As shown by the NO40 device, the longer the bombardment time, the more obvious the annealing effect is. So, it is expected that elimination of more hydrogen-related species, results in better suppression of electron trapping and a harder interface can be achieved by optimizing the bombardment time, ion beam energy, and intensity. Further work is being carried out to verify this conjecture.

#### IV. SUMMARY

1950

In summary, possible stress relief at the  $Si/SiO_2$  interface and in the gate oxide induced by backsurface  $Ar^+$  bombardment can reduce interface states and hole traps of nitrided n-MOSFETs, and also enhance interface resistance against hot-carrier bombardment. Moreover, an annealing effect resulting from the bombardment can improve the electron-

trapping properties of the oxides to some extent. Although these improvements are not as large as those achieved by reoxidation, the bombardment does not decrease the nitrogen content in the nitrided gate oxide, and thus its resistance against dopant/impurity penetration into the conduction channel of the devices. Therefore, backsurface bombardment is a simple and promising technique for improving the reliability of MOS devices and is fully compatible with existing integrated circuit (IC) processing.

### **ACKNOWLEDGMENTS**

The authors would like to thank M. Q. Huang, G. Q. Li, and S. H. Zeng for their support of Ar<sup>+</sup> bombardment. This work is financially supported by Research Grant Council and Committee on Research and Conference Grant grants.

- <sup>1</sup>T. Ito, T. Nakamura, and H. Ishikawa IEEE Trans. Electron Devices **ED-29**, 498 (1982).

- <sup>2</sup>S. K. Lai, J. Lee, and V. K. Dham, IEDM Tech. Dig. 190 (1983).

- <sup>3</sup>F. L. Terry, Jr., R. J. Aucoin, M. L. Naiman, and S. D. Senturia IEEE Electron Device Lett. **EDL-4**, 191 (1983).

- <sup>4</sup>W. Yang, R. Jayaraman, and C. G. Sodini IEEE Trans. Electron Devices ED-35, 935 (1988).

- <sup>5</sup>H. S. Momose, T. Morimoto, K. Yamabe, and H. Iwai, IEDM Tech. Dig. 65 (1990).

- <sup>6</sup>P. T. Lai, Z. Xu, G. Q. Li, and W. T. Ng IEEE Electron Device Lett. EDL-16, 354 (1995).

- <sup>7</sup>P. T. Lai, M. Q. Huang, X. Zeng, S. H. Zeng, and G. Q. Li Appl. Phys. Lett. **68**, 2687 (1996).

- <sup>8</sup>B. S. Doyle, M. Bourcerie, C. Bergonzoni, R. Benecchi, A. Bravis, K. R. Mistry, and A. Boudou IEEE Trans. Electron Devices ED-37, 1869 (1990)

- <sup>9</sup>R. Bellens, P. Heremans, G. Groeseneken, and H. E. Maes IEEE Electron Device Lett. EDL-9, 232 (1988).

- <sup>10</sup>T. Hori, H. Iwasaki, Y. Naito, and H. Esaki IEEE Trans. Electron Devices ED-34, 2238 (1987).

- <sup>11</sup> S. T. Chang, N. M. Johnson, and S. A. Lyon Appl. Phys. Lett. **44**, 316 (1984)

- <sup>12</sup>S. K. Lai, D. W. Dong, and A. Hartsein J. Electrochem. Soc. **129**, 2042 (1982).