APPLIED PHYSICS LETTERS VOLUME 85, NUMBER 18 1 NOVEMBER 2004

## A quantitative study of the relationship between the oxide charge trapping over the drain extension and the off-state drain leakage current

Jiayi Huang and T. P. Chen<sup>a)</sup>

School of Electrical & Electronic Engineering, Nanyang Technological University, Nanyang Avenue, Singapore 639798, Singapore

C. H. Ang and S. Manju

Chartered Semiconductor Manufacturing Ltd, Singapore 738406, Singapore

S. Fung

Department of Physics, The University of Hong Kong, Hong Kong

(Received 29 April 2004; accepted 7 September 2004)

In this letter, we report an approach to quantitative study of the relationship between the oxide charge trapping over the drain extension due to electrical stress and the off-state drain leakage current. It is found that positive charge trapping over the drain extension leads to a significant increase in the off-state drain current if the edge direct tunneling (EDT) is dominant in the drain current but in contrast, it leads to a reduction in the drain current if the band-to-band tunneling in the Si surface is dominant. A quantitative relationship between the charge trapping and the off-state drain leakage current in the EDT regime is established. From the measurement of the off-state current in the EDT regime, the charge trapping can be determined by using the approach developed in this study. © 2004 American Institute of Physics. [DOI: 10.1063/1.1810211]

With the continuous scaling down of the gate oxide thickness, gate leakage current becomes significant and has impact on the device and circuit performance. As an important issue for the shrunk metal-oxide-semiconductor field effect transistors (MOSFETs), the off-state leakage current is critical to the subthreshold leakage in stand-by mode operation for a circuit.<sup>2</sup> Recent studies show that one of the gate leakage current components, edge direct tunneling (EDT) current from the gate to the drain extension, dominates the off-state leakage current for the sub-20 Å gate oxide<sup>3-5</sup> and contributes to the circuit power consumption. Reliability problems can be caused by electrical stress to the ultrathin gate dielectrics both over the channel<sup>6</sup> and in the edge region.5 The damage of the gate dielectric due to electrical stress could change the off-state leakage current and affect the circuit performance. Therefore, as an important reliability issue, a quantitative study of the influence of the stressinduced oxide charge trapping on the off-state leakage current is necessary. In this work, we report an approach to quantitative determination of the influence of the oxide charge trapping over the drain extension caused by electrical stress on the off-state drain leakage current.

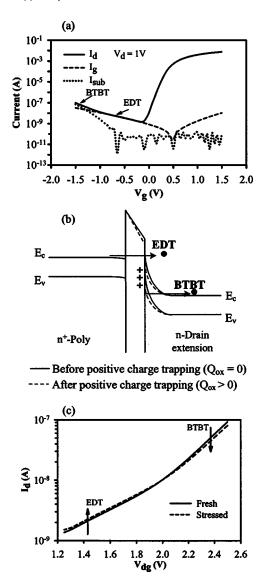

The devices used in this study were polycrystalline silicon-gate n-channel MOSFETs with a channel length of 0.13  $\mu$ m and a gate width of 10  $\mu$ m. The gate oxide thickness was 2 nm. The devices were stressed with a constant drain voltage (3.5 V) while the gate, source, and substrate were grounded. Current-voltage (I-V) measurements were carried out before and after each stress. Figure 1(a) shows the typical I-V characteristics at the drain voltage  $V_d=1$  V. As can be seen in this figure, under the off-state condition, i.e.,  $V_g < 0$ , the drain leakage current  $I_{\rm off}$  is almost equal to the gate leakage current  $I_g$ . Based on the gate leakage current model<sup>3</sup> and the analysis in Ref. 4, it can be concluded that

electrons direct tunneling from the conduction band of the  $n^+$  polycrystalline silicon gate to the conduction band of the n-type drain extension, i.e., the EDT current, is the origin of the off-state drain leakage current in this regime. A schematic of the EDT is shown in Fig. 1(b). On the other hand, when the gate voltage  $V_g$  becomes more negative ( $V_g < -1$  V), the drain current  $I_d$  increases with the substrate current  $I_{\rm sub}$  due to the well-known surface band-to-band tunneling (BTBT) mechanism. <sup>7,8</sup> As shown in Fig. 1(b), for a sufficiently negative  $V_g$ , electrons can tunnel from the valence band to the conduction band in the silicon surface region of the drain extension, i.e., the BTBT process occurs.

As both the EDT and the BTBT depend strongly on the oxide electric field, a small change in the oxide field can lead to a significant change in the drain current. An electrical stress may cause charge trapping in the gate oxide, and the oxide charge trapping over the drain extension will affect the EDT and the BTBT as the oxide field in this region is changed due to the charge trapping. This has been confirmed in our measurement. Figure 1(c) shows the drain leakage current  $(I_{off})$  before and after the electrical stress of 300 s. It can be seen that after the electrical stress,  $I_{\text{off}}$  governed by the EDT is increased while that governed by the BTBT is reduced. The increase of the EDT current is attributed to the increase of oxide electric field, while the decrease of the BTBT current is due to the reduction of the silicon surface electric field in the drain extension. As shown in Fig. 1(b), a positive charge trapping in the oxide near the Si/SiO<sub>2</sub> interface over the drain extension can increase the oxide electric field but reduce the silicon surface electric field. Therefore, the stress-induced positive charge trapping explains the  $I_{\text{off}}$ change in both EDT and BTBT regimes. Obviously, the increase in the EDT current is detrimental as it leads to an increase in the off-state power consumption.

As mentioned earlier, the oxide charge trapping over the drain extension will lead to a change in the oxide field and

a)Electronic mail: echentp@ntu.edu.sg

FIG. 1. (a) Typical I-V characteristics for nMOSFET before electrical stress; (b) energy band diagram in the drain extension before and after positive charge trapping and the illumination of the EDT and BTBT; and (c) drain current change in the EDT and BTBT regimes after a 300 s electrical stress.

thus a change in the EDT. The corresponding oxide voltage change can be described by  $\Delta V_{\rm ox} = Q_{\rm ox}/C_{\rm ox}$ , where  $Q_{\rm ox}$  is the oxide charge trapping over the drain extension defined as the equivalent areal density at the Si/SiO<sub>2</sub> interface, and  $C_{\rm ox}$  is the oxide capacitance per unite area. Based on the gate tunneling current model in Ref. 9 and taking into account the charge trapping, the gate tunneling current (i.e., the EDT) is found to be given by

$$I_{g} = A' \exp \left\{ \frac{20}{\phi_{b}} \frac{\left( |V_{\text{ox0}}| + \frac{Q_{\text{ox}}}{C_{\text{ox}}} \right)^{0.6}}{\phi_{b}^{0.6}} \left[ 1 - \frac{\left( |V_{\text{ox0}}| + \frac{Q_{\text{ox}}}{C_{\text{ox}}} \right)}{\phi_{b}} \right] \right\}$$

$$\times \exp \left\{ \frac{-BT_{\text{ox}} \left\{ 1 - \left[ 1 - \left( |V_{\text{ox0}}| + \frac{Q_{\text{ox}}}{C_{\text{ox}}} \right) / \phi_{b} \right]^{1.5} \right\}}{\left( |V_{\text{ox0}}| + \frac{Q_{\text{ox}}}{C_{\text{ox}}} \right)} \right\},$$

(1)

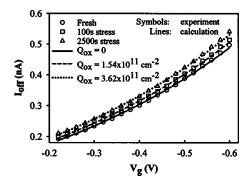

FIG. 2. Off-state drain current as a function of charge trapping. A linear relationship between the current and the charge trapping is observed for low charge trapping. The calculation shown in the inset indicates that a nonlinear relationship appears when  $Q_{\rm ox} > \sim 2 \times 10^{12}$  cm<sup>-2</sup>.

$=8\,\pi\sqrt{2m_{\rm ox}}\phi_b^{1.5}/3hq$ .  $V_{\rm ox0}$  is the externally applied gate oxide voltage,  $^4N$  is the carrier density,  $V_g$  is the potential difference between the gate and drain,  $A_{\rm eff}$  is the area of the drain extension,  $T_{\rm ox}$  is gate oxide thickness,  $\varepsilon_{\rm ox}=3.9\varepsilon_0$  ( $\varepsilon_0=8.854\times10^{-14}~{\rm F/cm}$ ) is the dielectric constant of SiO<sub>2</sub>,  $m_{\rm ox}=0.4m_0$  is the carrier effective mass,  $^9$  q $\phi_b=3.1~{\rm V}$  is the oxide barrier height,  $^9$  q is electronic charge, and q is the Planck constant. If the off-state current is dominated by the EDT, the drain current  $I_{\rm off}=I_g$ . In the following discussions, all are limited to this case, i.e., the off-state drain current in the EDT regime  $I_{\rm off}=I_g$ . The off-state drain current calculated with Eq. (1) versus the charge trapping is shown in Fig. 2, and the calculation is also compared with the measurement result as shown in the figure.

Usually,  $|V_{\rm ox0}| \gg |\Delta V_{\rm ox}| = |Q_{\rm ox}/C_{\rm ox}|$ . Therefore, Eq. (1) can be approximately written as

$$ln(I_{\text{off}}/I_{\text{off0}}) = aQ_{\text{ox}} + bQ_{\text{ox}}^2,$$

(2)

where  $I_{\text{off0}}$  is the off-state drain current before electrical stress (i.e.,  $Q_{\text{ox}}=0$ ),

$$a = \frac{20|V_{\text{ox0}}|^{0.6}}{\phi_b^{2.6}C_{\text{ox}}} \left[ \frac{0.6(\phi_b - |V_{\text{ox0}}|)}{|V_{\text{ox0}}|} - 1 \right] - \frac{BT_{\text{ox}}}{\phi_b^{1.5}|V_{\text{ox0}}|C_{\text{ox}}} \times \left[ 1.5(\phi_b - |V_{\text{ox0}}|)^{0.5} - \frac{\phi_b^{1.5}}{|V_{\text{ox0}}|} + \frac{(\phi_b - |V_{\text{ox0}}|)^{1.5}}{|V_{\text{ox0}}|} \right],$$

$$\begin{split} b &= -\frac{10}{\phi_b^{2.6} |V_{\text{ox0}}|^{0.4} C_{\text{ox}}^2} \bigg( 0.96 + 0.24 \frac{\phi_b}{|V_{\text{ox0}}|} \bigg) \\ &+ \frac{BT_{\text{ox}}}{\phi_b^{1.5} |V_{\text{ox0}}|^{1.5} C_{\text{ox}}^2} \Bigg[ 0.375 \bigg( \frac{|V_{\text{ox0}}|}{\phi_b - |V_{\text{ox0}}|} \bigg)^{0.5} \\ &+ 1.5 \bigg( \frac{\phi_b - |V_{\text{ox0}}|}{|V_{\text{ox0}}|} \bigg)^{0.5} - \frac{\phi_b^{1.5} - (\phi_b - |V_{\text{ox0}}|)^{1.5}}{|V_{\text{ox0}}|^{1.5}} \Bigg]. \end{split}$$

Therefore, from the measurement of the off-state drain current in the EDT regime, one can obtain the oxide charge trapping from Eq. (2).

To determine the  $Q_{\text{ox}}$ , one can measure the off-state drain leakage current  $I_{\text{off-}m}(i)$  in the EDT regime at different oxide voltage  $V_{\text{ox0}}(i)$  ( $i=1,2,3,\ldots n$ , where n is the number

where  $A' = A_{\rm eff}AV_eN/\varepsilon_{\rm ox}T_{\rm ox}, \quad A = q^3/8\pi h\phi_b$ , and B oxide voltage  $V_{\rm ox0}(i)$  (  $i=1,2,3,\ldots n$ , where n is the number Downloaded 08 Nov 2006 to 147.8.21.97. Redistribution subject to AIP license or copyright, see http://apl.aip.org/apl/copyright.jsp

FIG. 3. Comparison between the measurement and the calculation of the off-state drain current in the EDT regime.

of the data points) before and after electrical stress and then fit the measurement data by minimizing the error function below

$$F(Q_{\text{ox}}) = \sum_{i=1}^{n} \left[ \ln \left( \frac{I_{\text{off}-m}(i)}{I_{\text{off}0-m}(i)} \right) - \ln \left( \frac{I_{\text{off}-\text{cal}}(i)}{I_{\text{off}0-\text{cal}}(i)} \right) \right]^{2}$$

$$= \sum_{i=1}^{n} \left[ \ln \left( \frac{I_{\text{off}-m}(i)}{I_{\text{off}0-m}(i)} \right) - a(i)Q_{\text{ox}} - b(i)Q_{\text{ox}}^{2} \right]^{2}, \quad (3)$$

where  $I_{\rm off-cal}(i)$  is the off-state drain current calculated with Eq. (2). The  $Q_{\rm ox}$  corresponding to the minimum F can be found from  $dF/dQ_{\rm ox}=0$ . We have found that the second-order contribution of the  $Q_{\rm ox}$  [i.e., the term of  $b(i)Q_{\rm ox}^2$  in Eq. (3)] is negligible for actual charge trapping. For this case, the  $Q_{\rm ox}$  can be easily calculated with

$$Q_{\text{ox}} = \left\{ \sum_{i=1}^{n} a(i) \ln \left[ I_{\text{off-}m}(i) / I_{\text{off0-}m}(i) \right] \right\} / \sum_{i=1}^{n} a^{2}(i). \quad (4)$$

To check the correctness and accuracy of the above equations, we have calculated the  $I_{\rm off}$  with Eq. (1) using the  $Q_{\rm ox}$  values yielded from Eq. (4) and then compared the calculated  $I_{\rm off}$  with the corresponding measurement data. As shown in Fig. 3, the agreement between the calculation and the measurement is excellent.

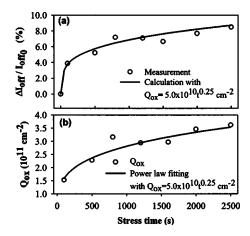

Figure 4(a) shows the increase in the  $I_{\rm off}$  with stress time. From the measured  $I_{\rm off}$ , the oxide charge trapping is calculated with Eq. (4) for different stress time, and the result is shown in Fig. 4(b). As can be seen in Fig. 4(b), the dependence of the charge trapping on the stress time (t) follows a power law, i.e.,  $Q_{\rm ox} \propto t^n$  with the exponential factor n=0.25. Similar power-law behaviors have been reported in literature. The exponent of 0.25 suggests that the charge trapping could be related to diffusion–limited electrochemical reactions. On the other hand, after the stress-time dependence of the charge trapping is obtained, the stress-time dependence of the off-state drain current can be also

FIG. 4. (a) Stress-time dependence of the increase in the off-state drain current in the EDT regime; and (b) stress-time dependence of the charge trapping. The off-state current was measured at  $V_{gs}$ =-0.5 V,  $V_{ds}$ =1 V, and  $V_s$ = $V_{sub}$ =0 V.

calculated with Eq. (1). The calculated stress-time dependence of the increase of the  $I_{\rm off}$  is shown in Fig. 4(a).

In conclusion, we have developed an approach to quantitative study on the influence of the oxide charge trapping over the drain extension caused by electrical stress on the off-state drain leakage current. It is shown that positive charge trapping over the drain extension leads to a significant increase in the off-state drain current if the EDT is dominant in the drain current. The quantitative relationship between the charge trapping and the off-state drain current in the EDT regime is obtained. By measuring the off-state drain current in the EDT regime and using the formula developed in this work, the charge trapping is determined quantitatively.

<sup>1</sup>C. Choi, K. Nam, Z. Yu, and R. Dutton, IEEE Trans. Electron Devices **48**, 2823 (2001).

<sup>2</sup>S. Mukhopadhyay and K. Roy, *Symposium On VLSI Circuit* (IEEE, Kyoto, 2003), p. 53.

<sup>3</sup>K. M. Cao, W. C. Lee, W. Liu, X. Jin, P. Su, S. K. H. Fung, J. X. An, B. Yu, and C. Hu, *International Electron Device Meeting Technical Digest* (IEEE, CA, 2000), p. 815.

<sup>4</sup>K. N. Yang, H. T. Huang, M. J. Chen, Y. M. Lin, M. C. Yu, S. M. Jang, D. C. H. Yu, and M. S. Liang, IEEE Trans. Electron Devices **48**, 1159 (2001).

<sup>5</sup>N. Yang, W. K. Henson, and J. J. Wortman, *International Electron Device Meeting Technical Digest* (IEEE, Washington, DC, 1999), p. 453.

<sup>6</sup>S. Tsujikawa, K. Watanabe, R. Tsuchiya, K. Ohnishi, and J. Yugami, *Symposium on VSLI Technology* (IEEE, Kyoto, 2003), p. 139.

<sup>7</sup>T. P. Chen, J. Huang, M. S. Tse, and X. Zeng, Solid-State Electron. **46**, 2013 (2002).

<sup>8</sup>Y. Taur, D. A. Buchanan, W. Chen, D. J. Frank, K. E. Ismail, S. H. Lo, G. A. Sai-Halasz, R. G. Viswanathan, H.-J. C. Wann, S. J. Wind, and H. S. Wong, Proc. IEEE **85**, 486 (1997).

<sup>9</sup>W. C. Lee and C. Hu, IEEE Trans. Electron Devices 48, 1366 (2001).

<sup>10</sup>S. Ogawa and N. Shiono, Phys. Rev. B **51**, 4218 (1995).

<sup>11</sup>S. S. Tan, T. P. Chen, C. H. Ang, and L. Chan, Appl. Phys. Lett. **82**, 269 (2003).