Realizing In-Memory Baseband Processing for Ultra-Fast and Energy-Efficient 6G

Qunsong Zeng, Jiawei Liu, Mingrui Jiang, Jun Lan, Yi Gong, Zhongrui Wang, Yida Li, Can Li, Jim Ignowski, and Kaibin Huang

Abstract—To support emerging applications ranging from holographic communications to extended reality, next-generation mobile wireless communication systems require ultra-fast and energy-efficient baseband processors. Traditional complementary metal-oxide-semiconductor (CMOS)-based baseband processors face two challenges in transistor scaling and the von Neumann bottleneck. To address these challenges, in-memory computingbased baseband processors using resistive random-access memory (RRAM) present an attractive solution. In this paper, we propose and demonstrate RRAM-implemented in-memory baseband processing for the widely adopted multiple-input-multiple-output orthogonal frequency division multiplexing (MIMO-OFDM) air interface. Its key feature is to execute the key operations, including discrete Fourier transform (DFT) and MIMO detection using linear minimum mean square error (L-MMSE) and zero forcing (ZF), in one-step. In addition, RRAM-based channel estimation module is proposed and discussed. By prototyping and simulations, we demonstrate the feasibility of RRAM-based full-fledged communication system in hardware, and reveal it can outperform state-of-the-art baseband processors with a gain of  $91.2\times$  in latency and  $671\times$  in energy efficiency by large-scale simulations. Our results pave a potential pathway for RRAMbased in-memory computing to be implemented in the era of the sixth generation (6G) mobile communications.

Index Terms—In memory computing, baseband processing, resistive switching memory, 6G communications, MIMO-OFDM.

## I. INTRODUCTION

While the fifth generation (5G) mobile networks are being deployed, the sixth generation (6G) is under development all over the world to provide a new infrastructure for propelling the digital economy forward and realizing Society 5.0 [1]. The performance of 6G will be unprecedented as reflected in a set of target key performance indicators (KPIs), dictating a peak data rate to go beyond 100Gb/s, having a minimum latency 0.1ms, and achieving an energy efficiency of  $10^{-12}$ J/bit [2]–[6]. This coined the term *ultra-fast-and*energy-efficient (UFEE) communication and will enable a wide range of emerging applications, for example, industrial automation [7], [8], tactile internet [9]-[11], holographic communications [12], [13], and digital twin [14], [15]. Hence, this provides a strong motivation for 6G researchers to explore the largely unoccupied Terahertz (THz) spectrum [2]-[6]. However, the required scaling up of baseband data rates to the

Q. Zeng, J. Liu, M. Jiang, Z. Wang, C. Li, and K. Huang are with The University of Hong Kong, Hong Kong SAR. J. Liu, J. Lan, Y. Gong, and Y. Li are with Southern University of Science and Technology, Shenzhen, China. J. Ignowski is with Hewlett Packard Enterprise, United States. Q. Zeng and J. Liu contributed equally to this work. Contact: K. Huang (huangkb@eee.hku.hk).

hundreds of Gbps level will dramatically increase the power consumption and complexity of baseband processing, making it challenging to realize the 6G vision [16]–[18]. This is further exacerbated by the increasingly sophisticated communication techniques required, including large-scale multiple-input multiple-output (MIMO), high-dimensional orthogonal frequency division multiplexing (OFDM), and interference management. From 2G to 5G era, baseband processing demands have been satisfied largely by shrinking transistor size as governed by Moore's law. Accordingly, the semiconductor industry has evolved from planar bulk Metal-Oxide-Semiconductor Field-Effect Transistors (MOSFETs) to the recent 3D FinFETs and Gate All Around (GAA) architectures to improve transistor performance and density in an integrated circuit (IC) chip [19]. However, this approach is facing increasing challenges as transistor size approaches the atomic limit [20]. In view of the Moore's Law coming to an end, we propose the new paradigm called in-memory baseband processing for the post-Moore era, which adopts the emerging in-memory computing architecture instead of relying on transistor densification, to pave the way towards realizing the 6G UFEE connectivity.

Baseband processing and computing at large face two bottlenecks: the von Neumann bottleneck and the power wall, incurring large energy and footprint overheads. The former is due to data shuttling between the physically separated processing and storage units, resulting in significant latency and high energy consumption (e.g., 100-time more than digital logical circuits). In the latter, the increasing power density of transistors as the transistor size shrinks has created a "power wall" that limits practical processor frequency to ~4 GHz since 2006 [21], falling far short of the requirements for THz communications. In the past decade, researchers have started to improve computing latency and energy consumption by employing an architecture that co-locates data processing and storage, so called in-memory computing. Rather than making incremental improvements to conventional systems such as parallelism or memory bandwidth, in-memory computing takes a different approach by performing calculations where the data is located, thus fundamentally changing the von Neumann architecture [22]. This method is similar to the way the human brain processes information in the networks of neurons and synapses, where there is no separation between computation and memory [23]. In contrast to traditional computing schemes, in-memory computing eliminates latency and energy usage issues associated with the memory wall. However, this new architecture requires computational memory devices that can both store data and perform cal-

1

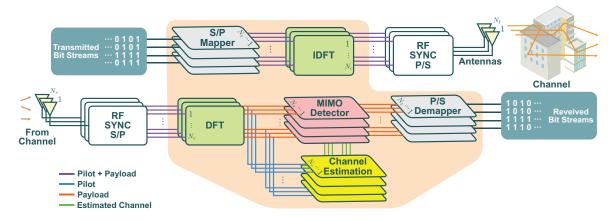

Figure 1. The architecture of RRAM-based transmitter: It consists of baseband processing modules [i.e., mapper and IDFT], RF modem, and an array of transmit antennas. Each layer represents a piece of RRAM-based circuit. The architecture of RRAM-based receiver: It is comprised of an array of receive antennas, RF front-end, and baseband processing modules [i.e., DFT, channel estimation, MIMO detection, and demapper].

culations simultaneously, usually by leveraging physical laws like Ohm's and Kirchhoff's laws in electrical circuits [24]. Emerging non-volatile memories such as resistive randomaccess memory (RRAM) is touted as one of the most potential candidates for such computational memory devices [25]. It has been reported that parallel execution of a larger number (e.g., millions) of multiply-and-accumulate (MAC) operations for matrix vector multiplications (MVM) can be accomplished with extremely high energy-efficiency and low latency [26]. This makes in-memory computing a UFEE solution for MVM intensive applications such as deep neural networks [27]-[42] and linear algebra computation [43]-[46]. Such advantages can naturally contribute to the trend of seamless integration of communication and artificial intelligence (AI) for the next-generation Internet-of-Things (IoTs). A new paradigm for communications called in-memory baseband processing, which adopts the emerging in-memory computing architecture and novel signal processing approach, are potential key factors to alleviate the challenges faced by researchers in realizing UFEE connectivity in the era of 6G.

6G will feature scaling up of different physical-layer technologies, for example, massive MIMO using large-scale antenna arrays [47] and OFDM comprising thousands of subcarriers [4]. The resultant baseband processing will involve frequent large-scale matrix operations. This motivates us to propose the new paradigm of in-memory baseband processing, which relocates the conventional digital operations to the analogue domain to achieve UFEE processing. In this paper, we present the design of an in-memory baseband processor for MIMO-OFDM which is a dominant air-interface technology for 5G-and-beyond [2]–[5], [48]. The key novelty includes modules, namely OFDM demodulation, MIMO detection, and channel estimation, which are designed and implemented using in-memory computing approach based on Ta/TaO<sub>x</sub>/Pt RRAM chip. The OFDM module implements the discrete Fourier transform (DFT) using two RRAM crossbar arrays. Using such arrays to store DFT matrix enables one-step DFT operation, cutting down the power/latency overheads in conventional CMOS-based processor significantly. Furthermore, the required channel matrix inversion for MIMO detection is realized using a novel RRAM circuit featuring stability and easy mode switching, enabling the one-step operation. The performance of our design is evaluated using proof-of-concept prototypes for separate modules and a complete system by physical experiments, respectively, and simulations for a large-scale communication system. We show that the throughput and energy-efficiency can be boosted up to  $91.2\times$  and  $671\times$  respectively as compared to state-of-the-art CMOS-based baseband processors.

## II. OVERVIEW OF RRAM-BASED BASEBAND PROCESSOR

In this paper, the baseband processor targets the MIMO-OFDM air interface, where a pair of multi-antenna transmitter and receiver communicate over a broadband channel. In broadband communications, frequency selective fading occurs when the channel having a coherence bandwidth is smaller than that of the signal causes its distortion. As a popular technology for coping with such fading as well as inter-symbol interference, OFDM is adopted to divide the whole bandwidth into  $N_c$  orthogonal sub-channels. As a result, each sub-channel, say the k-th sub-channel, is a narrowband channel with  $N_t$  transmit and  $N_r$  receive antennas, modelled by a MIMO-channel matrix  $\mathbf{H}^{(k)} \in \mathbb{C}^{N_r \times N_t}$  that is fixed within an OFDM symbol. The input-output relation of a MIMO system over the k-th sub-channel is given as

$$\mathbf{y}^{(k)} = \mathbf{H}^{(k)} \mathbf{x}^{(k)} + \mathbf{z}^{(k)}, \tag{1}$$

where  $\mathbf{x}^{(k)} \in \mathbb{C}^{N_t \times 1}$  consists of symbols at the k-th subcarrier,  $\mathbf{y}^{(k)} \in \mathbb{C}^{N_r \times 1}$  comprises the received symbols at the k-th sub-carrier, and  $\mathbf{z}^{(k)}$  represents the *additive white Gaussian noise* (AWGN) in propagation.

The architectures of the RRAM-based transceiver are illustrated in Fig. 1. Before baseband processing, the receiver still needs sampling at the RF front-end. Compared with a fast analogue-to-digital converter (ADC) design for traditional digital baseband processing, the proposed baseband processor features the direct processing of analogue-valued input signals so that the ADC can be replaced with a simpler sample-and-hold circuit. The baseband (information) processing starts at

the mapper module in the transmitter that transforms bits into symbols and ends at the demapper module in the receiver that transforms the symbols back to bits. The digital modulation is chosen as 16 quadrature amplitude modulation (16-QAM) unless specified otherwise, which maps a 4-bit string to one of the 16 points on the constellation diagram. The bit stream is split into in-phase (denoted by I) and quadrature (denoted by Q) streams, associated with 0-degree and 90-degree phase shifts of the carrier wave, respectively. I and Q components are Gray encoded, i.e., neighbour points only differ in a single bit, to produce symbol points in the constellation. The system performance is evaluated by two metrics: i) The modulation error ratio (MER) measures the dispersion of the constellation of the received symbols. To be specific, given total M transmitted symbols, the definition of MER is

$$MER = 10 \log_{10} \left( \frac{\sum_{m=1}^{M} (I_m^2 + Q_m^2)}{\sum_{m=1}^{M} [(I_m' - I_m)^2 + (Q_m' - Q_m)^2]} \right) dB,$$

(2)

where  $I_m$  and  $Q_m$  denote the in-phase and quadrature components of the m-th transmitted symbol while  $I_m'$  and  $Q_m'$  denote the in-phase and quadrature components of the received symbol. ii) The  $bit\ error\ ratio\ (BER)$  is the number of bit errors divided by the total number of transmitted bits. To be specific, during the studied time interval, the BER is given by

$$BER = \frac{\text{\# error bits}}{\text{\# total transmitted bits}} \times 100\%.$$

(3)

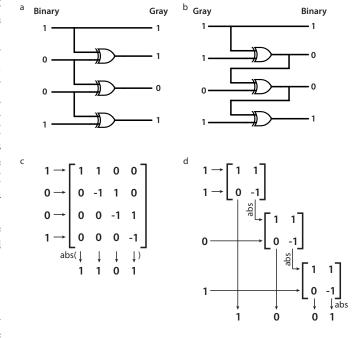

In this work, we focus on the baseband processing between the mapper and demapper. The module in the transmitter performs inverse DFT (IDFT). For the receiver, the three modules are DFT module, channel estimator, and MIMO detector. To reconcile signals and channels in the complex domain and the fact that RRAM devices store and compute real numbers, we propose to apply the mapping  $\mathcal{R}: \mathbb{C}^{K\times L} \to \mathbb{C}^{2K\times 2L}$  which transforms a complex matrix  $\mathbf{A} \in \mathbb{C}^{K\times L}$  into a real matrix  $\mathcal{R}(\mathbf{A}) = \begin{bmatrix} \Re(\mathbf{A}) & -\Im(\mathbf{A}) \\ \Im(\mathbf{A}) & \Re(\mathbf{A}) \end{bmatrix} \in \mathbb{R}^{2K\times 2L}$ . The complex vector is translated as the input voltages (or currents) for the RRAM array, with the mapping  $\mathcal{T}: \mathbb{C}^{K\times 1} \to \mathbb{R}^{2K\times 1}$  transforming a complex vector  $\mathbf{x} \in \mathbb{C}^{K\times 1}$  into a real vector  $\mathcal{T}(\mathbf{x}) = \begin{bmatrix} \Re(\mathbf{x}) \\ \Im(\mathbf{x}) \end{bmatrix} \in \mathbb{R}^{2K\times 1}$ . Such transformations enables the equivalent computation involving complex matrices and vectors.

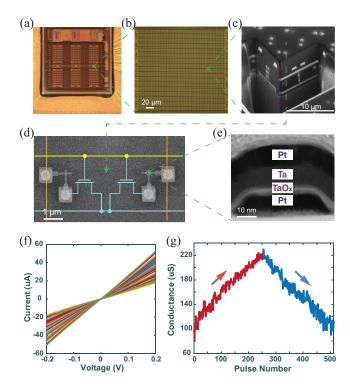

We use the Ta/TaO $_x$ /Pt-based RRAM arrays as the hardware accelerators for its compatibility with traditional CMOS process and reliable electrical characteristics. Details of the RRAM array fabrication and integration are described in Appendix A. The wire-bonded integrated RRAM chip that we used to implement the baseband processor modules is shown in Fig. 2(a), which contains three  $64 \times 64$  RRAM crossbar arrays and one of them is shown in Fig. 2(b). The 50nm  $\times$  50nm Ta/TaO $_x$ /Pt RRAMs are integrated with back-end-of-the-line (BEOL) processing on top of the control peripheral circuits (see Fig. 2(c)). The peripheral control circuits are implemented with a commercial 180nm technology integrated chip, among

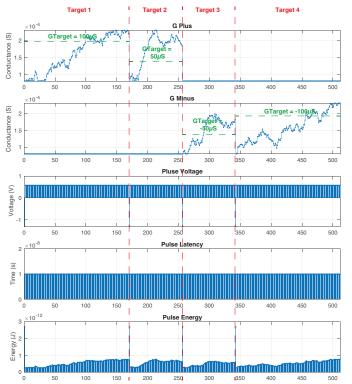

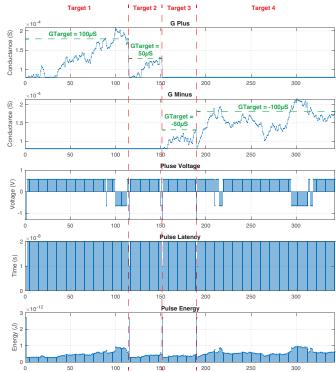

Figure 2. Integrated RRAM chip and measurements. (a) A photo of a wire-bounded integrated RRAM chip, which contains three 64 × 64 1T1R crossbar arrays, row MUXes, column MUXes, transimpedance amplifiers (TIA), sample-and-hold, and ADC. (b) Optical image of a  $64 \times 64$  RRAM crossbar array. (c) The cross-section view of the integrated chip with CMOS circuits at the bottom, inter-connection in the middle, and metal throughhole on the surface used for RRAM and back-end process integration (d) Top view of four cross-point RRAM devices. (e) The TEM image of the RRAM device. (f) Ohmic behaviour of RRAM devices. The linear I-V relationship is illustrated at different conductance states under different read voltages (-0.2~0.2V). (g) The conductance modulation characteristic of the RRAM device. A train of voltage pulses (pulse width 10ns) are applied for the RRAM conductance modulation measurements. The magnitude of voltages starts at 0.60V and grows to 0.70V smoothly for potentiation, while it starts at -0.50V and drops to -0.65V gradually for depression. The cycle-to-cycle variations are 4.41% during potentiation and 5.44% during depression, respectively. The conductance ranges from  $79.93\mu S$  to  $230.99\mu S$ in the behavioral measurement.

which the access transistors are highlighted in Fig. 2(d). Such one-transistor-one-resistor (1T1R) array architecture avoids the sneak current issue during RRAMs' conductance programming and allows each cell in the array to be accessed independently [49]. The cross-sectional transmission electron microscopy (TEM) image of the RRAM device is shown in Fig. 2(e). As a non-volatile analogue device, our RRAM device exhibits linear Ohmic behaviour (see Fig. 2(f)) to ensure accurate in-memory computing. For matrix mapping, the conductance programming of the fabricated RRAM device can be achieved by applying a train of positive pulses (0.60~0.70V/10ns) for potentiation, and continuous negative pulses (-0.50~-0.65V/10ns) for depression (see Fig. 2(g)).

# III. ORTHOGONAL FREQUENCY-DIVISION MULTIPLEXING MODULE

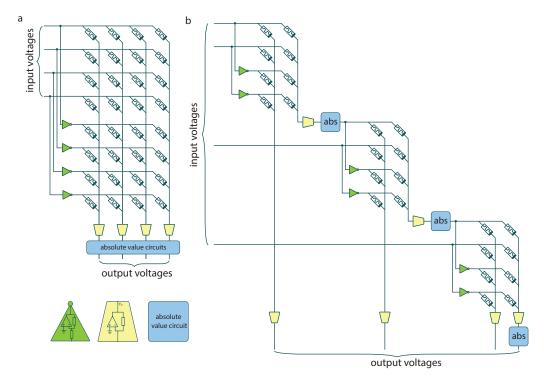

The RRAM-based DFT module is illustrated in Fig. 3(a), where data are modulated onto non-interfering sub-carriers in the frequency domain. The transformation between the time

Figure 3. Orthogonal frequency-division multiplexing modules. (a) The architecture of RRAM-based DFT module. The DFT matrix  $\mathbf{W}$  is stored in the RRAM array and the input signal  $\mathbf{y}$  is translated as the voltages to be applied to the array. The elements (and signals) in real and imaginary domains are highlighted by different colours. The module performs the DFT over signal  $\mathbf{y}$  and the read drivers get the result  $\mathcal{F}(\mathbf{y}) = \mathbf{W}\mathbf{y}$ . The design of inverting amplifier is presented at the upper right corner. (b, c) In the experiment, the real mapping of the DFT matrix is scaled and programmed into two 64 × 64 RRAM arrays in our integrated RRAM chip: (b) conductance matrix and (c) corresponding error matrix, each element of which refers to the ratio (experimental conductance – target conductance)/target conductance [note: the value is not in percentage form].

and frequency domains involves IDFT/DFT operations. For the received block of symbols y, the DFT of which can be represented as an  $N_c$ -length vector:  $\mathcal{F}(\mathbf{y}) = \mathbf{W}\mathbf{y}$ , where  $\mathcal{F}(\cdot)$ denotes the DFT operation and W is the DFT matrix. In the circuit design, the real mapping of DFT matrix,  $\mathcal{R}(\mathbf{W})$ , is scaled into the RRAM devices' conductance range and stored as the difference between two arrays. The received signal y is translated to the input voltages  $\mathcal{T}(\mathbf{y})$  for the array. The module computes the DFT of y, and the current outputs are the scaled real vector mapping  $\mathcal{T}(\mathcal{F}(\mathbf{y}))$ . The detailed discussion on the hardware implementation of this module is provided in Appendix B. Compared with conventional approaches based on fast Fourier transform (FFT) algorithms [50], the RRAMbased design features the dramatic reduction of computational complexity of from  $O(N_c \log N_c)$  for FFT to just a one-step (i.e., O(1)) operation. This makes it possible to overcome the bottleneck of high complexity of DFT in baseband processing for the next-generation large-scale OFDM communications.

In this section, a single-antenna OFDM system with 32 subcarriers is demonstrated. The conductance mapping of the DFT matrix to RRAM array is scaled to fit the RRAM devices' conductance range, which are programmed into two arrays.

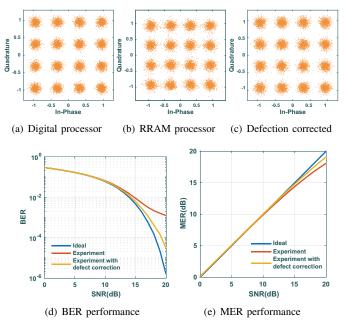

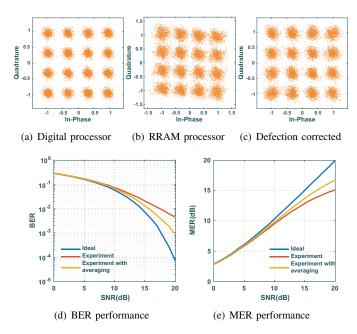

Figure 4. Experimental performance of the DFT module in the demonstrated OFDM system. At the receiver, the constellation diagram is recovered using (a) digital processor, (b) the RRAM processor experimental results, (c) RRAM processor results compensated by defective correction. (d, e) Communication performance of digital processor, RRAM-implemented DFT and defection corrected RRAM-DFT under different channel conditions.

The subtraction of the conductance matrices of these two arrays, in the form of differential pairs, and the corresponding error matrix are presented in Fig. 3(b) and Fig. 3(c). The complete signal processing path in the prototypical RRAMbased OFDM system is described as follows. For the transmitter, a message in bits is firstly modulated into 16-QAM symbols, and then transformed from the frequency domain into the time domain by IDFT. After adding a cyclic prefix, the OFDM symbols are transmitted over the channel towards the receiver. At the receiver, after removing the cyclic prefix, the RRAM-based DFT is performed to transform the received signal back to the frequency domain, where the symbols are then demodulated into bits to recover the message. The performance of the receiver with RRAM-based DFT module is experimentally characterized over the wireless channel of receive signal-noise-ratio (SNR) being 20dB. As a benchmark, the constellation diagram recovered by the digital processor using a double-precision floating-point DFT matrix is shown in Fig. 4(a). In this case, the distortion of demodulated symbols is measured by MER 20dB at which no bit errors occur. For our RRAM-implemented DFT prototype, the measured constellation diagram is shown in Fig. 4(b) with MER dropping to 18dB while the BER growing to 0.00146. The communication performance is affected by both the channel noise and RRAM devices' imperfections. Compared with the results from a digital processor, the performance loss of our experimental RRAM-implemented DFT module comes from the imperfections of RRAM devices in the array, including defections and programming errors. To reveal the effect of the defective devices, we compensate the defections by post-processing. To be specific, we define the defection matrix  $\mathbf{W}_{\mathrm{defection}}$  as the compensatory conductance matrix of stuck-on and stuck-off RRAM devices. We then perform the multiplication operation  $\mathbf{W}_{\mathrm{defection}}\mathbf{y}$  in computer and add the result into the experimental outcome to obtain the defection-corrected result:  $\mathbf{x} = \mathbf{W}_{\mathrm{RRAM}}\mathbf{y} + \mathbf{W}_{\mathrm{defection}}\mathbf{y}$ . Leveraging this method, we rectify the experimental constellation diagram from RRAMimplemented DFT module as shown in Fig. 4(c), whose BER is ameliorated by an order of magnitude. Moreover, we explore the performance of our design with different transmission powers (i.e., different SNRs) as shown in Fig. 4(d) and Fig. 4(e). We observe that the performance differences between digital processor and our experimental RRAM-implemented DFT module are insignificant for a noisy channel. However, the differences can be noticeable for cleaner channels where the imperfections of RRAM devices in the array deteriorate the communication performance. The defective devices play a destructive role in the baseband processing and tackling this issue brings benefit to the enhancement of performance.

# IV. MULTIPLE-INPUT AND MULTIPLE-OUTPUT **DETECTION MODULE**

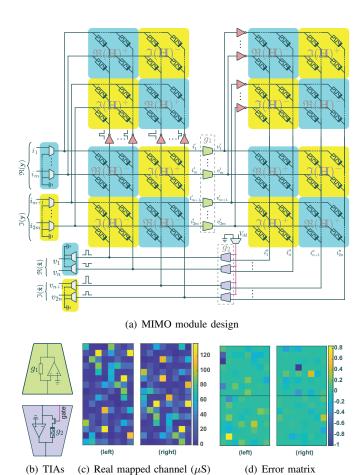

The RRAM-based MIMO detection module is illustrated in Fig. 5(a) and Fig. 5(b), which spatially multiplexes multiple parallel data-streams. This scales up the system throughput since different symbols are simultaneously transmitted over different antennas. Exploiting the unique channel between each pair of transmit and receive antennas allows each transmitted symbol to be recovered through the module of MIMO detection. In practice, two linear detectors are widely used, namely linear minimum mean square error (L-MMSE) and zero forcing (ZF) detectors. They reverse the signal distortion by propagation through a MIMO channel by channel equalization. To be specific, given the channel matrix H, the L-MMSE detector minimizes the mean squared error in the estimate of x among all linear detectors. The recovered signal vector is given by  $\hat{\mathbf{x}} = \left(\mathbf{H}^{\mathsf{H}}\mathbf{H} + \frac{1}{\mathsf{SNR}}\mathbf{I}\right)^{-1}\mathbf{H}^{\mathsf{H}}\mathbf{y}$ , where  $\mathbf{y}$  is the received signal vector at the receiver. In hardware implementation, the equivalent real-value channel matrix  $\mathcal{R}(\mathbf{H})$ is scaled and written into the RRAM arrays in the way as illustrated in Fig. 5(a), and the received signal y is scaled and translated to the input voltages  $\mathcal{T}(\mathbf{y})$ . The output voltages are the real vector mapping  $\mathcal{T}(\hat{\mathbf{x}})$ , and the detailed analysis of this circuit is provided in Appendix C. To cope with heterogeneous propagation environments with different SNRs, the feedback conductance of operational amplifiers can be represented using a RRAM device as shown in Fig. 5(b). Our design also applies to ZF detection (see Appendix C) which solves the least square problem and gives the recovered signal vector as  $\hat{\mathbf{x}} = (\mathbf{H}^H \mathbf{H})^{-1} \mathbf{H}^H \mathbf{y}$ . As shown in Fig. 5(b), the transistor dictates whether L-MMSE or ZF is applied. If the channel matrix is square, i.e.,  $N_t = N_r = N$ , the computational complexity of conventional matrix inversion is  $O(N^3)$ . The complexity increases rapidly as the number of transmit/receive antennas grows. On the contrary, the proposed MIMO detection performs the computation in just a single step (i.e., O(1)), presenting a promising solution for efficient detection in the 6G massive MIMO communication.

Figure 5. Multiple-input and multiple-output modules. (a) The architecture of RRAM-based MIMO detection module. The channel matrix H is stored in the four RRAM arrays as marked in the figure and the input signal y is scaled and translated as the input currents. The elements (and signals) in real and imaginary domains are highlighted by different colours. (b) The transistor controls whether L-MMSE or ZF modules is adopted. When the gate is grounded, the circuit performs ZF detection. Otherwise, L-MMSE is selected. In addition, to adapt to environments with different SNRs, the feedback conductance of the operational amplifiers is tuneable. (c, d) In the experiment, the real mapped channel matrix is scaled and programmed into RRAM arrays in our integrated RRAM chip: (c) conductance matrix and (d) corresponding error matrix, each element of which refers to the ratio (experimental conductance - target conductance)/target conductance.

(d) Error matrix

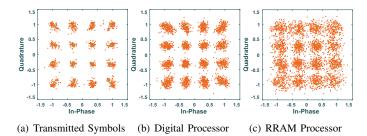

We experimentally demonstrated the RRAM-based narrowband MIMO system with 4 transmit antennas and 4 receive antennas. The real mapped channel matrix  $\mathcal{R}(\mathbf{H})$  is scaled and programmed into the RRAM arrays (see Fig. 5(c)). The programming error is presented in Fig. 5(d). The experimental results of the constellation diagrams from L-MMSE detection for a noisy channel of SNR being 20dB. To begin with, the constellation diagram recovered by the digital processor is shown in Fig. 6(a) as a benchmark. For our RRAMimplemented MIMO detection module, the measured MER drops 4dB compared to the digital counterpart, inducing more bit errors (see Fig. 6(b)). The performance loss comes from the programming noise of RRAM devices whose effects on the circuit are twofold: i) the imprecision of the channel matrix representation; ii) the imbalance of the left and right channel matrices. To reduce the effect of the programming noise in RRAM devices, we use two RRAM devices to represent one

Figure 6. Experimental performance of the MIMO detection module in the demonstrated MIMO system. At the receiver, the constellation diagram is recovered using (a) digital processor, (b) RRAM-implemented MIMO detection module, (c) RRAM MIMO detection module averaged from two implementations. (d, e) Communication performance of digital processor, RRAM-implemented MIMO detection, and averaged RRAM-pair implementation under different channel conditions.

real value which supresses the variance of random noise. By this means, we find the dispersion of constellation points (see Fig. 6(c)) becomes less severe and the BER reduces by an order of magnitude. Furthermore, as shown in Fig. 6(d) and Fig. 6(e), we study the performance differences between digital processor and our RRAM-implemented MIMO detection module under different channel conditions. We observe subtle differences between them in the low SNR regime while the divergence becomes noticeable in the high SNR regime. The performance loss of our RRAM-implemented MIMO detection module can be relieved by representing channel matrix using more RRAM devices to reduce the programming noise.

## V. CHANNEL ESTIMATION MODULE

To acquire the channel state information (CSI) needed for MIMO detection, the channel matrix is estimated at the receiver using pilot signals that are sent by the transmitter and known a priori to the receiver. Many data symbols can be transmitted between two pilot signals separated by channel coherent time, amortizing the overhead of channel training. A larger ratio between data and pilot symbols improves the system throughput at the cost of adaptive to time-varying channels. The transmitted training matrix  $\mathbf{P} \in \mathbb{C}^{N_t \times N_t}$  is known by the receiver, while the actual received matrix is  $\mathbf{S} \in \mathbb{C}^{\hat{N}_r \times N_t}$ . By choosing the pilot signal as a unitary matrix [51], i.e.,  $\mathbf{PP}^{H} = \mathbf{I}$ , the channel matrix estimated by maximum likelihood (ML) or least square (LS) is given as  $\hat{\mathbf{H}} = \mathbf{SP}^{\mathsf{H}}$ . In the RRAM-based channel estimation module, the real mapped training matrix  $\mathcal{R}(\mathbf{P})$  is stored in the RRAM array. Each row vector of the real mapped received

matrix  $\mathcal{R}(\mathbf{S})$  is translated to the supplied input voltages. The computation can be completed by  $2N_r$  read pulses while the complexity is  $O(N_rN_t^2)$  for traditional processors.

When ready, the row vectors of the estimated channel matrix are sequentially written into the RRAM array implementing the MIMO detector. We evaluate the performance of different writing process in terms of system latency. To this end, a mathematical model is developed to facilitate latency analysis for programming a 1T1R array as elaborated in Appendix E. Consider the writing process using a train of pulses to program an  $N \times N$  array in the row-by-row manner. It can be proved that the expected writing latencies of write-without-verification and write-with-verification schemes scale with the array size in the way no faster than  $O(N\sqrt{\ln N})$  and  $O(N\ln N)$ , respectively. This contributes to the most latency in our design. For comparison, the computational complexity is  $O(N^3)$  for traditional digital processors.

# VI. PERFORMANCE EVALUATION OF THE COMPLETE SYSTEM

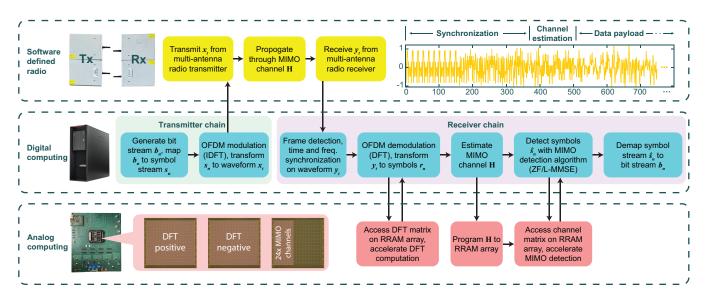

Recall that we consider the MIMO-OFDM air interface where a transmitter/receiver integrates the RRAM-based OFDM and MIMO modules. The modules are separately validated in previous sections. Here, we report a system-level demonstration of a MIMO-OFDM system with 32 sub-carriers and  $2 \times 2$  antennas for proof-of-concept. The RF chains are physically implemented using software defined radio (SDR) platform, which provides the realistic MIMO communication links over-the-air. The digital logic on a workstation regulates data generation, executes frame synchronization algorithms, orchestrates the operation of the other two platforms, and controls the system data flow. The system schematic is presented in Fig. 7. The workflow is described as follows. The workstation randomly generates bit stream and maps bits to symbols in 16-QAM constellation diagram. The symbols are then transformed to time domain waveforms by OFDM modulation, which are fed in the SDR transmitter to radiate the wireless signals at carrier frequency into the air by the two transmit antennas. The constellation diagram of symbols in the data payload when they are emitted from the transmitter is presented in Fig. 8(a). The dispersion of constellation points results from the thermal noise in transmitter circuit and the non-ideality of the RF components (e.g., nonlinear power amplifier response). The RF signal is captured by the two receive antennas at the SDR receiver, and downconverted to baseband signal with the locally generated carrier frequency. After that, the channel matrix is estimated using pilot symbols and programmed into RRAM arrays as mentioned. The data payloads are then processed using RRAMimplemented modules (i.e., DFT and MIMO detection), and the recovered constellation diagram is presented in Fig. 8(c) with MER being 12.83dB. For comparison, the constellation points from a digital baseband processor are given in Fig. 8(b) whose MER is 17.43dB. The performance loss of our RRAMimplemented system mainly comes from the defective RRAM devices and programming errors, which are compensatory as discussed. Our demonstration proves the feasibility of system-

Figure 7. Proof-of-concept in-memory baseband processing experiment. A small-scale MIMO-OFDM system (32 sub-carriers, 2 transmit and 2 receive antennas) is validated in the experiment using SDRs, workstation and RRAM crossbar arrays. A schematic of the experimental system is presented. The realistic communication system is realized by SDR platform. Our in-memory computing test board provides physical measurement for the computation of DFT and MIMO detection modules. The computer bridges different platforms and controls the dataflow.

Figure 8. Proof-of-concept in-memory baseband processing experimental results: (a) Constellation diagram of transmitted symbols. (b, c) Constellation diagrams of the symbols recovered at the receiver from (b) digital baseband processing and (c) RRAM-implemented in-memory baseband processing.

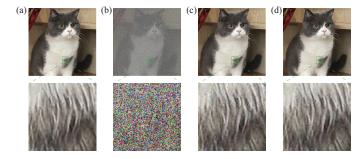

Figure 9. An illustration of the communication performance of transmitting an image over a noisy channel. (a) The original image. (b, c) The recovered images are from RRAM-based baseband processor where the RRAM arrays at the MIMO detector are programmed by (b) write-without-verification and (c) write-with-verification schemes. (d) Benchmark: software result.

level RRAM-based in-memory baseband processing in a real wireless communication system.

In the following, we perform the simulations of a large-scale RRAM-accelerated communication system corresponding to the standard of 5G new radio (NR) (see Table I). The simulation of RRAM array programming is based on the

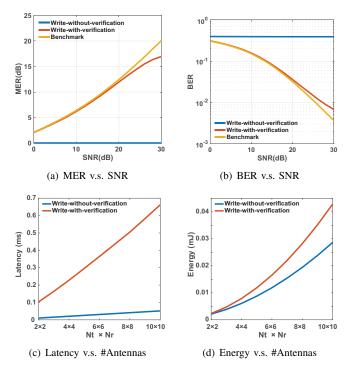

RRAM model calibrated using the experimentally acquired device properties such as the Ohmic behaviour (see Fig. 2(f)) and the evolution of the conductance with voltage pulses (see Fig. 2(g)). Both the cycle-to-cycle variations and read noise during RRAM programming are included in our simulations. Since the transmitter is much simpler than the receiver, we focus on the RRAM-based receiver in the remainder of this section. To visually demonstrate the performance of our designed in-memory baseband processor, we consider the specific task of uncoded transmission of an image as shown in Fig. 9(a). The image recovered at the receiver are presented in Fig. 9(b) and Fig. 9(c) where RRAM devices are programmed using writing without and with verification schemes, respectively. As a benchmark for comparison, the image resulting from a digital baseband processor is shown in Fig. 9(d). One can observe that the performance of the write-without-verification scheme is poor while the other scheme with verification performs similarly as the ideal processor. To quantify the performance, we present the relation between MER (and BER) and SNR for both schemes as shown in Fig. 10(a) (and Fig. 10(b)). The simulation results are aligned with the earlier observation and show that write-with-verification scheme outperforms the other in terms of communication performance. From the perspective of latency and energy efficiency, the performance is compared in Fig. 10(c) and Fig. 10(d). As shown in Table II, the throughput and energy-efficiency of the proposed RRAM-based in-memory baseband processing exceed those of any reported CMOS-based digital processors [52]-[56]. For example, under the specifications in Table I, the throughput and energy efficiency can achieve up to 160.8Gb/s and 4637Gb/J, exceeding state-of-the-art digital counterparts in the literature by more than  $329 \times$  and  $671 \times$ , respectively. Moreover, by reasonable conversion, our design is estimated to supports a throughput 91.2× higher than one of the stateof-the-art commercial modems, i.e., Qualcomm Snapdragon

Table I

PARAMETERS FOR LARGE-SCALE MIMO-OFDM SYSTEM SIMULATION

| Parameter | # sub-carriers | # Tx antennas | # Rx antennas | # Pilot symbols | # Symbols/frame |

|-----------|----------------|---------------|---------------|-----------------|-----------------|

| Notation  | $N_c$          | $N_t$         | $N_r$         | $N_t$           | M               |

| Value     | 1024           | 4             | 4             | 4               | 14×160          |

Table II

COMPARISON WITH CMOS-BASED DIGITAL PROCESSORS

| Processor                                                                   | Technology | Latency (ms) | Energy<br>(mJ) | Communication<br>Throughput (Gb/s) | Energy<br>Efficiency (Gb/J) |

|-----------------------------------------------------------------------------|------------|--------------|----------------|------------------------------------|-----------------------------|

| Qualcomm<br>Snapdragon X65 [52]                                             | 4 nm       | <10          | N/A            | <5                                 | N/A                         |

| TMS320C6678<br>8-core digital signal processor [53]                         | 20 nm      | 589.9        | 6548           | 0.0621                             | 0.0056                      |

| Domain adaptive processor 16×DAP in literature [54]                         | 12 nm      | 74.95        | 6547           | 0.4888                             | 0.0056                      |

| Combined digital baseband modules:<br>FFT in [55] and MIMO detector in [56] | 65 nm      | 50.17        | 5.3024         | 0.7303                             | 6.9091                      |

| Proposed RRAM-based<br>Baseband Processor                                   | -          | 0.2278       | 0.0079         | 160.8                              | 4637                        |

Table III

PARAMETERS OF MEMRISTORS' BEHAVIORAL MODELS FOR THE SIMULATIONS

| Memristor Device                           | Mechanism | Pulse<br>width  | State<br>number | Cycle-to-cycle vatiation | $G_{ m max}/G_{ m min}$ | Operation voltages     |

|--------------------------------------------|-----------|-----------------|-----------------|--------------------------|-------------------------|------------------------|

| Ta/TaO <sub>x</sub> /Pt<br>our RRAM        | Filament  | 10 ns           | 256             | 4.41% (P)<br>5.44% (D)   | 230.99/79.93 μS         | 0.65/-0.575 V          |

| TiN/HZO/SiO <sub>2</sub> /Si<br>FeFET [57] | FeFET     | 75 ns           | 32              | 0.5%                     | 1.79/0.04 μS            | 3.65/-2.95 V           |

| Ag/PZT/Nb:SrTiO <sub>3</sub><br>FTJ [58]   | FTJ       | 10 ns<br>630 ps | 256<br>150      | 2.06%<br>3.65%           | 80/1 μS<br>27.5/1 μS    | 1.675/-3.5 V<br>4/-5 V |

X65. Underpinning the improvements is the ultra-fast onestep baseband processing after channel estimation such that the baseband latency mostly comes from programming the RRAM arrays of MIMO detection module at the beginning of the frame. In contrast, for CMOS-based digital processors, data symbols are processed by executing the DFT (or FFT) and MIMO-detection algorithms using digital logic circuits, both suffering from high complexity as discussed. Next, there exists a tradeoff between communication performance and latency, i.e., higher performance requires better programming accuracy and thus longer latency. On the one hand, the write-withoutverification scheme shows lower latency but poor communication performance in terms of BER and MER, a result of the intrinsic stochasticity of RRAM. On the other hand, RRAM with more states can achieve higher precision but possibly more pulses are needed to reach the target conductance value.

# VII. DISCUSSION

This work demonstrates the feasibility of UFEE MIMO-OFDM baseband processing by leveraging the emerging inmemory computing technology based on RRAM arrays. The processing latency and energy are mostly contributed by the programming of the RRAM arrays for MIMO detection due to periodic channel estimation, while the following processing of data symbols can be completed in one-step. These advantages promise a feasible approach for realizing UFEE baseband processing. It shall be also emphasized that the proposed in-memory baseband processing not only works on RRAM but can be readily applied to other emerging in-memory

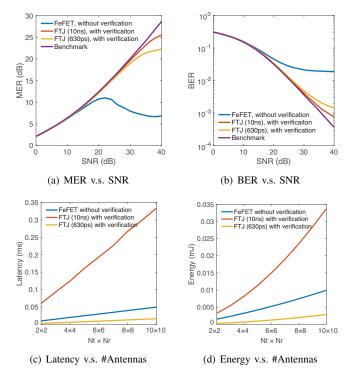

computing technologies including phase change, ferroelectric and magnetoresistive memories, as detailed in Table III which lists the device features of our experimental RRAM devices and other types of memristor. There are some observations from the simulation results in Fig. 11. First, we compared two different schemes for updating memristor arrays: writing with and without verification, elucidating the importance of verification and low cycle-to-cycle variation in ensuring the accuracy of the operations. To ensure satisfactory communication performance, write-with-verification is suggested for updating the memristor arrays even if the cycle-to-cycle variation is relatively small (e.g., ~0.5%) as shown in the simulation result of programming ferroelectric FET (FeFET) [57] without verification. Second, memristor can be further improved using ultra-narrow pulse width along with relatively large number of states to achieve ultra-fast conductance updates without compromising the communication performance. For example, the simulation results in Fig. 11 show that the UFEE requirements can be met using ferroelectric tunnel junction (FTJ) which is reported for high precision attainable using sub-nanosecond pulses [58]. Leveraging the behavioural model of such memristors, the latency of our in-memory baseband processing system can be reduced to the scale of several microseconds and the energy consumption to the scale of several micro-Jules, which meets the UFEE requirements of 6G communications. Furthermore, in-memory baseband processing is more effective for applications with less stringent precision requirements. For example, if the transmitted messages, such as images, are inputs to the downstream neural networks for inference,

Figure 10. Performance evaluation of in memory MIMO-OFDM baseband processing using experimental RRAMs. The simulations target a large-scale MIMO-OFDM system of 1024 sub-carriers, 4 transmit antennas and 4 receive antennas unless specified otherwise. The behavioural model of RRAM devices comes from the experimental testing of our fabricated RRAM devices. The simulation curves are averaged over 200 trials to eliminate the randomness of channel and RRAM devices. (a, b) Under different channel conditions, the resultant (a) MER and (b) BER from the three schemes. (c, d) For writing with and without verification schemes, the (c) latency and (d) energy are evaluated in terms of different MIMO sizes.

the models' robustness against programming noise can ensure high classification accuracy. Overall, developing the proposed in-memory baseband processing into a versatile technology is believed to provide a feasible approach for realizing the 6G vision on supporting future services and applications with extremely low latency and high energy-efficiency.

#### **APPENDIX**

## A. RRAM Device Fabrication and Integration

The integrated chip platform is comprised of three  $64 \times 64 \text{ Ta/TaO}_x/\text{Pt}$  RRAM crossbar arrays, together with digital control and analogue sensing circuits to realize in-memory computing. The driving and sensing analogue circuits are taped out with TSMC's 180nm technology node. After the integration of the RRAM devices with the CMOS circuits, the chip is wire-bonded in a package. The RRAM devices have a lateral dimension of 50nm  $\times$  50nm, fabricated in house with back-end-of-line (BEOL) processes. The layers of the RRAM materials stack (Ta/TaO $_x/\text{Pt}$ ) are deposited with room temperature sputtering, and the electrodes are patterned with electron-beam lithography. The deposited TaO $_x$ , serving as the switching layer, has a thickness of  $\sim$ 2nm.

## B. DFT/IDFT Circuit

Consider the circuit with DFT matrix  $\mathbf{W} \in \mathbb{C}^{N_c \times N_c}$ . The real mapping of the DFT matrix  $\mathcal{R}(\mathbf{W}) \in \mathbb{R}^{2N_c \times 2N_c}$  is scaled

Figure 11. Performance evaluation of in memory MIMO-OFDM baseband processing using memristors in the literature. For the three memristor behavioural models, the (a) latency and (b) energy are evaluated in terms of different MIMO sizes. Under different channel conditions, the resultant (c) MER (in dB) and (d) BER are shown.

into the RRAM devices' conductance range by a scaling factor  $\alpha$ , giving the conductance matrix  $\mathbf{G} = \alpha \mathcal{R}(\mathbf{W}) \in \mathbb{R}^{2N_c \times 2N_c}$ . The real conductance matrix  $\mathbf{G}$  is implemented by the difference between a pair of conductance arrays,  $\mathbf{G}^+ - \mathbf{G}^-$ , with the utilization of inverting amplifier to invert the voltages. The received signal  $\mathbf{y} \in \mathbb{C}^{N_c \times 1}$  is translated to the input voltages with the real vector mapping, such that  $\mathbf{v} = \mathcal{T}(\mathbf{y}) \in \mathbb{R}^{2N_c \times 1}$ . Leveraging Ohm's law (i.e., current = conductance  $\times$  voltage), the multiplications  $\{G_{kl}^+ v_l\}$  and  $\{G_{kl}^- v_l\}$  are achieved. Then, Kirchhoff's current law sums these contributions along each row line and the read circuit integrates all the signals, giving the current at the k-th column  $i_k = \sum_{l=1}^L (G_{kl}^+ - G_{kl}^-) v_l$ . Therefore, the output currents at the read circuit give the result:  $\mathbf{i} = (\mathbf{G}^+ - \mathbf{G}^-)\mathbf{v}$ , which gives the DFT result  $\alpha \mathcal{T}(\mathbf{x}) = \alpha \mathcal{R}(\mathbf{W}) \mathcal{T}(\mathbf{y})$ . Since DFT matrix is unitary, i.e.,  $\mathbf{W}^{-1} = \mathbf{W}^{\mathsf{H}}$ , IDFT module circuit is the same as that of DFT when we replace  $\mathcal{R}(\mathbf{W})$  with  $\mathcal{R}(\mathbf{W})^{\mathsf{T}}$ .

## C. L-MMSE/ZF MIMO Detector Circuit

Consider the L-MMSE detection circuit with channel matrix  $\mathbf{H} \in \mathbb{C}^{N_r \times N_t}$ . The real mapped channel matrix  $\mathcal{R}(\mathbf{H}) \in \mathbb{R}^{2N_r \times 2N_t}$  is scaled into the RRAM devices' conductance range by a scaling factor  $\alpha$ , giving the conductance matrix  $\mathbf{G} = \mathbf{G}^+ - \mathbf{G}^- = \alpha \mathcal{R}(\mathbf{H}) \in \mathbb{R}^{2N_r \times 2N_t}$  which is implemented as the difference between two RRAM arrays. The real vector mapping of the received signal  $\mathcal{T}(\mathbf{y}) \in \mathbb{R}^{2N_r \times 1}$  is translated to input currents. To make the voltages in the circuit within a reasonable range, the input currents are also scaled as

$\mathbf{i} = \alpha \mathcal{T}(\mathbf{y}) \in \mathbb{R}^{2N_r \times 1}$ . The two arrays at the left-hand side constitute the conductance matrix  $-\mathbf{G} = \mathbf{G}^- - \mathbf{G}^+$ with voltages v supplied at the bottom of the nether array. The Kirchhoff's current law sums the output currents from the left RRAM array pair, -Gv, and the input currents, i, such that the input currents at the operational amplifiers are i' = -Gv + i. Hence, the output voltages that supplied to the right RRAM array pair are  $\mathbf{v}' = -\frac{\mathbf{i}'}{a_1} = \frac{\mathbf{G}\mathbf{v} - \mathbf{i}}{a_2}$ , where  $g_1$  is the feedback conductance of the TIAs. Then, the right RRAM array pair, whose conductance matrix is represented by  $\mathbf{G}^{\mathsf{T}} = (\mathbf{G}^{+} - \mathbf{G}^{-})^{\mathsf{T}}$ , performs the MVM computation and outputs the current vector  $\mathbf{i}'' = \mathbf{G}^\mathsf{T} \mathbf{v}' = \mathbf{G}^\mathsf{T} \frac{\mathbf{G} \mathbf{v} - \mathbf{i}}{\mathbf{c}}$ . The currents are applied to the other set of TIAs, so that  $\mathbf{i}'' = -g_2\mathbf{v}$ , where  $g_2$  is the feedback conductance of the TIAs in this set. Accordingly, one can observe the relation:  $\mathbf{G}^{\mathsf{T}} \frac{\mathbf{G} \mathbf{v} - \mathbf{i}}{g_1} = -g_2 \mathbf{v}$ , which gives the output voltages  $\mathbf{v} =$  $(\mathbf{G}^{\mathsf{T}}\mathbf{G} + g_1g_2\mathbf{I})^{-1}\mathbf{G}^{\mathsf{T}}\mathbf{i}$ . By setting the SNR as  $\alpha^2(g_1g_2)^{-1}$ , the designed L-MMSE circuit outputs the desired vector:  $\mathcal{T}(\hat{\mathbf{x}}) = \left(\mathcal{R}(\mathbf{H})^{\mathsf{T}}\mathcal{R}(\mathbf{H}) + \frac{1}{\mathsf{SNR}}\mathbf{I}_{2N_t \times 2N_t}\right)^{-1}\mathcal{R}(\mathbf{H})^{\mathsf{T}}\mathcal{T}(\mathbf{y})$ . When the feedbacks of the TIAs in the second set are open, i.e.,  $g_2 = 0$ , the output voltages of the circuit are  $\mathbf{v} = (\mathbf{G}^\mathsf{T}\mathbf{G})^{-1}\mathbf{G}^\mathsf{T}\mathbf{i}$ . This computes the ZF and gives the desired vector  $\mathcal{T}(\hat{\mathbf{x}}) = (\mathcal{R}(\mathbf{H})^T \mathcal{R}(\mathbf{H}))^{-1} \mathcal{R}(\mathbf{H})^T \mathcal{T}(\mathbf{y}).$

# D. Implementing Complex Matrices and Vectors

Both the channel entries and signals are in the complex domain while employing differential pairs of RRAM devices can only represent real numbers. To address this issue, we propose to apply the equivalent matrices and vectors of real entries instead. Inspired by the matrix representation of complex numbers, i.e., the mapping  $a+b\mathrm{j}\to\begin{pmatrix} a&-b\\b&a\end{pmatrix}$  is a ring isomorphism from the field of complex numbers to the ring of these matrices, we extend the method to complex matrices and define the mappings as follows.

**Definition 1.** (*Real Matrix Mapping*). Define the mapping  $\mathcal{R}$ :  $\mathbb{C}^{K \times L} \to \mathbb{R}^{2K \times 2L}$ , which transforms a complex matrix  $\mathbf{A} = \Re(\mathbf{A}) + \mathrm{j}\Im(\mathbf{A}) \in \mathbb{C}^{K \times L}$  into a real matrix  $\mathcal{R}(\mathbf{A}) \in \mathbb{R}^{2K \times 2L}$ :

$$\mathcal{R}(\mathbf{A}) = \begin{bmatrix} \Re(\mathbf{A}) & -\Im(\mathbf{A}) \\ \Im(\mathbf{A}) & \Re(\mathbf{A}) \end{bmatrix}. \tag{4}$$

The defined mapping preserves the basic operations of matrices (see Lemma 1), making it a feasible method for inmemory baseband processing implementation.

**Lemma 1.** (Properties of Equivalent Real Matrices). Some basic properties of the mapping  $\mathcal{R}$  defined in Definition 1 are described as follows. For any matrices  $\mathbf{A}, \mathbf{B} \in \mathbb{C}^{K \times L}$ ,  $\mathbf{C} \in \mathbb{C}^{L \times N}$ ,

$$\mathcal{R}(\mathbf{A}) + \mathcal{R}(\mathbf{B}) = \mathcal{R}(\mathbf{A} + \mathbf{B}), \tag{5}$$

$$\mathcal{R}(\mathbf{A})\mathcal{R}(\mathbf{C}) = \mathcal{R}(\mathbf{AC}),\tag{6}$$

$$\mathcal{R}(\mathbf{A}^{\mathsf{H}}) = \mathcal{R}(\mathbf{A})^{\mathsf{T}}.\tag{7}$$

The proof involves straightforward calculations of matrices and thus omitted for brevity. It can be inferred from the equation (6) that  $\mathcal{R}(\mathbf{A}^{-1}) = \mathcal{R}(\mathbf{A})^{-1}$  if  $\mathbf{A}$  is invertible. Given the mapping, the complex matrices can be written into the

RRAM arrays without specific changes or auxiliary circuits. On the other hand, the proposed method can be applied to complex vectors as well, where one complex vector  $\mathbf{x} \in \mathbb{C}^{K \times 1}$  is mapped to a real matrix  $\mathcal{R}(\mathbf{x}) \in \mathbb{R}^{2K \times 2}$ . Then the *matrix-vector multiplication* (MVM) can be achieved following equation (6). However, it takes two steps to complete the operation since  $\mathcal{R}(\mathbf{x})$  is a matrix with two columns. To further improve the computational efficiency, we propose to implement the complex vector, which is usually the input voltages/currents for RRAM array, using the following transformation.

**Definition 2.** (Real Vector Mapping). Define the mapping  $\mathcal{T}$ :  $\mathbb{C}^{K\times 1} \to \mathbb{R}^{2K\times 1}$ , which transforms a complex vector  $\mathbf{x} \in \mathbb{C}^{K\times L}$  into a real vector  $\mathcal{T}(\mathbf{x}) \in \mathbb{R}^{2K\times 1}$ :

$$\mathcal{T}(\mathbf{x}) = \begin{pmatrix} \Re(\mathbf{x}) \\ \Im(\mathbf{x}) \end{pmatrix}. \tag{8}$$

The proposed mappings in Definition 1 and 2 make it possible to realize one-shot MVM computation as shown below.

**Lemma 2.** (One-Shot MVM Operation Between Equivalent Real Matrix and Vector). For any matrix  $\mathbf{A} \in \mathbb{C}^{K \times L}$  stored in RRAM array and vector  $\mathbf{x} \in \mathbb{C}^{L \times 1}$  translated as supply voltages, one-shot MVM is realized by the relation:

$$\mathcal{T}(\mathbf{A}\mathbf{x}) = \mathcal{R}(\mathbf{A})\mathcal{T}(\mathbf{x}). \tag{9}$$

It is proved by checking the following two relations:

$$\Re(\mathbf{A}\mathbf{x}) = \Re(\mathbf{A})\Re(\mathbf{x}) - \Im(\mathbf{A})\Im(\mathbf{x})$$

and

$$\Im(\mathbf{A}\mathbf{x}) = \Im(\mathbf{A})\Re(\mathbf{x}) + \Re(\mathbf{A})\Im(\mathbf{x}).$$

Based on Lemmas 1 and 2, the following two useful equations can be obtained:

$$\mathcal{T}\left((\mathbf{A}^{\mathsf{H}}\mathbf{A})^{-1}\mathbf{A}^{\mathsf{H}}\mathbf{x}\right) = \left(\mathcal{R}(\mathbf{A})^{\mathsf{T}}\mathcal{R}(\mathbf{A})\right)^{-1}\mathcal{R}(\mathbf{A})^{\mathsf{T}}\mathcal{T}(\mathbf{x}). \tag{10}$$

$$(\mathbf{A}^{\mathsf{H}}\mathbf{A} + \lambda \mathbf{I})^{-1}\mathbf{A}^{\mathsf{H}}\mathbf{x} = \left(\mathcal{R}(\mathbf{A})^{\mathsf{T}}\mathcal{R}(\mathbf{A}) + \lambda \mathbf{I}\right)^{-1}\mathcal{R}(\mathbf{A})^{\mathsf{T}}\mathcal{T}(\mathbf{x}). \tag{11}$$

where  $\lambda$  is a constant. The above equations correspond to MIMO detection implementation.

# E. Latency Analysis

We aim at quantifying the latency of writing a MIMO channel matrix into a RRAM array in the row-by-row manner. In particular, the channel is assumed as Rayleigh fading while the RRAM array is comprised of 1T1R cells. Two writing schemes are analyzed: write-without-verification and write-with-verification.

1) Communication model: The input-output relation of a MIMO system with channel matrix  $\mathbf{H} \in \mathbb{C}^{N_r \times N_t}$  is described as

$$y = Hx + z, (12)$$

where  $\mathbf{x} \in \mathbb{C}^{N_t \times 1}$  and  $\mathbf{y} \in \mathbb{C}^{N_r \times 1}$  denote the transmit and receive symbols, respectively.  $\mathbf{z} \sim \mathcal{CN}(0, \sigma_n^2 \mathbf{I}_{N_r})$  represents the AWGN in propagation. We consider i.i.d. Rayleigh fading model, where the entries of the channel matrix  $\mathbf{H}$  follow i.i.d.

zero-mean complex Gaussian distribution. For any (i, j)-th element in matrix  $\mathbf{H}$ , we have  $H_{ij} \sim \mathcal{CN}(0, 2\sigma_h^2)$  where  $\Re(H_{ij}) \sim \mathcal{N}(0, \sigma_h^2)$  and  $\Im(H_{ij}) \sim \mathcal{N}(0, \sigma_h^2)$ .

The elements of channel matrix  $\{H_{ij}\}$  vary in the whole real domain. We need to scale them into the feasible conductance range for RRAM devices. For each RRAM device, the maximum and minimum values of working conductance are denoted by  $G_{\max}$  and  $G_{\min}$ , respectively. For convenience, we assume  $G_{\min}=0$  such that a differential pair of RRAM devices can represent a real number in the interval  $[-G_{\max}, G_{\max}]$ . In order to scale the channel matrix into this range, we apply the three-sigma rule:

$$\Pr(-3\sigma_h \le \Re(H_{ij}) \le 3\sigma_h) = 99.73\%,$$

(13)

$$\Pr(-3\sigma_h \le \Im(H_{ij}) \le 3\sigma_h) = 99.73\%.$$

(14)

Through this rule, we can guarantee the feasibility of representing channel matrix by a RRAM array with high probability. Accordingly, the variance of the channel elements as mentioned becomes  $\sigma_h = G_{\rm max}/3$ .

2) Model of RRAM device: To begin with, we focus on the RRAM device whose behavioral model is shown in Fig. 2(f) and Fig. 2(g). Consider the conductance update process using a train of write pulses. The pulse width is denoted as  $\Delta t_w$  which is a minuscule value. Cycle-to-cycle variation  $\sigma_c$  refers to the variation in conductance change at every write pulse. It is expressed as the percentage of the entire conductance range in the existing literature [59]–[62]. In other words, the standard variance of the per-cycle write noise,  $\mathcal{N}(0,\sigma_c^2)$ , is presented by  $\sigma_c = \gamma G_{\max}$  where  $\gamma \in (0,1)$  denotes the percentage. Then, we can characterize the per-pulse conductance change as follows:

$$\Delta G = \frac{G_{\text{max}} - G_{\text{min}}}{N_p} + \frac{\sigma_c}{\sqrt{\Delta t_w}} \Delta W, \tag{15}$$

where  $\Delta G = G(t+\Delta t_w) - G(t)$  is the conductance change by applying one write pulse over G(t),  $N_p$  is pulse number corresponding to programming conductance from  $G_{\min}$  to  $G_{\max}$ , and  $\Delta W = W(t+\Delta t_w) - W(t)$  with W(t) being a Winner process:  $\Delta W \sim \mathcal{N}(0,\Delta t_w)$ . From (15), we know the following knowledge of the RRAM device's state after one pulse:

$$\mathbb{E}[G(t + \Delta t_w)|G(t)] = G(t) + \frac{G_{\text{max}} - G_{\text{min}}}{N_p \times \Delta t_w} \Delta t_w, \quad (16)$$

$$Var[G(t + \Delta t_w)|G(t)] = \left(\frac{\sigma_c}{\sqrt{\Delta t_w}}\right)^2 \Delta t_w.$$

(17)

By introducing the slope parameter  $\mu \triangleq \frac{G_{\max} - G_{\min}}{N_p \times \Delta t_w}$  and the diverting variance  $\sigma \triangleq \frac{\sigma_c}{\sqrt{\Delta t_w}}$ , the evolution of conductance state G(t) is characterized by the stochastic differential equation (SDE) given the initial state  $G_0$  (i.e., the conductance at the time t=0):

$$dG(t) = \mu dt + \sigma dW(t), \quad G(0) = G_0. \tag{18}$$

The solution of (18) gives an Itô process:

$$G(t) = G_0 + \mu t + \sigma \int_0^t dW(s).$$

(19)

3) Performance of RRAM device: Let  $p(g,t|G_0)$  represent the conditional probability density of G(t) given initial state  $G(0)=G_0$ . For the SDE specified in (18), the probability density of the solution satisfies the forward Kolmogorov equation (also known as Fokker-Planck equation) with the initial condition as follows:

$$\frac{\partial p(t,g)}{\partial t} = -\mu \frac{\partial p(t,g)}{\partial g} + \frac{\sigma^2}{2} \frac{\partial^2 p(t,g)}{\partial g^2},$$

$$p(0,g) = \delta(g - G_0),$$

(20)

where  $\delta(\cdot)$  is Dirac function. By solving the partial differential equation in (20), we obtain the following lemma.

**Lemma 3.** (*Probability Density*). The probability density for the conductance evolution G(t) is

$$p(t, g|G_0) = \frac{1}{\sqrt{2\pi\sigma^2 t}} \exp\left(-\frac{(g - \mu t - G_0)^2}{2\sigma^2 t}\right),$$

(21)

which gives the Gaussian distribution  $(G(t)|G_0) \sim \mathcal{N}(G_0 + \mu t, \sigma^2)$ .

The process  $\{G(t), t \geq 0\}$  is time homogeneous with independent increments. Without loss of generality, we assume the target conductance  $\bar{G}$  is larger than the initial state, i.e., the increment of conductance is positive:  $\Delta G \triangleq \bar{G} - G_0 \geq 0$ . The writing time is denoted as T, which aims at increasing the conductance by the amplitude of  $\Delta G$ .

## • Write-without-verification scheme

Given target conductance G and the increment  $\Delta G$ , the write latency of the RRAM device is determined by

$$T = \frac{\Delta G}{\mu}.$$

(22)

Meanwhile, the achieved conductance state G(T) is inaccurate, giving that

$$G(T) \sim \mathcal{N}\left(\bar{G}, \frac{\sigma^2 \Delta G}{\mu}\right).$$

(23)

## • Write-with-verification scheme

To achieve the target conductance  $\bar{G}$ , the read pulse is applied after each write pulse to monitor the evolution of conductance state G(t). We model it as the first passage time, which refers to the first time when the conductance state G(t) achieves the target value  $\bar{G}$ ,

$$T \triangleq \inf\{t \ge 0 : G(t) = \bar{G}\}. \tag{24}$$

By adding an absorbing boundary  $p(t, \bar{G}) = 0$  to the partial differential equation (together with the initial condition) in (20), we obtain the probability density of the first passage time as the solution of the boundary value problem.

**Lemma 4.** (First Passage Time Probability Density). The probability density of the first passage time with the target increment conductance  $\Delta G$  is given by

$$p(T|\Delta G) = \frac{\Delta G}{\sqrt{2\pi\sigma^2 T^3}} \exp\left(-\frac{(\Delta G - \mu T)^2}{2\sigma^2 T}\right), \quad (25)$$

which gives the inverse Gaussian distribution  $(T|\Delta G) \sim \mathcal{IG}\Big(\Delta G/\mu, (\Delta G/\sigma)^2\Big)$ .

4) Latency of RRAM array programming: We consider the latency of writing the real mapped channel matrix  $\mathcal{R}(\hat{\mathbf{H}})$  onto the 1T1R array in the row-by-row manner. For simplicity, we assume the array has been fully reset, i.e., all the RRAM devices are initialized with  $G_{ij}(0)=0, \ \forall (i,j).$  In this setting,  $G_{ij}^+$  will be updated if  $H_{ij}\geq 0$ , or  $G_{ij}^-$  will be updated otherwise. The conductance change of one device, e.g.,  $\Delta G_{ij}$  for the (i,j)-th device, follows the i.i.d. half-normal distribution over indices  $\forall (i,j)$ , giving that

$$\Delta G_{ij} \sim \left| \mathcal{N}\left(0, G_{\text{max}}^2/9\right) \right|, \quad i = 1, \dots, N_t, \ j = 1, \dots, N_r.$$

The matrix  $\mathcal{R}(\mathbf{H})$  has  $2N_r$  rows and it consists of two identical processes each with updating  $N_r$  rows. Thus, the expected latency of writing this matrix is

$$T_{\text{write}} = 2 \times \mathbb{E}\left[\sum_{i=1}^{N_r} T_i^{\text{row}}\right] = 2N_r \times \mathbb{E}[T_i^{\text{row}}],$$

(27)

where the expectation is taken over channel entries. One-row latency, say the *i*-th row, is determined by the RRAM device consuming the largest write time, that is

$$T_i^{\mathsf{row}} = \max_{1 \le j \le 2N_t} T_{ij},\tag{28}$$

where latencies  $\{T_{ij}\}$  refer to writing  $\Re(H_{ij'})$  and  $\Im(H_{ij'})$ ,  $j'=1,\cdots,N_t$  into the i-th row of RRAM array. Hence, latencies  $\{T_{ij}\}_{j=1}^{2N_t}$  are  $2N_t$  i.i.d. random variables.

## • Write-without-verification scheme

Recall that the write time of one RRAM device using write-without-verification scheme is determined by  $T=\Delta G/\mu$ . Thus, for the *i*-th row, the write time of the RRAM device at the *j*-th column follows the half-normal distribution, that is

$$T_{ij} \sim \left| \mathcal{N}\left(0, \frac{G_{\text{max}}^2}{9\mu^2}\right) \right|, \quad j = 1, \cdots, 2N_r.$$

(29)

where  $|\mathcal{N}(\cdot, \cdot)|$  denotes the half-normal distribution.

**Theorem 1.** (Expected Latency of Write-Without-Verification). Consider writing the scaled real mapped channel matrix into an 1T1R array row-by-row using write-without-verification scheme. The expected write latency is upper bounded by

$$T_{\text{write}} \le \frac{2\sqrt{2}G_{\text{max}}}{3\mu} N_r \left(\sqrt{\ln N_t} + \frac{1}{\sqrt{\pi} \ln N_t}\right). \quad (30)$$

*Proof:* Since  $T_i^{\text{row}} = \max_{1 \leq j \leq 2N_t} T_{ij}$ , the probability of  $T_i^{\text{row}}$  satisfies

$$\Pr\left(T_i^{\mathsf{row}} > t\right) = 1 - \Pr\left(\max_{1 \le j \le 2N_t} T_{ij} \le t\right)$$

$$= 1 - \left(1 - \Pr(T_{ij} > t)\right)^{2N_t}. \tag{31}$$

Applying Bernoulli's inequality, we know that

$$(1 - \Pr(T_{ij} > t))^{2N_t} \ge 1 - 2N_t \Pr(T_{ij} > t).$$

(32)

Thus, for the non-negative random variable  $T_i^{\mathsf{row}}$ , its expectation is expressed as

$$\mathbb{E}[T_i^{\mathsf{row}}] = \int_0^\infty \left(1 - \left(1 - \Pr(T_{ij} > t)\right)^{2N_t}\right) dt$$

$$\leq \varepsilon + \int_\varepsilon^\infty \left(1 - \left(1 - \Pr(T_{ij} > t)\right)^{2N_t}\right) dt$$

$$\leq \varepsilon + 2N_t \int_\varepsilon^\infty \Pr(T_{ij} > t) dt, \tag{33}$$

where the inequality holds for any positive constant  $\varepsilon>0$ . To obtain the probability  $\Pr(T_{ij}>t)$ , we introduce the *cumulative distribution function* (CDF) of  $T_{ij}$ , i.e.,  $F_{T_{ij}}(t)= \operatorname{erf}\left(\frac{3\mu t}{\sqrt{2}G_{\max}}\right)$ . To ease the notation, we denote the parameter  $\bar{\sigma}\triangleq \frac{G_{\max}}{3\mu}$ . Then the probability is given by

$$Pr(T_{ij} > t) = 1 - F_{T_{ij}}(t) = 2Q(t/\bar{\sigma}),$$

(34)

where  $Q(\cdot)$  is the Q-function. Leveraging the inequality  $Q(x) \geq \frac{1}{x\sqrt{2\pi}} \left(1 - \frac{1}{x^2}\right) e^{-x^2/2}$  for x>0, we have

$$\mathbb{E}[T_i^{\mathsf{row}}] \leq \varepsilon + 4N_t \int_{\varepsilon}^{\infty} Q\left(\frac{t}{\bar{\sigma}}\right) dt$$

$$= \varepsilon + 2\sqrt{\frac{2}{\pi}} N_t \bar{\sigma} \exp\left(-\frac{\varepsilon^2}{2\bar{\sigma}^2}\right) - 4N_t \varepsilon Q\left(\frac{\varepsilon}{\bar{\sigma}}\right)$$

$$\leq \varepsilon + 2\sqrt{\frac{2}{\pi}} N_t \frac{\bar{\sigma}^3}{\varepsilon^2} \exp\left(-\frac{\varepsilon^2}{2\bar{\sigma}^2}\right). \tag{35}$$

Substituting  $\varepsilon = \bar{\sigma}\sqrt{2 \ln N_t}$  into the inequality for  $N_t > 1$ , we obtain

$$\mathbb{E}[T_i^{\mathsf{row}}] \leq \bar{\sigma} \sqrt{2 \ln N_t} + \bar{\sigma} \sqrt{\frac{2}{\pi}} \frac{1}{\ln N_t}$$

$$= \frac{\sqrt{2} G_{\max}}{3\mu} \left( \sqrt{\ln N_t} + \frac{1}{\sqrt{\pi} \ln N_t} \right). \quad (36)$$

Finally, according to (27), the expected latency of updating the whole RRAM array is upper bounded by

$$T_{\text{write}} \le \frac{2\sqrt{2}G_{\max}}{3\mu} N_r \left(\sqrt{\ln N_t} + \frac{1}{\sqrt{\pi} \ln N_t}\right).$$

(37)

This completes the proof.

### • Write-with-verification scheme

Recall that the latency of writing one RRAM device, say the (i, j)-th device, in this scheme is determined by the first passage time with the compound distribution as follows:

$$T_{ij}|\Delta G_{ij} \sim \mathcal{I}\mathcal{G}\left(\Delta G_{ij}/\mu, (\Delta G_{ij})^2/\sigma^2\right),$$

$\Delta G_{ij} \sim |\mathcal{N}\left(0, G_{\max}^2/9\right)|.$  (38)

where  $\mathcal{IG}(\cdot,\cdot)$  and  $|\mathcal{N}(\cdot,\cdot)|$  denote the inverse Gaussian distribution and half-normal distribution, respectively.

**Theorem 2.** (Expected Latency of Write-With-Verification). Consider writing the scaled real mapped channel matrix into an 1T1R array row-by-row using

write-with-verification scheme. The expected write latency is upper bounded by

$$T_{\text{write}} \leq 2N_r \times \min \left\{ \frac{2\sqrt{2}G_{\text{max}}}{3\mu} \sqrt{\ln(4N_t)}, \frac{2\sigma^2}{\mu^2} \ln(4N_t) + \frac{G_{\text{max}}^2}{9\sigma^2} \right\}.$$

(39)

*Proof:* Recall that  $T_i^{\sf row} = \max_{1 \le j \le 2N_t} T_{ij}$  with i.i.d.  $\{T_{ij}\}_{j=1}^{2N_t}$ . Applying Jensen's inequality,

$$\exp(\varepsilon \mathbb{E}[T_i^{\mathsf{row}}]) \leq \mathbb{E}[\exp(\varepsilon T_i^{\mathsf{row}})]$$

$$= \mathbb{E}\left[\max_{1 \leq j \leq 2N_t} \exp(\varepsilon T_{ij})\right]$$

$$\leq \sum_{j=1}^{2N_t} \mathbb{E}\left[\exp(\varepsilon T_{ij})\right]$$

$$= 2N_t \mathbb{E}\left[\exp(\varepsilon T_{ij})\right], \tag{40}$$

where the expectation follows the rule of compound distribution, that is

$$\mathbb{E}\left[\exp(\varepsilon T_{ij})\right] = \mathbb{E}_{\Delta G_{ij}}\left[\mathbb{E}\left[\exp(\varepsilon T_{ij})|\Delta G_{ij}\right]\right]. \tag{41}$$

Given  $\Delta G_{ij}$ , the latency  $T_{ij}$  follows an inverse Gaussian distribution,  $T_{ij} \sim \mathcal{IG}\left(\frac{\Delta G_{ij}}{\mu}, \frac{(\Delta G_{ij})^2}{\sigma^2}\right)$ , whose moment-generating function (MGF) is

$$\mathbb{E}\left[\exp(\varepsilon T_{ij})|\Delta G_{ij}\right] = \exp\left\{\frac{\mu \Delta G_{ij}}{\sigma^2} \left(1 - \sqrt{1 - \frac{2\sigma^2 \varepsilon}{\mu^2}}\right)\right\}.$$

(42)

To ease the notation, we define

$$x(\varepsilon) \triangleq \frac{\mu}{\sigma^2} \left( 1 - \sqrt{1 - \frac{2\sigma^2 \varepsilon}{\mu^2}} \right),$$

(43)

which is an increasing function for  $\varepsilon \in (0, \frac{\mu^2}{2\sigma^2}]$ . Furthermore, we denote the standard variance of  $\Delta G_{ij}$  as  $\tilde{\sigma}$  whose value is  $\tilde{\sigma} = \frac{G_{\max}}{3}$ . Then, leveraging the MGF of the half-normal distribution,  $\Delta G_{ij} \sim |\mathcal{N}(0, \tilde{\sigma}^2)|$ , we have

$$\mathbb{E}[\exp(x(\varepsilon)\Delta G_{ij})] = \exp\left(\frac{\tilde{\sigma}^2 x(\varepsilon)^2}{2}\right) \left(1 + \operatorname{erf}\left(\frac{\tilde{\sigma} x(\varepsilon)}{\sqrt{2}}\right)\right).$$

(44)

From the relation  $\exp(\varepsilon \mathbb{E}[T_i^{\mathsf{row}}]) \leq 2N_t \mathbb{E}[\exp(\varepsilon T_{ij})] = 2N_t \mathbb{E}[\exp(x(\varepsilon)\Delta G_{ij})]$ , we have

$$\mathbb{E}[T_i^{\mathsf{row}}] \leq \frac{1}{\varepsilon} \ln(2N_t) + \frac{\tilde{\sigma}^2 x(\varepsilon)^2}{2\varepsilon} + \frac{1}{\varepsilon} \ln\left(1 + \operatorname{erf}\left(\frac{\tilde{\sigma} x(\varepsilon)}{\sqrt{2}}\right)\right). \tag{45}$$

It is not hard to prove the following facts:  $x(\varepsilon) \leq \frac{2}{\mu}\varepsilon$  and  $erf(\cdot) \leq 1$ , and thus we have

$$\mathbb{E}[T_i^{\mathsf{row}}] \le \frac{1}{\varepsilon} \ln(4N_t) + \frac{2\tilde{\sigma}^2}{\mu^2} \varepsilon, \tag{46}$$

which holds for any  $\varepsilon \in (0, \frac{\mu^2}{2\sigma^2}]$ . This indicates the expected one-row latency  $\mathbb{E}[T_i^{\text{row}}]$  is upper bounded by the minimum of the right-hand side of inequality (46).

1). If  $\ln(4N_t) \leq \frac{\mu^2}{2\sigma^2} \left(\frac{\tilde{\sigma}}{\sigma}\right)^2$ , the minimum value of the right-hand side of (46) is

$$\frac{1}{\varepsilon} \ln (4N_t) + \frac{2\tilde{\sigma}^2}{\mu^2} \varepsilon \ge 2\sqrt{\frac{1}{\varepsilon} \ln (4N_t) \cdot \frac{2\tilde{\sigma}^2}{\mu^2} \varepsilon}$$

$$= \frac{2\sqrt{2}G_{\text{max}}}{3\mu} \sqrt{\ln(4N_t)}, \quad (47)$$

and thus, we have

$$\mathbb{E}[T_i^{\mathsf{row}}] \le \frac{2\sqrt{2}G_{\max}}{3\mu} \sqrt{\ln(4N_t)}.\tag{48}$$

2). If  $\ln(4N_t) > \frac{\mu^2}{2\sigma^2} \left(\frac{\tilde{\sigma}}{\sigma}\right)^2$ , the minimum value of the right-hand side of inequality (46) is achieved at  $\epsilon = \frac{\mu^2}{2\sigma^2}$ , so that

$$\frac{1}{\varepsilon} \ln (4N_t) + \frac{2\tilde{\sigma}^2}{\mu^2} \varepsilon \ge \frac{2\sigma^2}{\mu^2} \ln(4N_t) + \left(\frac{\tilde{\sigma}}{\sigma}\right)^2$$

$$= \frac{2\sigma^2}{\mu^2} \ln(4N_t) + \frac{G_{\text{max}}^2}{9\sigma^2}, \quad (49)$$

and thus, we have

$$\mathbb{E}[T_i^{\mathsf{row}}] \le \frac{2\sigma^2}{u^2} \ln(4N_t) + \frac{G_{\max}^2}{9\sigma^2}.$$

(50)

By combining the results in the two cases, we have

$$\mathbb{E}[T_i^{\mathsf{row}}] \leq \begin{cases} \frac{2\sqrt{2}G_{\max}}{3\mu} \sqrt{\ln(4N_t)}, & \ln(4N_t) \leq \frac{\mu^2}{2\sigma^2} \left(\frac{G_{\max}}{3\sigma}\right)^2, \\ \frac{2\sigma^2}{\mu^2} \ln(4N_t) + \frac{G_{\max}^2}{9\sigma^2}, & \ln(4N_t) > \frac{\mu^2}{2\sigma^2} \left(\frac{G_{\max}}{3\sigma}\right)^2, \end{cases}$$

(51)

which can be easily verified that it is equivalent to

$$\mathbb{E}\left[T_{i}^{\mathsf{row}}\right] \leq \min\left\{\frac{2\sqrt{2}G_{\max}}{3\mu}\sqrt{\ln(4N_{t})}, \frac{2\sigma^{2}}{\mu^{2}}\ln(4N_{t}) + \frac{G_{\max}^{2}}{9\sigma^{2}}\right\}. \tag{52}$$

Finally, according to (27), the expected latency of updating the whole RRAM array is upper bounded by

$$T_{\text{write}} \leq 2N_r \times \min \left\{ \frac{2\sqrt{2}G_{\text{max}}}{3\mu} \sqrt{\ln(4N_t)}, \frac{2\sigma^2}{\mu^2} \ln(4N_t) + \frac{G_{\text{max}}^2}{9\sigma^2} \right\}.$$

(53)

This completes the proof.

## F. Comparison with Digital CMOS Counterpart

In this note, we provide the comparisons with the state-ofthe-art (SOTA) digital CMOS counterparts, which is important to highlight the advantages of our RRAM-based baseband processor in terms of latency (or throughput) and energy efficiency. The calculations are based on the parameters in the Table IV unless specified otherwise.

Table IV PARAMETERS FOR COMPARISON WITH CMOS-BASED DIGITAL PROCESSORS

| Parameter | DFT Size      | # Slots/Frame | Symbols/Slot | Modulation | Number of Antennas |

|-----------|---------------|---------------|--------------|------------|--------------------|

| Value     | 1024<br>2048* | 160           | 14           | 16-QAM     | 4×4<br>2×2+4×4*    |

\*2048 and  $2 \times 2 + 4 \times 4$  are only used for comparison with Qualcomm Snapdragon X65.

- 1) Comparison with SOTA commercial modem: SOTA commercial modems are fabricated using the latest technology node, targeting the 5G signal processing. Take the popular Qualcomm Snapdragon X65 modem as an example. It is fabricated using the TSMC 4nm process according to the public data [52]. The maximum download speed can achieve up to 10 Gb/s over mmWave and sub-6 carrier aggregation. Note that the modulation used in this product is 256-QAM (8 bits/symbol) while we used 16-QAM (4 bits/symbol) in this work for the demonstration of our RRAM-based design. Therefore, the top speed is reduced by half as we match the QAM order of the two processors for a fair comparison, resulting in a peak throughput of 5 Gb/s as benchmark. In addition, the throughput of X65 modem is the combination of two separate bands and specifications, i.e., mmWave (2  $\times$  2 MIMO) and sub-6 GHz (4  $\times$  4 MIMO). For the same communication overhead, the baseband processing latency of our design with the same parameters (2048-point DFT,  $2 \times 2$ MIMO +  $4 \times 4$  MIMO) is only 0.2409 ms by re-simulation. It means our design can support a communication throughput as large as 455.8 Gb/s, which is 91.2× higher than that of the SOTA (i.e., Snapdragon X65 modem). However, it is hard to scale the throughput to fit the other group of settings specified in Table 1 which are used for other baselines, so that we just summarize it as < 5 Gb/s in Table II, making it appear different from the values in other designs. On the other hand, the energy efficiency comparison is not feasible since the X65 modem is an integrated system-on-chip (SoC) that contains RFIC, control processor, digital baseband processor, and other units. Unfortunately, there is no detailed energy efficiency data related to baseband processing in this modem available in the public domain.

- 2) Comparison with multi-core digital signal processor (DSP) reported in literature: Next, we compare the proposed design with the reported powerful multi-core DSP in the literature, namely TMS320C6678 from Texas Instruments [53]. The performance achieves up to 128 GOPS while the average power consumption for the optimized digital processing function is 11.1 Watts. For fair comparison, we just take the power of this 8-core DSP into consideration while neglect the power of the development board TMDSEVM6678LE. The baseband processing workload is estimated by the algorithmic computation complexity, giving the value of 75.5 GOPs. Accordingly, the latency and energy consumption are calculated as 589.9 ms and 6.548 J, respectively. Meanwhile, ignoring the power of peripheral circuits, our RRAM-based design shows the latency and energy consumption being 0.2278 ms and 0.0079 mJ, and thus the equivalent computational throughput and energy efficiency are calculated as 331.4 TOPS and 9557 TOPS/Watt which outperforms this DSP by  $10^3$  and  $10^5$  times,

respectively.

- 3) Comparison with digital baseband processor reported in literature: Moreover, we compare the proposed design with the reported digital baseband processor in the literature. Since the design of traditional digital baseband processor is considered a matured area, there are few recent publications on the complete baseband system design. As a compromise, we provide the following two comparisons: a) one with the SOTA domain adaptive processor (DAP) for wireless communication; b) the other with "virtually assembled" digital baseband processor by combining the SOTA designs of isolated digital baseband modules (i.e., DFT, MIMO detection, etc.) collected from the recent literatures.