## Charge-trapping characteristics of fluorinated thin ZrO<sub>2</sub> film for nonvolatile memory applications

X. D. Huang, 1,a) R. P. Shi, 2 and P. T. Lai<sup>2,a)</sup>

<sup>1</sup>Key Laboratory of MEMS of the Ministry of Education, Southeast University, Nanjing 210096, China <sup>2</sup>Department of Electrical and Electronic Engineering, The University of Hong Kong, Pokfulam Road, Hong Kong, China

(Received 26 January 2014; accepted 15 April 2014; published online 24 April 2014)

The effects of fluorine treatment on the charge-trapping characteristics of thin  $ZrO_2$  film are investigated by physical and electrical characterization techniques. The formation of silicate interlayer at the  $ZrO_2/SiO_2$  interface is effectively suppressed by fluorine passivation. However, excessive fluorine diffusion into the Si substrate deteriorates the quality of the  $SiO_2/Si$  interface. Compared with the  $ZrO_2$ -based memory devices with no or excessive fluorine treatment, the one with suitable fluorine-treatment time shows higher operating speed and better retention due to less resistance of built-in electric field (formed by trapped electrons) against electron injection from the substrate and smaller trap-assisted tunneling leakage, resulting from improved  $ZrO_2/SiO_2$  and  $SiO_2/Si$  interfaces. © 2014 AIP Publishing LLC. [http://dx.doi.org/10.1063/1.4873388]

Metal-oxide-nitride-oxide-silicon (MONOS)-type nonvolatile memory with discrete traps in the dielectric for charge storage is considered as a promising candidate to replace its floating-gate counterpart due to stronger scaling ability and higher reliability. Recently, high-k dielectrics have been proposed instead of conventional Si<sub>3</sub>N<sub>4</sub> as charge-trapping layer (CTL) to achieve lower operating voltage and higher charge-trapping efficiency. 1-8 Among various high-k dielectrics, Hf-based oxides (e.g., HfO<sub>2</sub> and HfON) have been extensively investigated as CTL mainly because of its large conduction-band offset relative to SiO<sub>2</sub>  $(\Delta E_c \sim 2.0 \,\mathrm{eV})$ , high k value ( $\sim 22$ ), and compatibility with CMOS processing.<sup>2–4</sup> On the other hand, ZrO<sub>2</sub> shows similar dielectric properties as HfO<sub>2</sub> but has higher k value ( $\sim$ 37). Consequently, there is an increasing interest in exploring ZrO<sub>2</sub> as CTL.<sup>5,6</sup> Wu et al. studied the charge-trapping characteristics of ZrO2 with and without nitridation and found that MONOS device with nitrided ZrO<sub>2</sub> showed better performance than that without nitridation due to nitrogen passivation of the ZrO<sub>2</sub> film. Besides nitrogen, fluorine is also an excellent passivant to remove oxide defects and strengthen the dielectric films due to its very high electronegativity. Therefore, fluorination is an effective way to improve the charge-trapping characteristics of dielectrics.<sup>7,8</sup> In this work, based on MONOS capacitors, the charge-trapping characteristics of ZrO2 with and without fluorine incorporation are studied. Detailed analysis of fluorine treatment on the device performance is also carried out.

MONOS capacitors with Al/Al<sub>2</sub>O<sub>3</sub>/ZrO<sub>2</sub>/SiO<sub>2</sub>/Si were fabricated on p-type (100) substrate. After the standard RCA cleaning, 2-nm SiO<sub>2</sub> tunneling oxide was grown on the wafers by thermal dry oxidation. Then 3-nm ZrO<sub>2</sub> was deposited on the SiO<sub>2</sub> by sputtering using a Zr target in an Ar/O<sub>2</sub> (8/1) mixed ambient. Following that, some samples were treated by a CHF<sub>3</sub> + O<sub>2</sub> (10 SCCM/1 SCCM) plasma at 20 W for 150 s and 400 s, respectively. The low-concentration O<sub>2</sub> was used to remove the carbon and hydrogen in the plasma. <sup>10</sup>

Then, 15-nm Al<sub>2</sub>O<sub>3</sub> was deposited by atomic layer deposition using trimethyl-aluminum (Al(CH3)<sub>3</sub>) and H<sub>2</sub>O as precursors at 300 °C. Following that, all the samples went through a post-deposition annealing in N<sub>2</sub> at 900 °C for 30 s. Finally, Al was evaporated and patterned as gate electrodes followed by a forming-gas annealing at 300 °C for 20 min. The sample without fluorine treatment was denoted as ZrO, while the samples with 150-s and 400-s fluorine treatment were denoted as LF-ZrO and HF-ZrO, respectively. In addition, Al/Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub>/Si (denoted as MAOS) and Al/ZrO<sub>2</sub>/SiO<sub>2</sub>/Si (denoted as MNOS) capacitors were also fabricated by the same process to study the charge-trapping characteristics of the ZrO<sub>2</sub> film. The physical properties of the films with and without fluorine treatment were analyzed by transmission electron microscopy (TEM), secondary ion mass spectroscopy (SIMS), and X-ray photoelectron spectroscopy (XPS). The electrical characteristics of the devices were measured by HP4284A LCR meter and HP4156A semiconductor parameter analyzer.

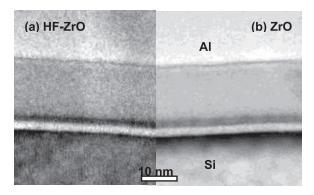

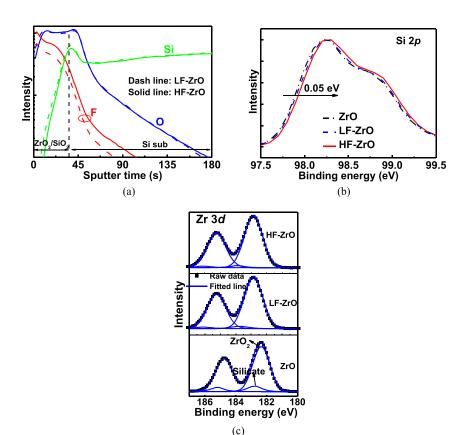

Fig. 1 shows the cross-sectional TEM image of the MONOS capacitors with and without the fluorine treatment, where the physical thickness remains the same after the fluorine treatment, indicating negligible etching of the ZrO<sub>2</sub> film due to the low energy of the fluorine plasma treatment. Fig. 2(a) displays the SIMS depth profile of the samples with various fluorine-treatment times to evaluate the fluorine distribution. It is clear that fluorine is mainly located in the ZrO<sub>2</sub>/SiO<sub>2</sub> stack and decreases rapidly in the Si substrate, indicating strong fluorine passivation in the ZrO<sub>2</sub>/SiO<sub>2</sub> stack. Also, the fluorine atoms diffuse more into the Si substrate for longer fluorine-treatment time. This is consistent with the XPS data in Fig. 2(b), where the Si 2p spectrum from the substrate for the HF-ZrO sample shifts to higher binding energy by 0.05 eV relative to those for the ZrO and LF-ZrO samples, implying the formation of Si-F bonds. Fig. 2(c) shows the Zr 3d spectrum combined with curve-fitting lines. For the ZrO sample, the Sr 3d spectrum displays distinct doublet at 184.7 eV (Zr  $3d_{3/2}$ ) and 182.3 eV (Zr  $3d_{5/2}$ ), agreeing with Zr–O bonding in the ZrO<sub>2</sub> film. After the fluorine treatment,

a)Electronic addresses: eexdhuang@gmail.com and laip@eee.hku.hk

FIG. 1. Cross-sectional TEM image for (a) the HF-ZrO and (b) ZrO MONOS capacitors.

the spectrum shifts to higher binding energy by  $0.5\,\mathrm{eV}$ , indicating that F is bonded with Zr. Moreover, the Zr spectrum can be decomposed into two components, corresponding to  $\mathrm{ZrO}_2$  (182.3 eV for Zr  $3d_{5/2}$ ) and Zr silicate formed by the  $\mathrm{ZrO}_2/\mathrm{SiO}_2$  interfacial reaction (182.7 eV for Zr  $3d_{5/2}$ ). Compared with the ZrO sample, the much smaller area of the silicate component for the LF-ZrO and HF-ZrO samples indicates negligible formation of the Zr silicate interlayer due to sufficient fluorine passivation. The formation of the interlayer consumes the  $\mathrm{SiO}_2$  tunneling oxide, and also it has smaller bandgap ( $\sim 6.6\,\mathrm{eV}$ ) and more defects than thermally grown  $\mathrm{SiO}_2$  ( $\sim 8.9\,\mathrm{eV}$ ). Therefore, an abrupt interface without interlayer is desirable for good data retention.  $^{14}$

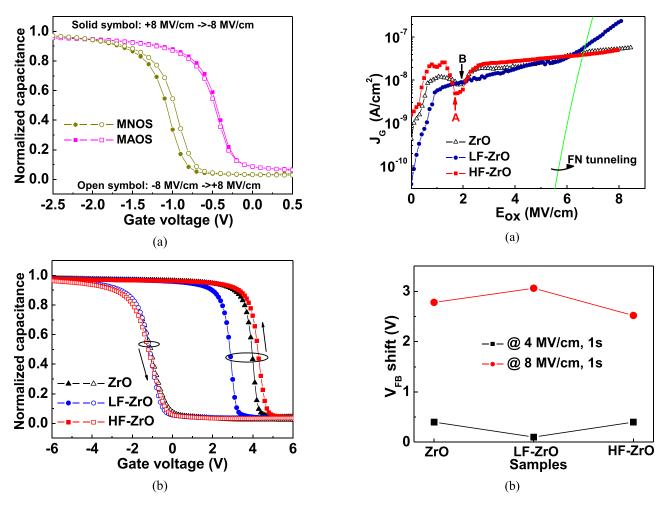

Fig. 3(a) displays the C-V loops under  $\pm 8\,\text{MV/cm}$  sweeping for the MAOS and MNOS samples. The trapped-charge density ( $Q_{ox}$ ) in the device can be calculated by the expression below

$$Q_{ox} \approx \frac{\Delta V_{FB} C_{ox}}{q},\tag{1}$$

where  $\Delta V_{FB}$  is the memory window from the C-V loops,  $C_{ox}$ is the capacitance density of the samples, and q is the electron charge. The  $Q_{ox}$  for the MAOS and MNOS samples is about  $3.5 \times 10^{10}\, cm^{-2}$  and  $1.1 \times 10^{12}\, cm^{-2}$ , respectively. The much higher Qox for the MNOS sample than that for the MAOS one at the same operating condition indicates that the charge-trapping site is mainly in the ZrO<sub>2</sub> layer. In addition, compared with the MAOS sample with counterclockwise hysteresis loop, the MNOS one exhibits a clockwise hysteresis loop, suggesting that charges inject from the Al electrode into the ZrO2 layer at the forward sweeping (from -8 MV/cm to +8 MV/cm) mainly due to the smaller barrier height at the Al/ZrO<sub>2</sub> interface ( $\Delta E_C \sim 1.6 \, \text{eV}$  for Al/ZrO<sub>2</sub>;  $\sim$ 3.0 eV for Al/Al<sub>2</sub>O<sub>3</sub>). Fig. 3(b) depicts the 1-MHz C-V hysteresis loops of the MONOS devices, where the memory window for the ZrO, LF-ZrO, and HF-ZrO samples is 4.8 V, 3.8 V, and 5.1 V, respectively. The smaller window for the LF-ZrO sample than the ZrO sample is due to the suppressed formation of interlayer by fluorine passivation, <sup>13</sup> while the largest window for the HF-ZrO sample suggests extra traps generated by excessive fluorine treatment. The C-V curve of the HF-ZrO sample shows more severe stretch-out characteristic than the ZrO and LF-ZrO samples, implying its higher interface-state density (Dit) at the SiO2/Si interface. Using the Terman's method,  $^{16}$  the HF-ZrO sample has an extracted  $D_{it}$  of  $7.4\times10^{12}\,cm^{-2}$ , corresponding to 8.8% and 17.5%higher than the ZrO sample  $(6.8\times10^{12}\,\text{cm}^{-2})$  and the LF-ZrO sample  $(6.3 \times 10^{12} \text{ cm}^2)$ , respectively. Appropriate fluorine incorporation can passivate the SiO<sub>2</sub>/Si interface,

FIG. 2. (a) SIMS depth profile of  $ZrO_2/SiO_2$  on Si substrate with various fluorine treatments. (b) XPS Si 2p spectrum and (c) XPS Zr 3d spectrum for the samples with and without fluorine treatments.

FIG. 3. (a) 1-MHz C-V loops of the MNOS and MAOS devices under  $\pm 8$  MV/cm sweeping; (b) 1-MHz C-V loops of the MONOS devices under  $\pm 12$  V sweeping.

FIG. 4. (a)  $J_G$  as a function of  $E_{OX}$  for the MONOS capacitors. The simulated FN tunneling current through SiO<sub>2</sub> tunneling oxide is also shown. (b)  $V_{FB}$  shift at low (~4 MV/cm) and high (~8 MV/cm)  $E_{OX}$ .  $V_{FB}$  shift is defined as  $V_{FB} - V_{FB0}$ , where  $V_{FB}$  is the flat-band voltage under stress, and  $V_{FB0}$  is the flat-band voltage of the fresh device.

leading to the smallest D<sub>it</sub> for the LF-ZrO sample. However, owing to the high electronegativity of fluorine, excessive fluorine can distort and even cleave the Si-Si bonds at the interface to form dangling Si bonds and Si-F bonds (as demonstrated in Fig. 2), <sup>17,18</sup> resulting in the highest D<sub>it</sub> and thus the largest window for the HF-ZrO sample.

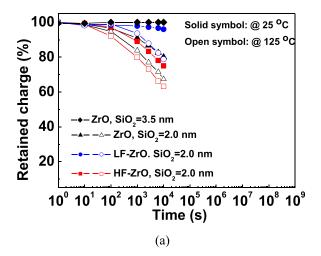

Fig. 4(a) displays the gate leakage ( $J_G$ ) of the MONOS devices as a function of electric field across  $SiO_2$  ( $E_{OX}$ ) by applying positive gate voltage ( $V_G$ ), corresponding to electron injection from the substrate. The LF-ZrO sample has a smaller leakage at low  $E_{OX}$  than the ZrO and HF-ZrO samples due to fewer traps at/near its interface and thus reduced trap-assisted tunneling. Moreover, the  $J_G$ - $E_{OX}$  curve of the HF-ZrO sample presents an obvious notch (denoted as A), where  $J_G$  decreases with  $E_{OX}$  and then increases again. This is associated with its high  $D_{it}$  at the  $SiO_2/Si$  interface. Due to Coulomb repulsion, electrons trapped by interface states can form a built-in electric field ( $E_{in}$ ) opposite to the external electric field  $E_{OX}$  induced by  $V_G$ , which is approximately given by

$$E_{in} \approx \frac{1}{4\pi\varepsilon} \frac{Q_{it}}{R^2},\tag{2}$$

where  $Q_{it}$  is the trapped charge;  $\varepsilon$  is the permittivity of the dielectric that  $E_{in}$  passes through; and R represents the

distance between the trapped-charge centroid and the substrate. E<sub>in</sub> tends to block the electron injection and also electrons filled in the shallow traps near the interface would flow back into the substrate due to Ein, both of which can offset the electron injection from the substrate. With increasing E<sub>OX</sub> and establishing a balance between electron trapping and de-trapping, J<sub>G</sub> increases with E<sub>OX</sub> again. A similar notch (denoted as B) is also observed for the ZrO sample due to high trap density at the ZrO<sub>2</sub>/SiO<sub>2</sub> interlayer and high D<sub>it</sub> at the SiO<sub>2</sub>/Si interface. On the contrary, no notch in the J<sub>G</sub>-E<sub>OX</sub> curve for the LF-ZrO sample suggests that its E<sub>in</sub> is weak and has little effect on electron injection, resulting from the suppressed formation of interlayer at the ZrO<sub>2</sub>/SiO<sub>2</sub> interface by the fluorine passivation as well as low Dit at the SiO<sub>2</sub>/Si interface by avoiding excessive fluorine diffusion to the Si substrate. For the ZrO and HF-ZrO samples, the traps generated by the Zr-silicate interlayer and high interface states lead to larger V<sub>FB</sub> shift (thus larger Q<sub>it</sub>) at low electric field as shown in Fig. 4(b). Moreover, these trapped charges at the ZrO<sub>2</sub>/SiO<sub>2</sub> and SiO<sub>2</sub>/Si interfaces make the trapped-charge centroid closer to the substrate compared with those located in the ZrO<sub>2</sub> film, thus resulting in stronger E<sub>in</sub> against electron injection according to Eq. (2). This is consistent with the phenomenon that the J<sub>G</sub> of the LF-ZrO sample increases more rapidly with  $E_{OX}$  than those of the ZrO and HF-ZrO samples, which becomes more obvious as the Fowler-Nordheim (FN) tunneling current dominates  $J_G$  (FN current is exponentially proportional to electric field of  $E_{OX}$ - $E_{in}$ ). <sup>19</sup> It should be noted that the little impact of  $E_{in}$  on electron injection from the substrate is beneficial to supplying sufficient electrons for the memory device, thus contributing to the larger  $V_{FB}$  shift ( $\sim 3.1~V$  versus 2.8 V for ZrO, 2.5 V for HF-ZrO) at high electric field for the LF-ZrO sample in Fig. 4(b). On the other hand, small leakage at low electric field normally indicates suppressed trap-assisted tunneling under retention mode and thus is beneficial for data retention. Therefore, the steeper  $J_G$ - $E_{OX}$  characteristic of the LF-ZrO sample is desirable for memory device to achieve high operating speed as well as good data retention.

Fig. 5(a) displays the retention characteristics of the MONOS capacitors, and the retention data for the ZrO sample with thicker  $SiO_2$  tunneling layer ( $SiO_2 \sim 3.5$  nm) are also measured to study charge-loss paths under the retention mode. The ZrO sample with thicker  $SiO_2$  shows excellent data retention with no charge loss even after  $10^4$  s suggests that no charge loss happens through the  $Al_2O_3$  blocking layer mainly due to its high quality with negligible traps. Moreover, compared with the ZrO sample with thicker  $SiO_2$ , the ZrO one with thinner  $SiO_2$  ( $\sim 2.0$  nm) shows worse data

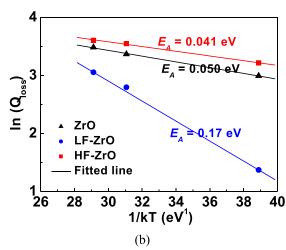

FIG. 5. (a) Data retention for the MONOS capacitors with an initial  $V_{FB}$  shift of 3.2 V. (b) Arrhenius plot of the retention property.

retention, indicating that the charge loss is mainly determined by the tunneling SiO<sub>2</sub> layer. As the operating temperature is raised from 25 °C to 125 °C, the charge-loss rate after 10<sup>4</sup> s (Q<sub>loss</sub>) increases from 3.9% to 21.2% for the LF-ZrO sample; For comparison, the corresponding Q<sub>loss</sub> increases from 19.9% to 32.6% and from 24.9% to 36.8% for the ZrO and HF-ZrO samples, respectively. The lower Q<sub>loss</sub> of the LF-ZrO sample demonstrates its better data retention. The activation energy EA of the charge loss is also extracted from the Arrhenius plot of the retention property in Fig. 5(b) to gain more insight on the charge-loss mechanism. The much smaller E<sub>A</sub> of the ZrO sample (0.041 eV) and HF-ZrO sample (0.050 eV) indicates that the charge-loss mechanism is mainly based on tunneling process. which hardly depends on temperature.<sup>20</sup> For the ZrO and HF-ZrO samples, the electrons trapped at the ZrO<sub>2</sub>/SiO<sub>2</sub> or SiO<sub>2</sub>/Si interface are close to the substrate, thus easily escaping back to the substrate, because the tunneling probability increases exponentially with decreasing barrier height and tunneling distance between the trapped electrons and the substrate. Also, the traps at the ZrO<sub>2</sub>/SiO<sub>2</sub> and SiO<sub>2</sub>/Si interfaces can act as a medium to facilitate the escaping of electrons from the CTL to the substrate by trap-assisted tunneling. On the contrary, the trapped electrons in the LF-ZrO sample cannot move easily by tunneling but have to be thermally activated to the conduction band of the CTL before tunneling to the substrate (due to the larger distance of the trapped charges in the ZrO<sub>2</sub> film from the substrate as well as high-quality ZrO<sub>2</sub>/SiO<sub>2</sub> and SiO<sub>2</sub>/Si interfaces), thus resulting in larger E<sub>A</sub>  $(\sim 0.17 \text{ eV})$  and better data retention.

In summary, the effects of fluorine treatment on the charge-trapping characteristics of thin  $ZrO_2$  film are investigated. Compared with the memory devices with no or excessive fluorine treatment, the one with suitable fluorine treatment time shows better characteristics due to suppressed interlayer growth by fluorine passivation of the  $ZrO_2/SiO_2$  interface and also fewer interface states by avoiding excessive fluorine diffusion to the substrate. Therefore,  $ZrO_2$  film with appropriate fluorine incorporation is a promising candidate as CTL for high-performance nonvolatile memory applications.

This work was financially supported by the CRCG Small Project Funding (No. 201209176095) of the University of Hong Kong.

<sup>&</sup>lt;sup>1</sup>T. M. Pan, J. S. Jung, and F. H. Chen, Appl. Phys. Lett. **97**, 012906 (2010).

<sup>&</sup>lt;sup>2</sup>H. W. You and W. J. Cho, Appl. Phys. Lett. **96**, 093506 (2010).

<sup>&</sup>lt;sup>3</sup>H. J. Yang, C. F. Cheng, W. B. Chen, S. H. Lin, F. S. Yeh, S. P. McAlister, and A. Chin, IEEE Trans. Electron Devices **55**, 1417 (2008).

<sup>&</sup>lt;sup>4</sup>J. Y. Wu, Y. T. Chen, M. H. Lin, and T. B. Wu, IEEE Electron Device Lett. **31**, 993 (2010).

<sup>&</sup>lt;sup>5</sup>Y. H. Wu, L. L. Chen, Y. S. Lin, M. Y. Li, and H. C. Wu, IEEE Electron Device Lett. **30**, 1290 (2009).

<sup>&</sup>lt;sup>6</sup>J. Liu, Q. Wang, S. B. Long, M. H. Zhang, and M. Liu, Semicond. Sci. Technol. **25**, 055013 (2010).

<sup>&</sup>lt;sup>7</sup>X. D. Huang, J. K. O. Sin, and P. T. Lai, IEEE Trans. Electron Devices **58**, 4235 (2011).

<sup>&</sup>lt;sup>8</sup>J. C. Wang, C. T. Lin, C. S. Lai, and J. L. Hsu, Appl. Phys. Lett. **97**, 023513 (2010).

<sup>&</sup>lt;sup>9</sup>C. R. Hsieh, Y. Y. Chen, and J. C. Lou, Appl. Phys. Lett. **96**, 022905 (2010).

- <sup>10</sup>C. X. Li, C. H. Leung, P. T. Lai, and J. P. Xu, Solid-State Electron. 54, 675 (2010).

- <sup>11</sup>B. A. V. Hassel and A. J. Burggraaf, Appl. Phys. A **52**, 410 (1991).

- <sup>12</sup>A. Kawamoto, K. Cho, P. Griffin, and R. Dutton, J. Appl. Phys. **90**, 1333 (2001).

- <sup>13</sup>T. Yamaguchi, H. Satake, and N. Fukushima, Tech. Dig. Int. Electron Devices Meet. 2001, 663.

- <sup>14</sup>C. H. Lin and Y. Kuo, J. Appl. Phys. **110**, 024101 (2011).

- <sup>15</sup>G. D. Wilk, R. M. Wallace, and J. M. Anthony, J. Appl. Phys. **89**, 5243 (2001).

- <sup>16</sup>L. M. Terman, Solid-State Electron. **5**, 285 (1962).

- <sup>17</sup>M. Morita, T. Kubo, T. Ishihara, and M. Hirose, Appl. Phys. Lett. 45, 1312 (1984).

- <sup>18</sup>L. Tsetseris, X. J. Zhou, D. M. Fleetwood, R. D. Schrimpf, and S. T. Pantelides, Appl. Phys. Lett. 85, 4950 (2004).

- <sup>19</sup>Y. Kim, S. I. Ohmi, K. Tsutsui, and H. Iwai, Jpn. J. Appl. Phys., Part 1 44, 4032 (2005).

- <sup>20</sup>Y. Liu, S. Tang, and S. K. Banerjee, Appl. Phys. Lett. 88, 213504 (2006).