## Improved memory characteristics by NH<sub>3</sub>-nitrided GdO as charge storage layer for nonvolatile memory applications

L. Liu, <sup>1</sup> J. P. Xu, <sup>1,a)</sup> F. Ji, <sup>1</sup> J. X. Chen, <sup>1</sup> and P. T. Lai<sup>2,a)</sup>

<sup>1</sup>Department of Electronic Science and Technology, Huazhong University of Science and Technology, Wuhan 430074, People's Republic of China

(Received 27 March 2012; accepted 19 June 2012; published online 16 July 2012)

Charge-trapping memory capacitor with nitrided gadolinium oxide (GdO) as charge storage layer (CSL) is fabricated, and the influence of post-deposition annealing in NH<sub>3</sub> on its memory characteristics is investigated. Transmission electron microscopy, x-ray photoelectron spectroscopy, and x-ray diffraction are used to analyze the cross-section and interface quality, composition, and crystallinity of the stack gate dielectric, respectively. It is found that nitrogen incorporation can improve the memory window and achieve a good trade-off among the memory properties due to NH<sub>3</sub>-annealing-induced reasonable distribution profile of a large quantity of deep-level bulk traps created in the nitrided GdO film and reduction of shallow traps near the CSL/SiO<sub>2</sub> interface. © 2012 American Institute of Physics. [http://dx.doi.org/10.1063/1.4737158]

recent years, metal-oxide-nitride-oxide-silicon (MONOS) nonvolatile memory (NVM) has drawn attention due to its superior programming/erasing (P/E) speeds and easier dimension scaling compared with the conventional polycrystalline silicon floating-gate memory. For satisfying the requirements of future NVMs, e.g., large memory window, low power consumption, and good data retention, high-k dielectrics, e.g., HfO<sub>2</sub>, AlN, and Y<sub>2</sub>O<sub>3</sub>, have been proposed to substitute Si<sub>3</sub>N<sub>4</sub> as the charge storage layer (CSL) of MONOS memory due to their high charge-trapping capacity. It has been reported that gadolinium oxide (GdO) is a promising candidate as the gate dielectric of silicon, 5,6 particularly due to its small lattice mismatch (<0.5%) with Si (100). The memory properties of GdO nano-crystal and Gd-incorporated HfO2 dielectric as charge trapping layer have been investigated and reported.<sup>8,9</sup> On the other hand, it is generally believed that nitridation can induce a lot of electron traps, 10 and nitrogen incorporation can enhance the permittivity of the dielectric. 11 It is expected that good charge-trapping properties and dielectric performance could be achieved by using nitrided GdO as the CSL of memory device through appropriate post-deposition annealing (PDA). Therefore, in this work, nitrided GdO is prepared as the CSL of memory device and the effects of PDA conditions on nitrogen incorporation and thus memory performance are investigated. Under suitable annealing conditions, good memory characteristics are achieved for the MONOS memory capacitor with nitrided GdO as CSL.

MONOS and metal-nitride-oxide-silicon (MNOS) capacitors were fabricated on p-type Si wafers. After a standard RCA cleaning,  $SiO_2$  was thermally grown in dry  $O_2$  at 900 °C as the tunneling layer. GdO and nitrided GdO were deposited as the CSL by reactive sputtering of  $SiC_2$  target at an  $SiC_3$  and denoted as  $SiC_4$  and denoted as  $SiC_5$  and

GN1, respectively. Then, a PDA was carried out in  $N_2$  ambient at 550 °C for 30 s. Also, some nitrided GdO samples were annealed in  $N_2$  or  $NH_3$  ambient at 550 °C for 2 min, denoted as GN2 and GN3, respectively. Next,  $Al_2O_3$  was deposited as blocking layer (BL) by atomic layer deposition method by alternating deposition cycles of  $Al(CH_3)_3$  and  $H_2O$  precursors at 300 °C for the MONOS capacitors only. Finally, Al was evaporated and patterned as gate electrode and also as back electrode, followed by forming-gas annealing in  $H_2/N_2$  (5%  $H_2$ ) at 300 °C for 20 min.

The electrical characteristics were measured by HP4284A LCR meter and HP4156A semiconductor parameter analyzer. The flat-band voltage ( $V_{FB}$ ) of the samples was extracted by assuming  $C_{FB}/C_{OX} = 0.5$  ( $C_{FB}$  and  $C_{OX}$  are the flat-band and oxide capacitances, respectively, determined from 1 MHz high-frequency C-V curve).

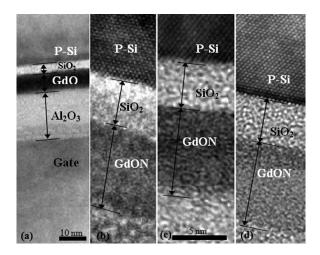

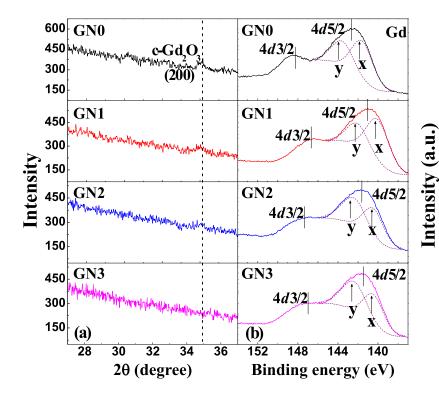

The cross-section and interface quality of the MONOS capacitors were examined by transmission electron microscopy (TEM), as shown in Fig. 1. It can be seen that thicknesses of the BL/CSL/SiO2 layers are almost consistent for the four samples (13 nm/6 nm/3 nm), and the interfaces are clear. Moreover, no clear crystal grain or crystal lattice is observed except for the Si substrate. This is expected for amorphous SiO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub> due to their high crystallization temperature. X-ray diffraction (XRD) analysis is done for these CSL films, as shown in Fig. 2(a). It can be seen that only the GN0 sample exhibits a weak cubic-Gd<sub>2</sub>O<sub>3</sub> (200) peak, indicating that little cubic-phase Gd<sub>2</sub>O<sub>3</sub> is formed after the PDA and no clear diffraction peaks are observed for the GN1, GN2, and GN3 samples, exhibiting amorphous diffraction pattern, which could be attributed to increased crystallization temperature due to nitrogen incorporation.

From the x-ray photoelectron spectroscopy (XPS) analysis, the composition of the CSL in the GN0, GN1, GN2, and GN3 samples is determined to be  $Gd_{0.317}O_{0.683}$ ,  $Gd_{0.368}O_{0.587}N_{0.045}$ ,  $Gd_{0.349}O_{0.615}N_{0.036}$ , and  $Gd_{0.376}O_{0.580}N_{0.044}$ , respectively. The reduced nitrogen content in the GN2 sample could be due to

<sup>&</sup>lt;sup>2</sup>Department of Electrical and Electronic Engineering, The University of Hong Kong, Pokfulam Road, Hong Kong

a) Authors to whom correspondence should be addressed. Electronic addresses: jpxu@mail.hust.edu.cn and laip@eee.hku.hk.

FIG. 1. TEM image of the stacked gate dielectric structure for the four samples: (a) GN0, (b) GN1, (c) GN2, and (d) GN3.

the escape of nitrogen atoms during the annealing in N<sub>2</sub> ambient for 2 min. However, new nitrogen atoms would be incorporated by the NH<sub>3</sub> annealing for the GN3 sample to compensate for the loss of nitrogen content. Fig. 2(b) shows the Gd 4d spectrum with two strong peaks as 4d5/2 and 4d3/2. Compared with the GN0 sample, the Gd 4d spectrum of the three nitrided samples displays a shift toward lower binding energy due to nitrogen incorporation and the shift is different for different N content. The spectrum of Gd 4d5/2 is deconvoluted into two components, denoted as x and y, respectively. The x peak with lower binding energy is correlated to Gd silicate. The reduced Gd content ratio in the x peak state from the GNO sample to the GN3 sample (61%, 56%, 49%, and 46%) indicates that nitrogen incorporation during the sputtering and PDA with longer time, especially in NH3 atmosphere, is effective in improving the structural and interface quality of the CSL due to suppressed formation of gadolinium silicate, e.g., Gd-Gd and Gd-Si bonds. 12

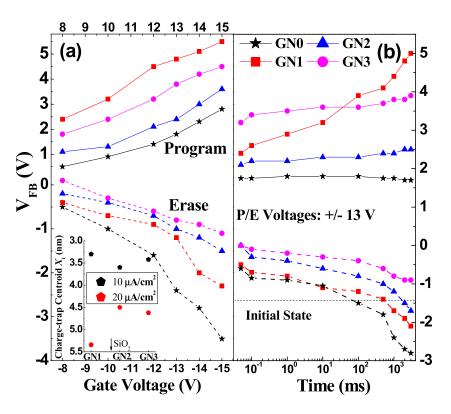

The V<sub>FB</sub> extracted from the 1 MHz C-V curve under different P/E voltages is shown in Fig. 3(a). The much larger memory window of the GN1 sample than that of the GN0 sample is observed, indicating that a large quantity of electron traps exists in the CSL of the GN1 sample due to nitrogen incorporation. The large negative flat-band shift of the GN0 sample under erasing operation could be attributed to more pre-existing hole traps in the CSL or generation of positive charges, induced by oxide and/or oxygen vacancies in the CSL.<sup>13</sup> The small negative shift of V<sub>FB</sub> under erasing operation for the GN1, GN2, and GN3 samples implies that nitrogen incorporation into the GdO film could effectively reduce the oxygen defects and oxygen vacancies to some extent.<sup>14</sup> However, as the annealing time increases, the quantity of the traps in the CSL is reduced due to enhanced densification of the CSL film, thus resulting in a smaller memory window for the GN2 and GN3 samples than the GN1 sample. The larger memory window of the GN3 sample than that of the GN2 sample could be ascribed to creation of extra electron traps related to the hydrogen dissociated from the NH<sub>3</sub> gas.15

The charge-trap centroid from the metal/CSL interface  $(X_t, \text{ nm})$  is extracted using the MNOS capacitors with the same CSL as the GN0, GN1, GN2, and GN3 samples by the constant-current stress method<sup>16</sup>

$$X_t = t_{ox} \left( 1 - \frac{\Delta V_{-g}}{\Delta V_{+g}} \right)^{-1},$$

(1)

where  $t_{ox}$  is thickness of the gate dielectric and  $\Delta V_{-g}$  and  $\Delta V_{+g}$  are the negative and positive gate-voltage shifts. As shown in the inset of Fig. 3(a), the  $X_t$  moves towards the SiO<sub>2</sub> side as the constant-current stress increases, implying that the injected electrons tend to fill the traps near the gate side firstly, which is beneficial for the retention characteristics by avoiding electrons tunneling back to the substrate.

FIG. 2. XRD patterns (a) and Gd 4d XPS patterns (b) for the CSL film of the four samples.

FIG. 3. The  $V_{FB}$  shift under different P/E voltages (a); in the inset charge-trap centroid and the change of  $V_{FB}$  as a function of P/E time (b).

Furthermore, the  $X_t$  of the GN1 sample under  $20 \,\mu\text{A/cm}^2$  constant-current stress is much closer to the  $\text{SiO}_2$  side than that of the GN2 and GN3 samples. So, it could be suggested that for the GN1 sample, more traps in the CSL are close to the CSL/SiO<sub>2</sub> interface and are effectively passivated by longer annealing in N<sub>2</sub> or NH<sub>3</sub>, while bulk traps are dominant for the GN2 and GN3 samples. Moreover, the largest  $X_t$  shift for the GN1 sample demonstrates its wider distribution of electron traps as compared to the GN2 and GN3 sample.

In Fig. 3(b), the  $V_{FB}$  shift of the samples as a function of P/E time is examined at P/E voltages of  $\pm 13$  V. For the GN0 sample, the shift of  $V_{FB}$  quickly reaches saturation during the initial  $100 \, \mu s$  program time and is the minimum among

the four samples, indicating a limited amount of electron traps, probably located near the CSL/SiO $_2$  interface. For the GN1 sample, the  $V_{FB}$  shift gradually increases and is smaller in the initial stage and larger after 10 ms than that of the GN3 sample, especially after 100 ms, a quick increase of  $V_{FB}$  shift occurs. The low programming speed for the GN1 sample further indicates that there is a wide distribution of electron traps in its CSL and more traps are located near the CSL/SiO $_2$  interface as mentioned above. For the GN2 and GN3 samples, the high programming speed and efficiency are associated with the high electron-trap density in the bulk of their CSL. For erasing operation, larger negative shift of  $V_{FB}$  occurs as erasing time increases and exceeds the initial

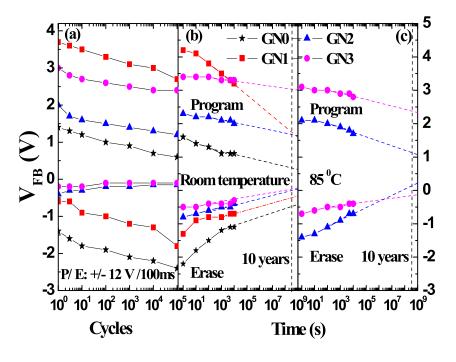

FIG. 4. Endurance (a) and retention characteristics at room temperature (b) or  $85\,^{\circ}\text{C}$  (c) for the MONOS memory capacitors.

$V_{FB}$  value after  ${\sim}60\,\mathrm{ms},\,{\sim}500\,\mathrm{ms},\,\mathrm{and}\,{\sim}1.5\,\mathrm{s}$  for the GN0, GN1, and GN2 samples respectively, resulting in an overerase phenomenon. However, it is observed that the negative  $V_{FB}$  shift of the GN3 sample becomes saturated below the initial  $V_{FB}$  value after 2-s erasing with no over-erase phenomenon, indicating that the annealing treatment of the N-incorporated GdO in  $NH_3$  is beneficial for suppressing the generation of excess hole traps and thus the over-erase phenomenon.

Fig. 4(a) is the endurance characteristics of the four samples. For the GN0 and GN1 samples, the gradual increase of the erasing window should be due to deep-level hole traps near the interface generated by the P/E stress, thus giving rise to accumulation of holes similar to the phenomenon in Ref. 17. For the GN2 and GN3 samples, the window exhibits a normal closing trend as the P/E cycle increases and is degraded by 45% and 21% after 10<sup>5</sup> P/E cycles, respectively. These indicate that the nitrogen incorporation during the reactive sputtering cannot effectively suppress the generation of interface states near/at the CSL/SiO<sub>2</sub> and SiO<sub>2</sub>/Si interfaces during the P/E stress. However, this problem can be solved since the defects and undesired states in the dielectric and at the CSL/SiO2 interface can be eliminated by the NH<sub>3</sub> annealing, <sup>18</sup> and thus their qualities are improved due to reduction of Gd silicates, and some nitrogen is incorporated at/near the SiO<sub>2</sub>/Si interface, which produce stronger chemical bonds.

Figs. 4(b) and 4(c) show the retention characteristics of the samples after removing 100 ms P/E voltages at  $\pm 13$  V. In Fig. 4(b), the initial memory window is 3.8 V, 5.5 V, 3.1 V, and 4.0 V and become 1.2 V, 2.0 V, 1.7 V, and 3.0 V for the extrapolated 10-year memory window with the initialwindow loss of 68%, 64%, 45%, and 25% for the GNO, GN1, GN2, and GN3 samples, respectively. For the GN0 sample, the high loss rate of charges for the erased state in the initial 10 s could be attributed to the excessive hole traps (as mentioned above), which are at shallow energy levels and close to the CSL/SiO<sub>2</sub> interface, thus affecting the stability of the erasing window. Because the electrons in deep traps have lower activation energy comparing with those in shallow traps so that they have a lower probability of directly tunneling to the states at SiO<sub>2</sub>/Si interface.<sup>8,19</sup> In programmed state, the GN2 and GN3 samples display better retention characteristics of electron charges with a lower loss rate of 26% and 12%, respectively, as compared with 56% and 58% of the GN0 and GN1 samples, respectively. This could be ascribed to the reduced shallow-level and interfacial traps and increased deep-level bulk traps, which should be more immune to tunneling of electrons back to the substrate, achieved by the longer annealing or incorporation of more nitrogen. As compared to the GN2 sample, the better charge retention of the GN3 sample even at 85 °C in Fig. 4(c) should be attributed to the recapture of de-trapping electrons by a wider and deeper distribution of trap levels in the CSL bulk.<sup>20</sup>

Nitrided GdO as charge storage layer of MONOS memory capacitor has been prepared by nitrogen-reactive sputtering and the effects of PDA on the characteristics of the memory capacitors have been investigated. It was found that the memory window was greatly improved due to a large quantity of electron traps generated in the GdO CSL by N incorporation. Furthermore, a good trade-off among the memory window, P/E speed, endurance, and retention characteristics has been achieved by using an NH3 annealing at 550 °C for 2 min. These are attributed to nitridation-induced deep-level electron traps in the bulk of the CSL, their suitable spatial distribution, and reduction of shallow traps near the CSL/SiO<sub>2</sub> interface. In addition, the over-erase phenomenon gets effectively suppressed through the NH<sub>3</sub> annealing. Therefore, nitrided GdO dielectric with post-deposition annealing in NH<sub>3</sub> is a promising candidate as the charge storage layer of advanced MONOS nonvolatile memory devices.

This work is financially supported by the National Natural Science Foundation of China (Grant No. 60976091), the Special financial Grant of the China Postdoctoral Science Foundation (201104459), and the University Development Fund (Nanotechnology Research Institute, 00600009) of the University of Hong Kong.

<sup>1</sup>B. Jiankang and M. H. White, Solid-State Electron **45**, 113 (2001).

<sup>2</sup>G. Zhang, X. P. Wang, W. J. Yoo, and M. F. Li, IEEE Trans. Electron Devices **54**, 3317 (2007).

<sup>3</sup>C. H. Lai, C. H. Wu, A. Chin, S. J. Wang, and S. P. McAlisterc, J. Electrochem. Soc. 153, 738 (2006).

<sup>4</sup>T. M. Pan and W. W. Yeh, Appl. Phys. Lett. **92**, 173506 (2008).

<sup>5</sup>J. Kwo, M. Hong, A. R. Kortan, K. T. Queeney, Y. J. Chanbal, J. P. Mannaerts, T. Boone, J. J. Krajewski, A. M. Sergent, and J. M. Rosamilia, Appl. Phys. Lett. 77, 130 (2000).

<sup>6</sup>H. D. B. Gottlob, T. Echtermeyer, M. Schmidt, T. Mollenhauer, J. K. Efavi, and T. Wahbrink, IEEE Electron device Lett. **27**, 814 (2006).

<sup>7</sup>H. J. Osten, E. Bugiel, M. Czernohorsky, Z. Elassar, O. Kirfel, and A. Fissel, Rare Earth Oxide Thin Films: Growth, Characterization, and Application 106, 101 (2007).

<sup>8</sup>J. C. Wang, C. T. Lin, P. C. Chou, and C. S. Lai, Microelectron. Reliab. **52**, 635 (2012).

<sup>9</sup>J. C. Wang, P. C. Chou, C. S. Lai, and L. C. Liu, J. Vac. Sci. Technol. B **29**, 011009 (2011).

H. T. Chang, N. M. Johnson, and S. A. Lyon, Appl. Phys. Lett. 44, 316 (1984).

He, L. D. Zhang, M. Liu, J. P. Zhang, X. J. Wang, and C. M. Zhan, J.

<sup>11</sup>G. He, L. D. Zhang, M. Liu, J. P. Zhang, X. J. Wang, and C. M. Zhan, J. Appl. Phys. **105**, 14109 (2009).

<sup>12</sup>O. Renault, D. Samour, J. F. Damlencourt, D. Blin, F. Martin, and S. Marthon, Appl. Phys. Lett. **81**, 3627 (2002).

<sup>13</sup>K. K. S. Curreem, P. F. Lee, K. S. Wong, J. Y. Daia, M. J. Zhou, J. Wang, and Q. Li, Appl. Phys. Lett. 88, 182905 (2006).

<sup>14</sup>W. R. Chen, T. C. Chang, P. T. Liu, J. L. Yeh, C. H. Tu, J. C. Lou, C. F. Yeh, and C. Y. Chang, Appl. Phys. Lett. 91, 082103 (2007).

<sup>15</sup>T. Hori, H. Iwasaki, Y. Naito, and H. Esaki, IEEE Trans. Electron Devices 34, 2238 (1987).

<sup>16</sup>Z. H. Liu, P. T. Lai, and Y. C. Cheng, IEEE Trans. Electron Devices 38, 344 (1991).

<sup>17</sup>Y. Q. Wang, W. S. Hwang, G. Zhang, G. Samudra, Y. C. Yeo, and W. J. Yoo, IEEE Trans. Electron Devices 54, 2699 (2007).

<sup>18</sup>K. C. Chiang and T. E. Hsieh, *IEEE Trans. Magn.* **47**, 656 (2011).

<sup>19</sup>J. C. Wang and C. T. Lin, J. Appl. Phys. **109**, 064506 (2011).

<sup>20</sup>H. Hamamura, T. Ishida, M. Toshiyuki, Y. Okuyama, D. Hisamoto, Y. Shimamoto, S. Kimura, and T. Kazuyoshi, in Reliability Physics Symposium (IRPS), IEEE International, 27 April 2008-1 May 2008, p. 412.

Applied Physics Letters is copyrighted by the American Institute of Physics (AIP). Redistribution of journal material is subject to the AIP online journal license and/or AIP copyright. For more information, see http://ojps.aip.org/aplo/aplcr.jsp