## Suppressed growth of unstable low-k GeO $_x$ interlayer in Ge metal-oxide-semiconductor capacitor with high-k gate dielectric by annealing in water vapor

X. Zou and J. P. Xu

Department of Electronic Science and Technology, Huazhong University of Science and Technology, Wuhan 430074, People's Republic of China

C. X. Li and P. T. Laia)

Department of Electrical and Electronic Engineering, The University of Hong Kong, Pokfulam Road, Hong Kong

(Received 8 December 2006; accepted 15 March 2007; published online 16 April 2007)

The effects of water vapor added in the  $N_2$  annealing of high-k HfTiON gate dielectric on Ge metal-oxide-semiconductor capacitor are investigated. Both transmission-electron microscopy and ellipsometry indicate that, as compared to dry- $N_2$  annealing, the wet- $N_2$  annealing can greatly suppress the growth of unstable low-k GeO $_x$  at the dielectric/Ge interface, thus resulting in smaller equivalent dielectric thickness, as well as less interface states and dielectric charges. All these are attributed to the hydrolyzable property of  $\text{GeO}_x$  in water. Moreover, the wet- $N_2$  annealed capacitor has ten times lower gate-leakage current due to its better dielectric morphology as confirmed by atomic force microscopy. © 2007 American Institute of Physics. [DOI: 10.1063/1.2723074]

As the scaling of classical Si metal-oxide-semiconductor (MOS) device continues, the fundamental limit of Si technology is in sight. In order to further enhance the currentdrive capability of the device, alternative channel materials are needed for better performance. One of these materials is Ge, which is currently under investigation as a replacement for Si. The main advantages of Ge are its high electron and hole mobilities for carrier transport. However, there is an intrinsic problem in the formation of gate dielectric on Ge substrate: Ge oxide is known to be thermally unstable, water hydrolyzable, and has poor electrical properties. Recently, high-k gate dielectrics on Si substrate have been proved to significantly reduce the leakage current as compared to the traditional SiO<sub>2</sub>/Si system, while still maintaining excellent reliability and high transistor performances. Therefore, deposition of high-k dielectric as gate oxide on Ge substrate has received much attention. Up to now, several metal oxides, e.g.,  $ZrO_2$ , <sup>1</sup>  $HfAlO_x$ , <sup>2</sup>  $HfO_2$ , <sup>3–5</sup> and GeON, <sup>6</sup> have been demonstrated to be suitable for Ge MOS devices. However, it is inevitable to grow a GeO<sub>r</sub> interlayer during the preparation of these gate dielectrics because they are usually formed in an oxidizing ambient. The unstable GeO<sub>r</sub> deteriorates the quality of the Ge/dielectric interface, thus increasing the interface-state density and gate-leakage current. Therefore, it is highly desirable to prepare high-k gate dielectric in a non oxidizing ambient to suppress the growth of the  $GeO_x$  interlayer. In this work, we demonstrate that this goal can be easily achieved by annealing the high-k gate dielectric in water vapor because GeO<sub>x</sub> is highly soluble in water even at room temperature. The electrical characteristics of the relevant MOS capacitors and the effects of the wet-N2 annealing on dielectric performance are analyzed.

Ge substrate used was (100) Sb-doped n-type wafers with a resistivity of 0.4–0.6  $\Omega$  cm. The wafers were cleaned with acetone, trichloroethylene, toluene, and ethanol and

rinsed with deionized water, followed by 60 s diluted HF (1:50) dipping for several cycles to remove the unstable native oxide ( $GeO_x$ ). After drying, HfTiN thin film was deposited by reactive cosputtering method in an  $Ar+N_2$  ambient ( $Ar:N_2=48:12$ ) with a Hf target at 65 W and a Ti target at 25 W, and a chamber pressure of 1 Pa. To minimize the interlayer growth, postdeposition annealing was carried out at 550 °C for 5 min in a dry- $N_2$  or wet- $N_2$  ambient instead of  $O_2$  (denoted as DN2 and WN2 samples, respectively). The wet- $N_2$  atmosphere was realized by bubbling pure  $N_2$  through de-ionized water at 95 °C with a flow rate of 500 ml/min. Then, Al was thermally evaporated and patterned as gate electrode with an area of  $7.85 \times 10^{-5}$  cm<sup>2</sup>. Finally, forming-gas annealing was performed at 300 °C for 20 min.

High-frequency (1 MHz) capacitance-voltage (*C-V*) characteristics were measured at room temperature using HP4284A precision impedance meter. Gate-leakage current was measured by HP4156A precision semiconductor parameter analyzer. Physical thickness of the gate dielectrics was determined by ellipsometry and listed in Table I. Structure of the films was determined by transmission-electron microscopy (TEM). All electrical measurements were carried out under a light-tight and electrically shielded condition.

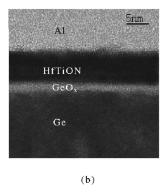

The TEM images in Fig. 1 show that both Ge MOS capacitors have a HfTiON film thickness of 9.1 nm. Moreover, Fig. 1(a) depicts a thin  $\text{GeO}_x$  interlayer (0.9 nm) between Ge and HfTiON in the WN2 sample, while a thicker  $\text{GeO}_x$  interlayer (2.7 nm) exists in the DN2 sample, as shown in Fig. 1(b). This phenomenon indicates that the wet-N<sub>2</sub> annealing is effective for suppressing the oxidation of Ge and thus the growth of the interlayer ( $\text{GeO}_x$ ). This is due to the well-known hydrolyzable property of  $\text{GeO}_x$  in water. On the other hand, the total physical thicknesses ( $t_{ox}$ ) of gate dielectric for the DN2 and WN2 samples measured by ellipsometry are 11.8 and 10.0 nm, respectively. These results are consistent with those obtained from the TEM images in

a) Author to whom correspondence should be addressed; electronic mail: laip@eee.hku.hk

TABLE I. Gate-dielectric capacitance, equivalent dielectric thickness, physical thickness, flatband voltage, and dielectric-charge and interface-state densities.

| Sample     | C <sub>ox</sub> (pF) | t <sub>eq</sub> (nm) | t <sub>ox</sub> (nm) | $V_{\mathrm{fb}} \ \mathrm{(V)}$ | $D_{\rm it}$ at midgap $({ m cm}^{-2}{ m eV}^{-1})$ | $Q_{\rm ox}$ (cm <sup>-2</sup> )            |

|------------|----------------------|----------------------|----------------------|----------------------------------|-----------------------------------------------------|---------------------------------------------|

| DN2<br>WN2 | 79<br>114            | 3.4<br>2.4           | 11.8<br>10.0         | 0.25<br>0.13                     | $7.9 \times 10^{11}$ $2.8 \times 10^{11}$           | $-1.3 \times 10^{12}$ $-7.3 \times 10^{11}$ |

Fig. 1. It should be noted that this wet- $N_2$  annealing is also applicable when thinner HfTiON films with high quality can be prepared by more advanced deposition techniques.

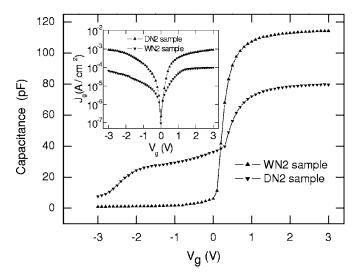

Typical HF C-V curves of the two samples are depicted in Fig. 2. Distortion is observed in the depletion and inversion regions of the C-V curve for the DN2 sample, indicating poor interface quality. This should be associated with significant interfacial defects originating from the growth of the  $GeO_x$  interlayer during the dry- $N_2$  annealing. On the other hand, the growth of the  $GeO_x$  interlayer can be effectively suppressed when the annealing is carried out in a wet- $N_2$  ambient, as shown by the smooth C-V curve of the WN2 sample, implying less interface and near-interface traps.

The values of gate-dielectric capacitance  $(C_{ox})$ , equivalent dielectric thickness  $(t_{eq})$ , and flatband voltage  $(V_{fb})$  extracted from the 1 MHz C-V curves are listed in Table I. Approximate interface-state density at midgap  $(D_{it})$  is also extracted from the 1 MHz C-V curve using the Terman method for comparison purpose only. Equivalent dielectriccharge density  $(Q_{ox})$  is calculated as  $-C_{ox}(V_{fb}-\varphi_{ms})/q$ , where the work-function difference  $\varphi_{\mathrm{ms}}$  between Al and Ge is calculated to be 0.053 V. It can be noted from Table I that  $t_{\rm eq}$  of the DN2 sample is larger than that of the WN2 sample, further indicating the excessive growth of  $GeO_x$  interlayer during the dry- $N_2$  annealing for the DN2 sample. Lower  $D_{it}$ is found for the WN2 sample than the DN2 sample due to suppressed growth of GeO<sub>x</sub> interlayer in the wet ambient. Obviously, the high interface-state density for the DN2 sample probably results from the unstable GeO<sub>r</sub> interlayer, which can lead to Ge atoms outdiffusing into the HfTiON film near the interface to generate a large amount of defects.8 Therefore, the wet-N<sub>2</sub> annealing is favorable for suppressing the growth of the  $GeO_x$  interlayer and thus decreasing  $D_{it}$ because GeO<sub>x</sub> once grown could be easily hydrolyzed in the wet ambient. The negative  $Q_{ox}$  of the WN2 sample should be largely related to the wet annealing ambient and the final forming-gas annealing. The origin of the negative charges might be OH<sup>-</sup>, which cannot diffuse out from the interface at

FIG. 1. TEM images of MOS capacitor. (a) WN2 sample and (b) DN2 sample.

temperature less than 550 °C. <sup>10</sup> For the DN2 sample, the negative  $Q_{ox}$  should be mainly due to the high acceptorlike interface and near-interface trap densities of the  $GeO_x$  interlayer because  $Q_{ox}$  includes not only fixed charge but also interface and near-interface trap charges. <sup>10</sup> Therefore, a larger  $|Q_{ox}|$  of the DN2 sample results in a larger flatband voltage shift than the WN2 sample.

The dielectric constants  $\varepsilon_{\rm ox}$  of the gate stack dielectric, as calculated by  $\varepsilon_{\rm SiO_2}(t_{\rm ox}/t_{\rm eq})$ , are found to be 16.3 and 13.5 for the WN2 and DN2 samples, respectively. The difference between the two dielectric constants is due to the different thicknesses of the  ${\rm GeO}_x$  interlayer, based on the formula of  $\varepsilon_{\rm ox} = \varepsilon_{\rm SiO_2}(t_{\rm ox}/t_{\rm eq}) = t_{\rm ox}/(t_{\rm GeO_x}/\varepsilon_{\rm GeO_x} + t_{\rm HfTiON}/\varepsilon_{\rm HfTiON})$ . Obviously, the larger the thickness of the low-k GeO $_x$  interlayer ( $t_{\rm GeO_x}$ ), the smaller is  $\varepsilon_{\rm ox}$ . Therefore, it is very important to suppress the growth of the  ${\rm GeO}_x$  interlayer and thus achieve large  $\varepsilon_{\rm ox}$  for the gate dielectric like in the WN2 sample.

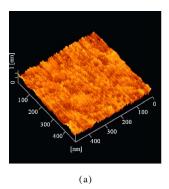

The gate-leakage properties of the two samples are shown in the inset of Fig. 2. The DN2 sample has a large gate leakage of  $1.5 \times 10^{-4}$  A/cm<sup>2</sup> at  $V_g = -1$  V due to large  $D_{it}$  associated with the unstable  $GeO_x$  interlayer. On the other hand, even with a thinner gate dielectric, the WN2 sample displays a much lower gate leakage of  $1.4 \times 10^{-5}$  A/cm<sup>2</sup> at  $V_{o}=-1$  V, thus exhibiting superior bulk and interface properties than the DN2 sample. This should be attributed to the suppressed growth of the unstable GeO<sub>x</sub> interlayer and thus smoother dielectric surface, because it has been reported that the roughness at the dielectric/gate interface can significantly increase the gate-leakage current. Atomic force microscopy (AFM) images of the HfTiON film surface after the wet-N2 and dry-N<sub>2</sub> annealings are shown in Fig. 3. The rms surface roughness of the dry-N<sub>2</sub> annealed sample (0.56 nm) is much larger than that of the wet- $N_2$  annealed sample (0.21 nm).

FIG. 2. High-frequency (1 MHz) *C-V* curves of the samples. The inset shows their gate-leakage current density vs gate voltage.

FIG. 3. (Color online) AFM images  $(0.5\times0.5~\mu\text{m}^2)$  of HfTiON films with (a) wet-N<sub>2</sub> annealing and (b) dry-N<sub>2</sub> annealing.

The reason is that owing to the stronger growth of the  $GeO_x$  interlayer during the  $dry-N_2$  annealing, more Ge atoms can outdiffuse from the  $GeO_x$  interlayer to the high-k dielectric film and then pile up at the surface, resulting in larger roughness.

In summary, the effects of postdeposition annealing in water vapor on the physical and electrical properties of Ge MOS capacitors with HfTiON gate dielectric have been investigated. Wet- $N_2$  annealing for deposited HfTiON film can induce a great reduction of interface-state/dielectric-charge densities and gate-leakage current due to the suppressed growth of unstable  $\text{GeO}_x$  interlayer in the wet ambient. This is attributed to the well-known hydrolyzable property of  $\text{GeO}_x$  in water. Therefore, depositing HfTiN film followed by wet- $N_2$  annealing to form HfTiON gate dielectric is a prom-

ising process for fabricating advanced Ge MOS transistors with high-k gate dielectric.

This work is financially supported by the National Natural Science Foundation of China (NSFC) under Grant No. 60576021, the Research Grants Council (RGC) of Hong Kong Special Administrative Region (HKSAR), China under Project No. HKU7142/05E, and the University Development Fund (Nanotechnology Research Institute, 00600009) of The University of Hong Kong.

<sup>1</sup>D. Chi, C. O. Chui, K. C. Saraswat, B. B. Triplett, and P. C. McIntyre, J. Appl. Phys. **96**, 813 (2004).

<sup>2</sup>D. Wu, A. C. Lindgren, S. Persson, G. Sjoblom, H. M. Von, J. Seger, P.-E. Hellstrom, J. Olsson, H.-O. Blom, S.-L. Zhang, M. Ostling, E. Vainonen-Ahlgren, W.-M. Li, E. Tois, and M. Tuominen, IEEE Electron Device Lett. **24**, 171 (2003).

<sup>3</sup>M. Houssa, B. D. Jaeger, A. Delabie, S. V. Elshocht, V. V. Afanas'ev, J. L. Autran, A. Stesmans, M. Meuris, and M. M. Heyns, J. Non-Cryst. Solids 351, 1902 (2005).

<sup>4</sup>T. J. Park, S. K. Kim, J. H. Kim, J. Park, M. Cho, S. W. Lee, S. H. Hong, and C. S. Hwang, Microelectron. Eng. **80**, 222 (2005).

<sup>5</sup>N. Wu, Q. C. Zhang, C. X. Zhu, D. S. H. Chan, M. F. Li, N. Balasubramanian, Albert Chin, and Dim-Lee Kwong, Appl. Phys. Lett. **85**, 4127 (2004).

<sup>6</sup>J. P. Xu, P. T. Lai, C. X. Li, X. Zou, and C. L. Chan, IEEE Electron Device Lett. **27**, 439 (2006).

<sup>7</sup>L. M. Terman, Solid-State Electron. **5**, 285 (1962).

<sup>8</sup>N. Lu, W. Bai, A. Ramirez, C. Mouli, A. Ritenour, M. L. Lee, D. Antoniadis, and D. L. Kwong, Appl. Phys. Lett. 87, 051922 (2005).

<sup>9</sup>H. Yano, F. Katafuchi, T. Kimoto, and H. Matsunami, IEEE Trans. Electron Devices **46**, 504 (1999).

<sup>10</sup>P. T. Lai, C. X. Li, J. P. Xu, X. Zou, and C. L. Chan, Proceedings of the 2005 IEEE Conference on Electron Devices and Solid-State Circuits, 2005, p. 115.

<sup>11</sup>L. F. Mao, C. H. Tan, and M. Z. Xu, Solid-State Electron. **45**, 531 (2001).

Applied Physics Letters is copyrighted by the American Institute of Physics (AIP). Redistribution of journal material is subject to the AIP online journal license and/or AIP copyright. For more information, see http://ojps.aip.org/aplo/aplor.jsp