## Improved interfacial and electrical properties of Ge MOS capacitor by using TaON/LaON dual passivation interlayer

Z. X. Cheng, J. P. Xu, A. L. Liu, Y. Huang, P. T. Lai, and W. M. Tang

<sup>1</sup>School of Optical and Electronic Information, Huazhong University of Science and Technology, Wuhan 430074, China

(Received 10 May 2016; accepted 2 July 2016; published online 15 July 2016)

The effects of TaON/LaON dual passivation interlayer on the interfacial and electrical properties of Ge metal-oxide-semiconductor (MOS) capacitor with HfO<sub>2</sub> gate dielectric are investigated. As compared to its counterpart with only LaON as passivation interlayer, the formation of HfGeO<sub>x</sub> and LaHfO<sub>x</sub>, which would degrade the interfacial quality, is effectively suppressed due to the strong blocking role of the TaON barrier layer against Hf diffusion. As a result, excellent interfacial and electrical properties are achieved for the Ge MOS device with the TaON/LaON dual passivation interlayer: high k value (20.9), low interface-state density (5.32 × 10<sup>11</sup> cm<sup>-2</sup> eV<sup>-1</sup>) and oxide-charge density (-3.90 × 10<sup>12</sup> cm<sup>-2</sup>), low gate leakage current density (1.77 × 10<sup>-4</sup> A/cm<sup>2</sup> at  $V_g = V_{\rm fb} + 1$  V), and high reliability under high-field stress. *Published by AIP Publishing*. [http://dx.doi.org/10.1063/1.4958837]

High-mobility germanium metal-oxide-semiconductor field-effect transistors (MOSFETs) with high permittivity (high-k) dielectrics have been extensively investigated to further improve the scaled CMOS technology. 1 As the most promising high-k gate dielectric for Si-based MOSFETs, HfO<sub>2</sub>-based dielectrics have been used in state-of-the-art integrated circuits since the 45-nm technology node<sup>2</sup> due to its high k value ( $\sim$ 25), relatively large bandgap ( $\sim$ 5.8 eV) and good thermal stability with the Si substrate.<sup>3</sup> However, when HfO<sub>2</sub> was deposited on the Ge substrate directly, unstable GeO<sub>x</sub> was parasitically grown.<sup>4</sup> Moreover, defective HfGeO<sub>x</sub> was formed due to the intermixing between the Ge substrate and HfO<sub>2</sub> dielectric, 5,6 and so severely degraded the quality of the HfO<sub>2</sub>/Ge interface and thus the electrical properties of the device. On the contrary, La<sub>2</sub>O<sub>3</sub> could react strongly with the Ge substrate to form a stable germanate layer for suppressing the formation of GeO<sub>x</sub> and outdiffusion of Ge, thus creating a superior interface with the Ge substrate. 7-9 This was attributed to the fact that the fourfold-coordinated La in the germanate produced a defectfree interface with Ge, but the fivefold-coordinated Hf in HfGeO<sub>x</sub> could result in many interface states. <sup>10</sup> In other words, LaGeO<sub>x</sub>/Ge can have similar interface quality as GeO<sub>2</sub>/Ge and also avoid the disadvantages of GeO<sub>2</sub> (water solubility and thermal instability). 11 As a result, LaGeO<sub>x</sub> could be a promising passivation interlayer for the Ge substrate. Moreover, N incorporation into La<sub>2</sub>O<sub>3</sub> could further suppress the Ge diffusion and improve the interfacial property. 8,12 However, when La<sub>2</sub>O<sub>3</sub> was used as passivation interlayer followed by deposition of HfO2 dielectric, Hf still could diffuse into the La2O3 interlayer and thus reduce the effect of passivation. 13,14 To solve this problem, a TaON barrier layer, which is effective in suppressing the diffusions of Ge and Hf,<sup>15,16</sup> is inserted between the LaON passivation interlayer and HfO<sub>2</sub> gate dielectric in this work. As a result, excellent interfacial and electrical properties are obtained by the HfO<sub>2</sub>/(TaON/LaON) gate stack with TaON/LaON as a dual passivation interlayer.

Germanium MOS capacitors were fabricated on n-type (100) Ge substrates with a resistivity of 0.02–0.1  $\Omega$  cm. Prior to the dielectric stack formation, the Ge surface was cleaned in trichloroethylene, acetone, and ethanol in sequence, and finally rinsed in de-ionized water followed by 30-s diluted high-frequency HF (1:50) dipping for several cycles to remove the native oxide. After drying by N<sub>2</sub> gas, the wafers were immediately transferred to a sputtering chamber. The stacked gate dielectric of HfO2/TaON/LaON (denoted as TaON/LaON sample) was formed through successively depositing 1-nm LaON by sputtering of a La<sub>2</sub>O<sub>3</sub> target in  $Ar + N_2$ , 1-nm TaN by sputtering of a Ta target in  $Ar + N_2$ , and 6-nm HfO<sub>2</sub> by sputtering of a HfO<sub>2</sub> target in Ar ambient. For comparison, 6-nm HfO<sub>2</sub>/2-nm LaON stacked gate dielectric (denoted as LaON sample) and 8-nm HfO<sub>2</sub> gate dielectric (denoted as control sample) were also fabricated using the corresponding sputtering conditions above. Then, a postdeposition annealing (PDA) was carried out in N2 (500 sccm) + O<sub>2</sub> (50 sccm) ambient at 500 °C for 5 min to convert TaN to TaON and reduce the oxygen vacancy in HfO<sub>2</sub>. Al was evaporated and patterned by lithography as gate electrode with an area of  $7.85 \times 10^{-5}$  cm<sup>2</sup>, followed by a forming-gas (5%  $H_2 + 95\%$   $N_2$ ) annealing at 300 °C for 20 min to reduce its contact resistance.

High-frequency (HF) capacitance-voltage (C-V) and gate leakage current density versus gate voltage  $(J_g\text{-}V_g)$  characteristics of the samples were measured by HP4284A precision LCR meter and HP4156A semiconductor parameter analyzer, respectively. High-field stress by HP4156A was applied to the gate stack to examine the device reliability in the terms of gate-current increase and flatband-voltage shift.

$<sup>^{2}</sup>$ Department of Electrical and Electronic Engineering, The University of Hong Kong, Pokfulam Road, Pokfulam, Hong Kong

<sup>&</sup>lt;sup>3</sup>Department of Applied Physics, The Hong Kong Polytechnic University, Hung Hom, Kowloon, Hong Kong

a) Authors to whom correspondence should be addressed. Electronic addresses: jpxu@hust.edu.cn and laip@eee.hku.hk

X-ray photoelectron spectroscopy (XPS) was used to investigate the chemical states and interfacial quality of the high-*k*/Ge interface. All electrical measurements were carried out under a light-tight and electrically shielded condition at room temperature.

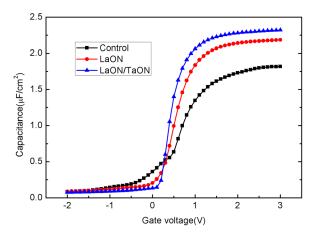

Fig. 1 shows the typical HF (1-MHz) C-V curves of the three samples. Obviously, the control sample without interface passivation layer (IPL) exhibits poor C-V behavior with the largest stretch out and even distortion in the weak inversion region, indicating poor interfacial quality caused by parasitically grown GeO<sub>x</sub> and defective HfGeO<sub>x</sub>. The formation of low-k GeO<sub>x</sub> ( $k \sim 5$ ) also results in a reduction of accumulation capacitance. 17,18 With a LaON IPL inserted between the HfO<sub>2</sub> gate dielectric and Ge substrate (for the LaON sample), much less stretch out is observed and also the distortion in the weak inversion region is eliminated, implying much better interfacial quality than the control sample. This is because the LaON IPL can react with the Ge substrate to form a stable germanate interlayer, which can block the Ge out-diffusion and O in-diffusion, 8,12 resulting in a superior interfacial quality. Moreover, the accumulation capacitance  $(C_{ox})$  of the LaON sample is increased due to the suppression of  $GeO_x$  and relatively high k value of  $LaGeO_xN_v$  (~12). The TaON/LaON sample has an even steeper transition from depletion to accumulation than the LaON sample, implying the best interfacial quality among the samples. This is attributed to the barrier role of the TaON layer against the indiffusion of Hf to avoid the degradation of the LaGeO<sub>x</sub>N<sub>v</sub> IPL, which together with the high k value of TaON ( $\sim$ 26), <sup>20</sup> contribute to the larger  $C_{ox}$  of the TaON/LaON sample than that of the LaON sample. The barrier role of the TaON layer will be discussed in detail by XPS analysis below.

The capacitance equivalent thickness (*CET*) and interface-state density near midgap ( $D_{\rm it}$ ) extracted from the HF C-V curve by the Terman's method for the purpose of comparison are listed in Table I. Obviously, the TaON/LaON sample exhibits the smallest *CET* and  $D_{\rm it}$ . The effective k value of the LaON/TaON sample calculated by  $k_{\rm die} = \varepsilon_{\rm SiO_2} \times t_{\rm die}/CET$  is 20.9, where  $\varepsilon_{\rm SiO_2}$  is the relative permittivity of SiO<sub>2</sub> and  $t_{\rm die}$  is the physical thickness of the dielectric. The flat-band voltage ( $V_{\rm fb}$ ) and the corresponding equivalent oxide-charge density [ $Q_{\rm ox} = -C_{\rm ox} \times (V_{\rm fb} - \varphi_{\rm ms})/Q_{\rm ms} = 0$  work function difference between the Al gate and

FIG. 1. HF (1-MHz) C-V curve of the samples.

TABLE I. Electrical and physical parameters of the samples extracted from their HF *C-V* curves.

| Sample    | $C_{\rm ox}$ $(\mu \text{F/cm}^{-2})$ | CET (nm) | $k_{\rm die}$ | $V_{\mathrm{fb}}$ | $Q_{\rm ox}$ (cm <sup>-2</sup> ) | $\begin{array}{c} D_{\rm it} \\ ({\rm eV}^{-1}{\rm cm}^{-2}) \end{array}$ |

|-----------|---------------------------------------|----------|---------------|-------------------|----------------------------------|---------------------------------------------------------------------------|

| $HfO_2$   | 1.82                                  | 1.90     | 16.4          | 0.55              | $-5.98 \times 10^{12}$           | $7.43 \times 10^{12}$                                                     |

| LaON      | 2.18                                  | 1.59     | 19.6          | 0.36              | $-4.83 \times 10^{12}$           | $8.02 \times 10^{11}$                                                     |

| LaON/TaON | 2.32                                  | 1.49     | 20.9          | 0.25              | $-3.90 \times 10^{12}$           | $5.32 \times 10^{11}$                                                     |

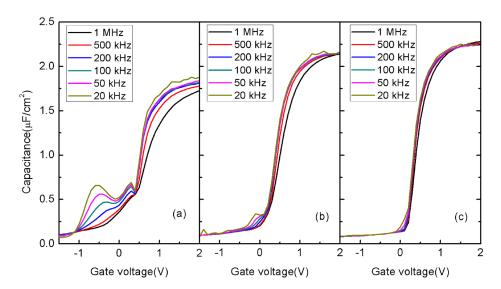

Ge substrate] are also listed in Table I. The negative  $Q_{ox}$ should be mainly due to the defects induced by Ge atom trapped at the oxygen vacancy of HfO2, resulting from the intermixing between  $HfO_2$  and  $Ge.^{21}$  The smallest  $Q_{ox}$  of the TaON/LaON sample further supports the effective blocking role of the TaON/LaON dual IPL against the diffusions of Ge, O, and Hf. Frequency dispersion in the C-V curve of these samples is shown in Fig. 2 to further illustrate their interfacial quality. The dispersive behavior of C-V curve from depletion to accumulation and from weak to strong inversion is attributed to the interface traps near the Ge valance band and conduction band, respectively.<sup>22</sup> Large frequency dispersion in the two regions is observed in Fig. 2(a), indicating a large  $D_{it}$  for the control sample. However, the two samples with IPL have greatly suppressed frequency dispersion, with the TaON/LaON sample in Fig. 2(c) exhibiting the smallest dispersion in both regions, thus suggesting the smallest  $D_{it}$ and best interfacial quality.

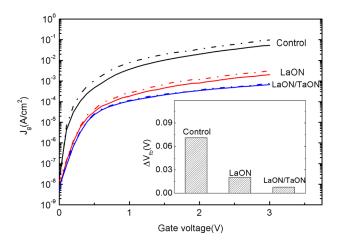

The typical gate-leakage properties of the samples before and after a high-field stress (at 7 MV/cm for 3600 s) are shown in Fig. 3. The control sample without IPL exhibits quite large gate leakage current density  $(J_g)$  even before stress  $(1.12 \times 10^{-2} \text{ A/cm}^2 \text{ at Vg} = V_{fb} + 1 \text{ V})$ . This is due to the poor interfacial quality and large  $Q_{ox}$  in the gate dielectric, resulting from the inter-diffusions of Ge, O, and Hf, and thus the formation of unstable GeO<sub>x</sub> and defective HfGeO<sub>x</sub>, as mentioned earlier. Moreover, the reduction of conductionband offset between HfO2 and Ge caused by GeOx might further increase the gate leakage current.<sup>23</sup> With the use of the LaON IPL or LaON/TaON dual IPL, the pre-stress gate leakage current is greatly reduced  $(3.63 \times 10^{-4} \,\text{A/cm}^2)$  and  $1.77 \times 10^{-4} \,\mathrm{A/cm^2}$  at  $V_{\rm g} = V_{\rm fb} + 1 \,\mathrm{V}$  for the LaON and LaON/TaON samples, respectively). As expected, the LaON/ TaON sample achieves the smallest gate leakage current due to the more effective blocking of TaON against Hf, O and Ge diffusions and better interfacial quality than the LaON sample. After the high-field stress, the LaON/TaON sample displays the best reliability with the smallest  $J_{\rm g}$  increase and  $V_{\rm fb}$ shift, based on the same reasons mentioned above.

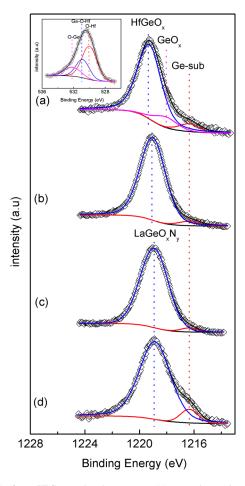

In order to further analyze the effects of the LaON and TaON/LaON interlayers on the interfacial quality between the high-k stack and Ge substrate, the composition and chemical states near the interface are investigated by XPS analysis. The energy scale of the three samples is calibrated by fixing the Ge 3d peak of the Ge substrate at a binding energy (BE) of  $28.8 \, \text{eV}$  to eliminate the charging effect on the samples. Because of a strong overlap between the Ge 3d peak and Hf or Ta peak,  $^{4.24}$  the Ge  $2p_{3/2}$  core level spectrum of the samples is used, as shown in Fig. 4. For comparison, a sample with only LaON on Ge substrate is fabricated

FIG. 2. Frequency dispersion of *C–V* curve: (a) control sample, (b) LaON sample, and (c) TaON/LaON sample.

(denoted as LaON/Ge sample) and its Ge  $2p_{3/2}$  core level spectrum is shown in Fig. 4(d). For the control sample without IPL, a peak with a BE of 1218.1 eV is observed in Fig. 4(a), which is attributed to  $\text{GeO}_x$ , as confirmed by a peak at  $\sim$ 532 eV in the O 1s core level spectrum in the inset of Fig. 4(a), attributed to O-Ge bond. However, this peak does not occur for the LaON and TaON/LaON samples, indicating the effective suppression of  $\text{GeO}_x$  growth by the stable LaGeO<sub>x</sub>N<sub>y</sub> IPL.

The peak with a BE of 1219.3 eV in Fig. 4(a) is attributed to HfGeO<sub>x</sub>, which is formed by the reaction between the HfO<sub>2</sub> gate dielectric and Ge substrate during the 500 °C PDA.<sup>23</sup> For the LaON/Ge sample in Fig. 4(d), a stable LaGeO<sub>x</sub>N<sub>y</sub> interlayer is formed, and correspondingly, a peak with a BE of 1218.9 eV is observed, located at a lower BE than the HfGeO<sub>x</sub> peak in Fig. 4(a). This is because enhanced charge transfer occurs from La atom to La–O–Ge than from Hf atom to Hf–O–Ge due to the lower electronegativity of La (1.1) than Hf (1.3), leading to a smaller BE for La-O-Ge.<sup>23</sup> For the LaON sample in Fig. 4(b), the germanate peak shifts to somewhere between the peaks of HfGeO<sub>x</sub> [Fig. 4(a)] and pure LaGeO<sub>x</sub>N<sub>y</sub> [Fig. 4(d)], implying the formation of an interlayer with both LaGeO<sub>x</sub>N<sub>y</sub> and HfGeO<sub>x</sub> due to the diffusion of Hf into the LaGeO<sub>x</sub>N<sub>y</sub> interlayer. However, for

FIG. 3.  $J_{\rm g}$  vs.  $V_{\rm g}$  characteristics of the samples before and after a high-field stress at 7 MV/cm for 3600 s. The inset shows the  $\Delta V_{\rm fb}$  after the stress.

the TaON/LaON sample in Fig. 4(c), the germanate peak is located at the same BE as that of the LaON/Ge sample in Fig. 4(d), indicating the formation of a pure LaGeO<sub>x</sub>N<sub>y</sub> interlayer without Hf incorporation. This is obviously attributed to the fact that the TaON barrier layer can effectively block the Hf diffusion and thus suppress the formation of HfGeO<sub>x</sub>.

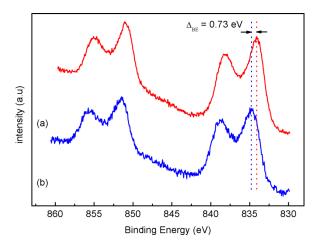

To further investigate the role of the TaON barrier layer, the Hf 4f and La 3d core level spectra of the LaON and TaON/LaON samples are shown in Figs. 5 and 6,

FIG. 4. Ge  $2p_{3/2}$  XPS core level spectrum: (a) control sample, (b) LaON sample, (c) TaON/LaON sample, and (d) LaON/Ge sample. The inset shows the O 1s XPS core level spectrum of the control sample.

FIG. 5. Hf 4f XPS core level spectrum: (a) LaON sample and (b) TaON/LaON sample.

respectively. The Hf 4f spectrum of the TaON/LaON sample in Fig. 5(b) can be deconvoluted to two different components as  $4f_{7/2}$  at 17.1 eV and  $4f_{5/2}$  at 18.8 eV, with a spin-orbital splitting of  $1.7 \,\text{eV}$ . This can be assigned as the pure  $\text{HfO}_2$ . For the LaON sample without the TaON barrier in Fig. 5(a), an obvious negative shift (0.61 eV) of the Hf 4f spectrum is observed due to the diffusion of Hf and thus the formation of LaHfO<sub>x</sub>. <sup>14</sup> A peak of 834.8 eV in the La 3d spectrum of Fig. 6(b) for the TaON/LaON sample is attributed to the La-O-Ge bond, which is at a higher energy level than La-O-La  $(\sim 834 \,\mathrm{eV})$ . <sup>14</sup> Owing to the lower electronegativity of Hf (1.1) than Ge (2.01), the BE of the La-O-Hf peak is smaller than that of La-O-Ge. So, another evidence for the Hf diffusion and LaHfO<sub>x</sub> formation in the LaON sample is the negative shift of the La 3d spectrum in Fig. 6(a) relative to that in Fig. 6(b). All of these results demonstrate that the TaON interlayer can indeed play a significant role in suppressing the Hf diffusion to avoid the undesirable formations of LaHfO<sub>x</sub> and HfGeO<sub>x</sub>. Based on the fact that Hf-Ta binary compound cannot be formed,<sup>28</sup> the barrier effect of TaON against the Hf diffusion is probably similar to that of TaN<sub>x</sub> against Cu diffusion (Ta forms virtually no solid solution

FIG. 6. La 3d XPS core level spectrum: (a) LaON sample and (b) TaON/LaON sample.

with Cu and exhibits small self-diffusion coefficient).<sup>29</sup> This is why the TaON/LaON sample exhibits better interfacial quality and thus electrical properties than the LaON sample.

In summary, the Ge surface can be well passivated by using a TaON/LaON dual interlayer to improve the interfacial quality and electrical properties of Ge MOS device with HfO<sub>2</sub> gate dielectric. Although the sample with LaON IPL can suppress the growth of defective GeO<sub>x</sub> and HfGeO<sub>x</sub> by forming a stable LaGeO<sub>x</sub>N<sub>v</sub> interlayer, Hf diffusion into the LaGeO<sub>x</sub>N<sub>v</sub> interlayer can still form HfGeO<sub>x</sub> and LaHfO<sub>x</sub> to degrade the interfacial quality. This problem can be satisfactorily solved by using TaON/LaON as dual IPL due to the effective blocking capability of the TaON barrier layer against Hf diffusion, thus leading to better interfacial quality and electrical properties: large k value (20.9), low interface-state density  $(5.32 \times 10^{11} \, \text{cm}^{-2} \, \text{eV}^{-1})$  and oxide-charge density  $(-3.90\times10^{12}\,\text{cm}^{-2}),$  small gate leakage current  $(1.77\times10^{-4}~\text{A/cm}^2~\text{at}~V_g\,{=}\,V_{fb}\,{+}\,1~\text{V}),$  and good high-field reliability. Therefore, the TaON/LaON dual interlayer is a promising passivation approach to obtain high-quality gatedielectric/Ge interface and thus high-performance Ge MOS device.

This work was financially supported by the National Natural Science Foundation of China (Grant Nos. 61274112, 61176100, 61404055), the Hong Kong Polytechnic University (Project No. 1-ZVB1), and the University Development Fund (Nanotechnology Research Institute, 00600009) of the University of Hong Kong.

<sup>1</sup>Y. Kamata, Mater. Today 11, 30–38 (2008).

<sup>2</sup>K. Kuhn, C. Kenyon, and A. Kornfeld, Intel Technol. J. **12**, 93–109 (2008).

<sup>3</sup>N. Lu, H. J. Li, J. J. Peterson, and D. L. Kwong, Appl. Phys. Lett. **90**, 082911 (2007).

<sup>4</sup>H. Jung, I. Yu, H. K. Kim, S. Y. Lee, J. Lee, Y. Choi, Y. J. Chung, N. Lee, T. J. Park, J. Choi, and C. S. Hwang, IEEE Trans. Electron Devices **59**, 2350–2356 (2012).

<sup>5</sup>S. Van Elshocht, M. Caymax, T. Conard, S. De Gendt, I. Hoflijk, M. Houssa, B. De Jaeger, J. Van Steenbergen, M. Heyns, and M. Meuris, Appl. Phys. Lett. 88, 141904 (2006).

<sup>6</sup>N. Lu, W. Bai, A. Ramirez, C. Mouli, A. Ritenour, M. L. Lee, D. Antoniadis, and D. L. Kwong, Appl. Phys. Lett. **87**, 051922 (2005).

<sup>7</sup>S. Abermann, C. Henkel, O. Bethge, G. Pozzovivo, P. Klang, and E. Bertagnolli, Appl. Surf. Sci. **256**, 5031–5034 (2010).

<sup>8</sup>H. X. Xu, J. P. Xu, C. X. Li, and P. T. Lai, Appl. Phys. Lett. 97, 022903 (2010).

<sup>9</sup>C. X. Li and P. T. Lai, Appl. Phys. Lett. **95**, 022910 (2009).

<sup>10</sup>G. Mavrou, P. Tsipas, A. Sotiropoulos, S. Galata, Y. Panayiotatos, A. Dimoulas, C. Marchiori, and J. Fompeyrine, Appl. Phys. Lett. 93, 212904 (2008).

<sup>11</sup>A. Molle, S. Baldovino, M. Fanciulli, D. Tsoutsou, E. Golias, and A. Dimoulas, J. Appl. Phys. 110, 084504 (2011).

M. Lin, C. Lan, C. Chen, and J. Wu, Appl. Phys. Lett. 99, 182105 (2011).

Mavrou, S. Galata, P. Tsipas, A. Sotiropoulos, Y. Panayiotatos, A. Dimoulas, E. K. Evangelou, J. W. Seo, and C. Dieker, J. Appl. Phys. 103, 014506 (2008).

<sup>14</sup>D. Tsoutsou, Y. Panayiotatos, and A. Sotiropoulos, J. Appl. Phys. 108, 064115–064115-7 (2010).

<sup>15</sup>J. P. Xu, X. F. Zhang, C. X. Li, P. T. Lai, and C. L. Chan, IEEE Electron Device Lett. 29, 1155–1158 (2008).

<sup>16</sup>F. Ji, J. P. Xu, P. T. Lai, C. X. Li, and J. G. Liu, IEEE Electron Device Lett. 32, 122–124 (2011).

<sup>17</sup>R. Zhang, T. Iwasaki, N. Taoka, M. Takenaka, and S. Takagi, Microelectron. Eng. 88, 1533–1536 (2011).

<sup>18</sup>S. N. A. Murad, P. T. Baine, D. W. McNeill, S. J. N. Mitchell, B. M. Armstrong, M. Modreanu, G. Hughes, and R. K. Chellappan, Solid-State Electron. 78, 136–140 (2012).

- <sup>19</sup>C. Andersson, C. Rossel, M. Sousa, D. J. Webb, C. Marchiori, D. Caimi, H. Siegwart, Y. Panayiotatos, A. Dimoulas, and J. Fompeyrine, Microelectron. Eng. 86, 1635–1637 (2009).

- <sup>20</sup>L. S. Wang, J. P. Xu, S. Y. Zhu, Y. Huang, and P. T. Lai, Appl. Phys. Lett. 103, 092901 (2013).

- <sup>21</sup>Q. Sun, Y. Shi, L. Dong, H. Liu, S. Ding, and D. W. Zhang, Appl. Phys. Lett. **92**, 102908 (2008).

- <sup>22</sup>L. L. Zhang, H. L. Li, Y. Z. Guo, K. C. Tang, J. Woicik, J. Robertson, and P. C. McIntyre, ACS Appl. Mater. Interfaces 7, 20499 (2015).

- <sup>23</sup>X. F. Li, X. J. Liu, Y. Q. Cao, A. D. Li, H. Li, and D. Wu, Appl. Surf. Sci. **264**, 783–786 (2013).

- <sup>24</sup>F. Ji, J. P. Xu, and Y. Huang, IEEE Trans. Electron Devices 61, 3608–3612 (2014).

- S. Shibayama, K. Kato, M. Sakashita, W. Takeuchi, N. Taoka, O. Nakatsuka, and S. Zaima, Thin Solid Films 557, 282–287 (2014).

- <sup>26</sup>C. X. Li, C. H. Leung, P. T. Lai, and J. P. Xu, Solid-State Electron. **54**, 675–679 (2010)

- <sup>27</sup>R. Asahara, I. Hideshima, H. Oka, Y. Minoura, S. Ogawa, A. Yoshigoe, Y. Teraoka, T. Hosoi, T. Shimura, and H. Watanabe, Appl. Phys. Lett. 106, 233503 (2015).

- <sup>28</sup>O. Levy, G. L. W. Hart, and S. Curtarolo, Acta Mater. **58**, 2887–2897 (2010).

- <sup>29</sup>H. Ono, T. Nakano, and T. Ohta, Appl. Phys. Lett. **64**, 1511 (1994).