## 23 bits optical sensor based on nonvolatile organic memory transistor

Xiaochen Ren and Paddy K. L. Chan

Citation: Applied Physics Letters 104, 113302 (2014); doi: 10.1063/1.4869308

View online: http://dx.doi.org/10.1063/1.4869308

View Table of Contents: http://scitation.aip.org/content/aip/journal/apl/104/11?ver=pdfcov

Published by the AIP Publishing

## Articles you may be interested in

Ambipolar organic thin-film transistor-based nano-floating-gate nonvolatile memory Appl. Phys. Lett. **104**, 013302 (2014); 10.1063/1.4860990

Spatial profile of charge storage in organic field-effect transistor nonvolatile memory using polymer electret Appl. Phys. Lett. **103**, 143302 (2013); 10.1063/1.4824213

Nonvolatile memory thin film transistors using CdSe/ZnS quantum dot-poly(methyl methacrylate) composite layer formed by a two-step spin coating technique

J. Appl. Phys. 112, 034518 (2012); 10.1063/1.4745041

Nonvolatile organic transistor-memory devices using various thicknesses of silver nanoparticle layers Appl. Phys. Lett. **97**, 023511 (2010); 10.1063/1.3462949

Nonvolatile organic field-effect transistor memory element with a polymeric gate electret Appl. Phys. Lett. **85**, 5409 (2004); 10.1063/1.1828236

## 23 bits optical sensor based on nonvolatile organic memory transistor

Xiaochen Ren and Paddy K. L. Chan<sup>a)</sup>

Department of Mechanical Engineering, The University of Hong Kong, Hong Kong

(Received 13 November 2013; accepted 11 March 2014; published online 20 March 2014)

Polymer electret transistor memory device has stable charge storage and memory properties. Here, we combine a large band gap organic semiconductor dinaphtho[2,3-b:2',3'-f]thieno[3,2-b]thiophene with the polystyrene electret to form an optical sensor with memory effect. The blue light combined with programming bias leads to a positive threshold voltage shift for more than 100 V while the drain-source current shows a variation of seven orders of magnitude. The dynamic range of current device is up to 23 bits and the photo responsivity is 420 A W<sup>-1</sup>. The optically programmed transistor can be directly used for high-resolution optical sensor and multi-level data storage applications. © 2014 AIP Publishing LLC. [http://dx.doi.org/10.1063/1.4869308]

Organic field effect transistors (OFETs) have demonstrated their potential applications in various functional devices including memories<sup>1</sup> and integrated sensors.<sup>2</sup> In memory transistors, the carrier density in the channel region is precisely controlled by the local electrical field induced by trap charges that are generated by electrical bias or external stimulations such as pressure and light. Different structures have been realized for organic memory transistor, such as inserting the floating gate layer, using polymer electrets as charge trapping media,<sup>3</sup> and placing metal nanoparticles into dielectric<sup>4</sup> or semiconductor<sup>5</sup> as the charge trapping centers. Among these structures, polymer electret has demonstrated high writing/erasing speed with long charge retention property. 6,7 Baeg et al. has reported transistor memory devices based on different polymer electrets and most of the devices can be programmed within few millisecond (ms) and the programming states can be maintained over 1000s without significant degradation and it is expected that the retention time of memory transistor based on polystyrene (PS) electret could be close to 10<sup>8</sup> s.<sup>3</sup> Hsu et al. reported the charge trapping property of pentacene transistor with polystyrene para-substituted with p-conjugated oligofluorenes as polymer electrets. They showed the p-conjugated oligofluorenes with smaller band gap can offer larger threshold voltage (Vth) shift because of the lower injection barrier for electrons.8 In polymer electrets memory devices, pentacene is commonly used as the active layer p-type semiconductor materials. 9,10 Compare with pentacene, transistors made with dinaphtho-[2,3-b:2',3'-f]-thieno[3,2-b]thiophene (DNTT) cannot only provide high field-effect mobility for high frequency operation, 11 but more importantly, DNTT device can operate under high temperature environment up to 150 °C and ambient air environment without encapsulation. 12,13

Other than memory devices, OFETs can also be used for sensing physical parameters including pressure, temperature, and light. Optical sensors for different photon wavelengths can be tuned by varying the molecular structure thus the band gap of organic semiconductors. Small molecular weight organic semiconductor phototransistors have similar photo responsivity (R—the ratio between the photogenerated current and the incident light intensity) and

molecule organic semiconductor as the charge storage material.<sup>22</sup> In LCOM, photo-generated electrons are stored in the small molecule charge trapping centers due to its low conductivity and low-lying LUMO energy level. The charge retention time and on/off ratio of the devices can be as high as  $20\,000\,\mathrm{s}$  and  $10^3$ , respectively. In this work, we combine the optical sensing and memory properties of the OFETs by using electret material and large band gap organic semiconductor to form a high performance optical programming memory transistor. We used the air stable organic semiconductor with large band gap, DNTT (3 eV), as the active layer material and PS/SiO<sub>2</sub> as the hybrid dielectric. The V<sub>th</sub> of the transistors can be altered in both positive and negative directions by applying external gate bias with light irradiation. The shift of V<sub>th</sub> shows no degradation for longer than 10<sup>4</sup> s and it is believed that the charge retention time can be longer than  $10^7$  s. The current optical memory transistor with controllable V<sub>th</sub> shift under various light intensities has responsivity of 420 A W<sup>-1</sup> and

dynamic range (DR-ratio between maximum and minimum

output signal of a sensor) to their inorganic counterparts.

Owing to the high mobility of graphene, the highest reported

R of organic transistor was graphene-based devices with a value over  $10^5\,\mathrm{A\,W^{-1}}.^{17}$  However, the DR of the graphene

transistor is very low because of the high off current in the

device. On the other hand, the small molecular weight

organic semiconductor transistors offer large light/dark

current ratio (10<sup>3</sup>–10<sup>5</sup>) (i.e., high dynamic range), but suffer from low responsivity due to their low mobility

$(0.02-0.5 \,\mathrm{cm^2\,V^{-1}\,s^{-1}})$ . Recently, several groups have

demonstrated the integration of the photosensing and mem-

ory properties of organic transistor into a single device by

maintaining the photo excited charges in the device. This

can be done by using ultrathin dielectric, <sup>19</sup> photochromic materials, <sup>20,21</sup> or charge trapping small molecule layer. <sup>22</sup>

Zhang et al. have demonstrated the light-charge organic tran-

sistor memory (LCOM) devices with the low-lying lowest

unoccupied molecular orbital (LUMO) energy level small

The cross-section SEM image together with schematic diagram of the device is shown in Fig. 1(a). The device fabrication process is described as follow. Heavily doped Si

high dynamic range of 23 bits which can be use directly as

an optical sensors and multi-level storage memories.

<sup>&</sup>lt;sup>a)</sup>Email: pklc@hku.hk

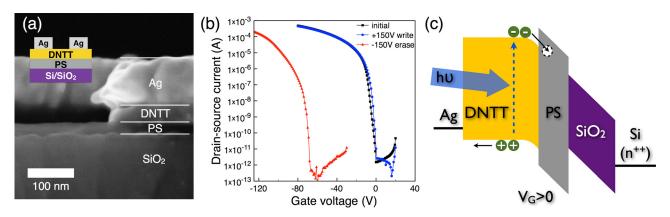

FIG. 1. (a) Cross sectional SEM image of DNTT transistor memory device in which the thickness of PS was estimated to be 30 nm. Inset is the schematic diagram of the device structure. Different from the real device, the top Ag layer thickness is intentionally increased from 50 nm to 100 nm in the sample for SEM image. (b) Transfer I-V of DNTT transistor memory device measured in the dark. (c) Schematic band diagram of transistor device working at positive gate bias and under blue light illumination, photo excited electrons in DNTT are trapped in the traps state (dotted circle) of the PS electret under positive gate bias.

wafer with thermally growth 300 nm SiO<sub>2</sub> layer is used as substrate and gate dielectric, prior to deposition, the substrate was cleaned by Deionized (DI) water and organic solvents. PS ( $_{MW} = 200000$ , Sigma-Aldrich) dissolved into toluene solvent with 0.5% weight ratio and then spun coated onto SiO<sub>2</sub> substrate with 6000 rpm for 1 min, then dried in N<sub>2</sub> atmosphere for 1 h at 90 °C. 40 nm DNTT was thermally evaporated onto the spun coated PS in vacuum chamber with base pressure  $5 \times 10^{-7}$  torr, followed by 50 nm Ag top electrodes defined by shadow mask with channel width of 2 mm and channel length of 0.1 mm. The output intensities of the blue and red high power LED (Luxeon Star) were calibrated by Newport power meter. The designed thickness of the PS layer is 30 nm and it is confirmed by the SEM image in Fig. 1(a). The transfer curve of the fresh device is indicated by the black square curve in Fig. 1(b) and the measurement was performed under dark in nitrogen glove box. It can be noticed from the curve that the turn-on of the transistor channel is near zero gate bias. Here, we apply a positive gate bias for the writing process, and negative gate bias for erasing. The biasing period for both writing and erasing is 10 s. It can be noticed from Fig. 1(b) that the current PS/DNTT optical memory device behaves completely different from the typical PS/pentacene device where positive writing bias induces right (positive) shift and negative erasing bias induces left (negative) shift to the threshold voltage. Under a -150 V erasing bias, the V<sub>th</sub> moved from -7.5 V to -73.2 V. The -63.7 V shift in threshold voltage is attributed to the filling of hole traps in the electret. However, unlike PS/pentacene memory transistor where positive shift in the transfer curves would occur, a  $+150 \,\mathrm{V}$  writing bias in the current PS/DNTT device shows negligible effect on the transfer curve of the device. Table I summarizes the

TABLE I. Transistor parameters of PS/DNTT device under different biasing conditions.

| PS/DNTT device | $\mu  (\text{cm}^2  \text{V}^{-1}  \text{s}^{-1})$ | $V_{th}(V)$ | SS(V/decade) |

|----------------|----------------------------------------------------|-------------|--------------|

| Initial        | 0.972                                              | -7.5        | 1.5          |

| Writing        | 0.981                                              | -7.4        | 1.5          |

| Erasing        | 0.961                                              | -73.2       | 1.6          |

effective carrier mobility  $(\mu)$ , subthreshold swing (SS), and V<sub>th</sub> of the device under different bias conditions. It can be notice from Table I that the mobility and SS remain the same for all the biasing conditions, V<sub>th</sub> negatively shifts only after erasing but almost remain unchanged after applying a writing bias. Weak response to the  $+150\,\mathrm{V}$  writing bias in the current device can be explained by the large electron injection barrier between the DNTT and Ag electrode which limits the number of electrons being injected (Fig. 1(c)). As a result, very little amount of electron traps in the electret layer can be filled by the electrons. To restore the positive shift in the V<sub>th</sub> under positive writing bias, electrons need to be generated in the DNTT and allowed to be trapped in the PS layer. Making use of this property in large band gap organic semiconductor, we can introduce the optical sensing property into the memory transistors and make it programmable with light.

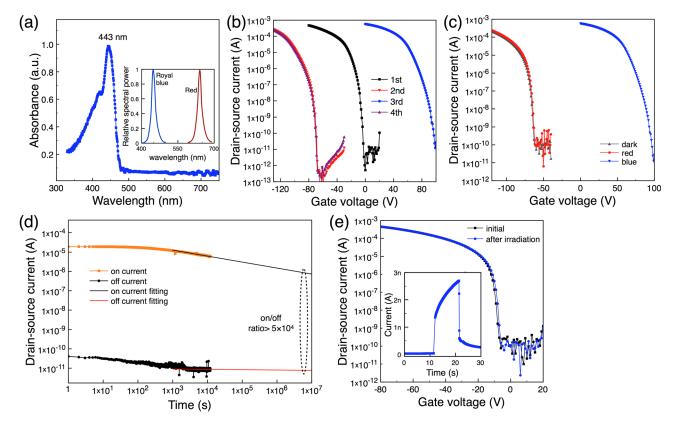

The absorption spectrum of a 40 nm DNTT thin film thermally evaporated on a quartz glass is shown in Fig. 2(a). The major absorption peak is located at 443 nm which agrees with the band gap measurement by cyclic voltammetry  $(E_g = 3 \text{ eV})$ . To test the optical sensitivity of the current memory device, we used a blue LED with emission peak at 447 nm and FWHM of 20 nm. The emission spectrums of the LED light sources are shown in the inset of Fig. 2(a). The transfer curves of the fresh device tested under the following biasing sequence (1st) fresh device, (2nd) erasing bias  $-150\,\mathrm{V}$  under dark, (3rd) writing bias  $+150\,\mathrm{V}$  under blue LED illumination, (4th) erasing bias  $-150 \,\mathrm{V}$  under dark are shown in Fig. 2(b). It is important to notice that all the transfer I-V curve measurements in the current work were performed under dark and light illumination that only occur during the writing process. By comparing the 3rd curve and the transfer curve after writing under dark in Fig. 1(b), it can be confirmed that positively shift of the threshold voltage only occur if it is programming under blue light illumination. After programming under blue illumination, the device can be simply erased by a negative bias as before (4th curve in Fig. 2(b)). To verify the electrons being injected into the PS layer are originally generated from the DNTT layer, we switched to a red LED (emission peak at 655 nm, FWHM 20 nm) as the illumination source (see inset of Fig. 2(a) for emission spectrum). Different from the programming under blue light, the results in Fig. 2(c) show no positive shift in the threshold voltage when the device is programming under red illumination. This provides direct evidence that the different  $V_{th}$  responses induced by charge injection is related to band gap of the active layer material.

After confirming the optical sensitivity in the memory transistor and the wavelength dependent programming characteristics, we take a step further to demonstrate its application potential by measuring the charge retention properties. The DNTT transistor can maintain stable charging states after programming or erasing and the I<sub>DS</sub> values are shown in Fig. 2(d). The high and low values of I<sub>DS</sub> represent the "on" and "off" state of memory transistor device. Both of the on and off currents were measured in the dark at zero gate bias. After 10<sup>4</sup> s, the on and off current only show a slight decay and the on/off ratio (larger than 10<sup>5</sup>) remains largely the same. From the extrapolation in Fig. 2(d), we believed the on and off states can retain for more than  $10^7$  s. To further confirm the long retention time is not a bulk effect in the DNTT but the presence of the electron traps in the PS, we measured the in-plane current of a DNTT thin film under the same blue LED illumination but without PS electret or gate electrode bias. The measured current in the inset of Fig. 2(e) shows a significant increase once the LED is on and it continue to increase during the 10 s of illumination. Once the LED is turned off, the current drops rapidly in less than 50 ms. It demonstrates that the long lasting on current in Fig. 2(d) is caused by the photo excited charges in the DNTT thin film under blue illumination, while the electrical field from the gate bias and the electret layer are needed for the charge injection and storage, respectively. The two transfer curves in Fig. 2(e) are measured before and after 10 s of blue LED illumination and zero gate bias applied during that 10 s, the overlapping of the two transfer curves confirms optical excitation solely cannot activate the memory property in the current PS/DNTT transistor device and electrical bias is needed.

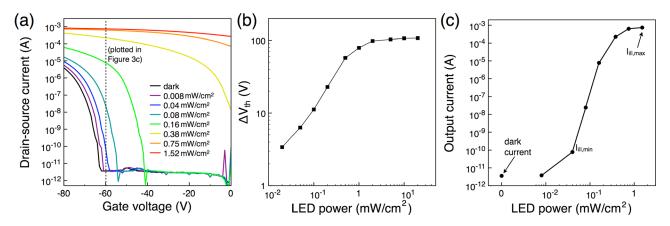

For the multi-level charge storage, we need to have adjustable shift in the threshold voltages of the transistor. We achieve this by modulating the output power of the blue LED from  $20 \,\mu\text{W} \,\text{cm}^{-2}$  to  $20 \,\text{mW} \,\text{cm}^{-2}$  while keeping the writing bias at +100 V. Fig. 3(a) shows different levels of threshold voltage shift can be obtained by varying the intensity of the blue LED. In between each transfer curve scan in Fig. 3(a), a -150 V erasing bias is applied to reset the memory transistor to the erased state. Fig. 3(b) summarizes the relationship between the shift of the threshold voltage and the LED light intensities under programing bias of  $+100 \,\mathrm{V}$ . Unlike the light-charge organic memory device based on the small molecule charge trapping layer<sup>22</sup> in which the erased state V<sub>th</sub> is close to 0 V. The holes trapping ability of PS allows the erased state started from a more negative V<sub>th</sub> value which is  $-73.2 \,\mathrm{V}$ , and thus the maximum positive  $\mathrm{V}_{\mathrm{th}}$

FIG. 2. (a) Absorbance of 40 nm DNTT thin film grown on quartz glass, inset of Fig. 2(a) shows the emission spectrum of blue and red LED light source. (b) Transfer I-V of PS/DNTT transistor memory device, 1st line is the initial state without any bias and light irradiation, 2nd line is the device erased by -150 V gate bias, 3rd line is the device writing with +150 V gate bias at the same time blue LED irradiation, 4th line is the device erased by -150 V gate bias after obtaining the 3rd line. (c) Transfer I-V of PS/DNTT device at erased state and after applied a +150 V gate bias together with red or blue light irradiation. (d) Measured retention time of DNTT transistor memory device after writing and erasing. The black and red lines are the extrapolation results. (e) Transfer I-V of PS/DNTT device before and after blue LED irradiation but without applying gate bias, inset of Fig. 2(e) shows the current response of DNTT thin film under light irradiation.

FIG. 3. (a) Transfer I-V of PS/DNTT device writing with  $+100 \, \text{V}$  gate bias and different incident light intensities, the dotted line is plotted at  $V_G = -60 \, \text{V}$  in Fig. 3(c). The device was erased by  $-150 \, \text{V}$  gate bias for  $10 \, \text{s}$  after each measurement to guarantee the same starting state for each measurement. (b) Threshold voltage shift of transistor as a function of incident LED power intensity. (c) Drain-source current value at  $V_G = -60 \, \text{V}$  obtained from Fig. 3(a) plotted against LED power intensity, the leftmost point represents the current measured in the dark.

shift is 97 V at a saturated light intensity of 20 mW cm $^{-2}$ . In the log-log plot of Fig. 3(b), the  $\Delta V_{th}$  has a linear relationship with light intensity up to 1 mW cm $^{-2}$  and the  $\Delta V_{th}$  would become saturated at high light intensity. In the linear region, there are sufficient trapping states in PS electret to trap the photo-induced charges effectively. The variation of the threshold voltage in this linear region is limited by the number of photo-induced charges in the DNTT thin film. On the other hand, the saturation of  $\Delta V_{th}$  at the higher light intensity is due to the limited number of charge trapping states in PS electret, which also limits the maximum detectable light intensity. To overcome this sensing limit in order to further extend it to higher optical intensity, new type of electret material with higher traps states density can be applied or

used lower molecular weight of PS to enhance the chain-end density for charge trapping.<sup>24</sup>

The DR value of phototransistor is an important parameter to describe the device performance. Tong and Forrest have shown an optical sensor based on subphthalocyanine (SubPc) with a dynamic range of 12 bits for 580 nm monochromic light. As mentioned earlier, the dynamic range of the photo sensor is defined as

$$DR = \log_2 \left( \frac{I_{ill,max} - I_{dark}}{I_{ill,min} - I_{dark}} \right), \tag{1}$$

where  $I_{ill,max}$  and  $I_{ill,min}$  are the maximum and minimum sensible current change under the writing bias and LED

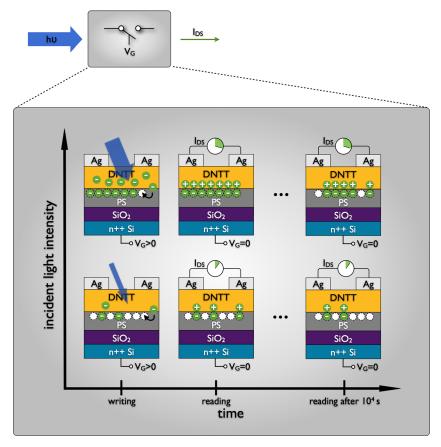

FIG. 4. Schematic diagram of a transistor based optical sensor device. The output drain-source current ( $I_{DS}$ ) is decided by the incident light energy ( $h\nu$ ). Inside the lower gray box is the schematic drawing of the optical sensing and data storage mechanisms of current transistor optical memory device. Drawing along the x-axis is the operating time sequence of the device, and y-axis represents the variation of incident light intensity.

illumination, respectively. Fig. 3(c) shows the drain-source current at  $V_G = -60 \,\mathrm{V}$  and under different light intensities (represented by the dotted line in Fig. 3(a)). Based on Fig. 3(c), the minimum sensible optical power is  $40 \,\mu\text{W}$ cm<sup>-2</sup>. If the LED power is lower than that, the current optical memory transistor is insensitive to the light. On the other extreme, the output current becomes saturated when LED power is larger than 1.52 mW cm<sup>-2</sup> due to the saturation of the transistor current. Based on Eq. (1) and the  $I_{dark} = 3.56 \times 10^{-12}$  A obtained from Fig. 3(a), the value of DR in the current phototransistor is evaluated to be DR = $\left(\frac{7.36\times10^{-4}-3.56\times10^{-12}}{7.11\times10^{-11}-3.56\times10^{-12}}\right)=23$  bits, which is a very high value for organic blue light sensor. The significant improvement of the dynamic range is attributed to the low off current in our device and the large voltage shift in the transfer curves after writing under illumination. Based on Fig. 3(c), we also calculated the responsivity of the current device at  $V_G = -60 \text{ V}$  from the equation  $R = I_{ph}/P_{opt}$ , where  $I_{ph}$  is the photo current equals to  $I_{\rm ill}$  -  $I_{\rm dark}$  and  $P_{\rm opt}$  is the incident optical power. The value of R at  $V_G = -60 \,\mathrm{V}$  and  $P_{opt} = 0.75 \,\text{mW cm}^{-2} \text{ is } 420 \,\text{A W}^{-1}.$

Comparing with the conventional phototransistor or photo diode, in which the increase of the device current is directly related to the generation of the photo excited carriers from the light input, they can provide a direct response to the light input without information storage property. In the current device structure, we intentionally use large band gap active layer to inject these photo excited charges into the electret by a writing bias. Moreover, the number of charges being trapped can be further controlled by tuning the incident light intensity at a particular writing bias. Other than optical sensing, the long retention time of the charges in the electret layer allows the devices to be used as optical memory where multi-level of information storage can be achieved by varying the light intensity. The detailed mechanism to realize the optical sensing and memory properties in the current PS/DNTT device is shown in Fig. 4. When we apply a positive writing gate bias to the device under blue light illumination, the mobile electrons generated by photon in DNTT would be captured by PS electret. The electron traps positively shift the V<sub>th</sub> (can be consider as helping the formation of the transistor channel at lower gate voltage). As a result, the I<sub>DS</sub> will increase even if gate electrode is grounded thus indicating that the device has memory property. After the reading bias, a negative erasing gate bias can reset the V<sub>th</sub> to negative value and ready for re-programming.

In summary, we demonstrate optical memory transistor with field effect carrier mobility around  $1\,\mathrm{cm}^2\,\mathrm{V}^{-1}\,\mathrm{s}^{-1}$  by intentionally using large band gap DNTT semiconductor and PS electret layer. The large memory window over 150 V and retention time longer than  $10^4\,\mathrm{s}$  demonstrates the excellent memory property in our current device. We discussed the optical programmable property of the DNTT by varying the wavelength and optical power density of the illuminating light source. The strong optical sensitivity shows great

potential for multiple states data storage in the devices. Having high trap density in the PS layer, the current optical memory transistor shows an extremely high dynamic range up to 23 bits. The high dynamic range optical sensitivity and memory property of the current transistors can shed lights on data storage applications in OFETs.

The work was supported by the Seed Funding Scheme of the University of Hong Kong (Code: 201209160033, 201210159031) and General Research Fund (Research Grants Council, HKSAR, Code: HKU 710313E).

- <sup>1</sup>T. Sekitani, T. Yokota, U. Zschieschang, H. Klauk, S. Bauer, K. Takeuchi, M. Takamiya, T. Sakurai, and T. Someya, Science **326**(5959), 1516–1519 (2009).

- <sup>2</sup>T. Someya, Y. Kato, T. Sekitani, S. Iba, Y. Noguchi, Y. Murase, H. Kawaguchi, and T. Sakurai, Proc. Natl. Acad. Sci. U.S.A. 102(35), 12321–12325 (2005).

- <sup>3</sup>K. J. Baeg, Y. Y. Noh, J. Ghim, S. J. Kang, H. Lee, and D. Y. Kim, Adv. Mater. 18(23), 3179–3183 (2006).

- <sup>4</sup>W. L. Leong, P. S. Lee, A. Lohani, Y. M. Lam, T. Chen, S. Zhang, A. Dodabalapur, and S. G. Mhaisalkar, Adv. Mater. **20**(12), 2325–2331 (2008).

- <sup>5</sup>S. M. Wang, C. W. Leung, and P. K. L. Chan, Org. Electron. **11**(6), 990–995 (2010).

- <sup>6</sup>K. J. Baeg, Y. Y. Noh, J. Ghim, B. Lim, and D. Y. Kim, Adv. Funct. Mater. **18**(22), 3678–3685 (2008).

- <sup>7</sup>K. J. Baeg, Y. Y. Noh, and D. Y. Kim, Solid-State Electron. **53**(11), 1165–1168 (2009).

- <sup>8</sup>J. C. Hsu, W. Y. Lee, H. C. Wu, K. Sugiyama, A. Hirao, and W. C. Chen, J. Mater. Chem. **22**(12), 5820–5827 (2012).

- <sup>9</sup>Y. H. Chou, H. J. Yen, C. L. Tsai, W. Y. Lee, G. S. Liou, and W. C. Chen, J. Mater. Chem. C 1(19), 3235–3243 (2013).

- <sup>10</sup>Y. L. Guo, J. Zhang, G. Yu, J. Zheng, L. Zhang, Y. Zhao, Y. G. Wen, and Y. Q. Liu, Org. Electron. 13(10), 1969–1974 (2012).

- <sup>11</sup>F. Ante, D. Kaelblein, T. Zaki, U. Zschieschang, K. Takimiya, M. Ikeda, T. Sekitani, T. Someya, J. N. Burghartz, K. Kern, and H. Klauk, Small 8(1), 73–79 (2012).

- <sup>12</sup>U. Zschieschang, F. Ante, D. Kaelblein, T. Yamamoto, K. Takimiya, H. Kuwabara, M. Ikeda, T. Sekitani, T. Someya, J. Blochwitz-Nimoth, and H. Klauk, Org. Electron. 12(8), 1370–1375 (2011).

- <sup>13</sup>K. Kuribara, H. Wang, N. Uchiyama, K. Fukuda, T. Yokota, U. Zschieschang, C. Jaye, D. Fischer, H. Klauk, T. Yamamoto, K. Takimiya, M. Ikeda, H. Kuwabara, T. Sekitani, Y. L. Loo, and T. Someya, Nat. Commun. 3, 723 (2012).

- <sup>14</sup>X. C. Ren, P. K. L. Chan, J. B. Lu, B. L. Huang, and C. W. Leung, Adv. Mater. 25(9), 1291–1295 (2013).

- <sup>15</sup>X. R. Tong and S. R. Forrest, Org. Electron. **12**(11), 1822–1825 (2011).

- <sup>16</sup>K. J. Baeg, M. Binda, D. Natali, M. Caironi, and Y. Y. Noh, Adv. Mater. 25(31), 4267–4295 (2013).

- <sup>17</sup>Z. H. Sun, Z. K. Liu, J. H. Li, G. A. Tai, S. P. Lau, and F. Yan, Adv. Mater. 24(43), 5878–5883 (2012).

- <sup>18</sup>Y. Y. Noh, D. Y. Kim, and K. Yase, J. Appl. Phys. 98(7), 074505 (2005).

- <sup>19</sup>W. Wang, D. G. Ma, and Q. Gao, IEEE Trans. Electron Devices **59**(5), 1510–1513 (2012).

- <sup>20</sup>Y. Ishiguro, R. Hayakawa, T. Yasuda, T. Chikyow, and Y. Wakayama, ACS Appl. Mater. Interfaces 5(19), 9726–9731 (2013).

- <sup>21</sup>R. Hayakawa, K. Higashiguchi, K. Matsuda, T. Chikyow, and Y. Wakayama, ACS Appl. Mater. Interfaces 5(9), 3625–3630 (2013).

- <sup>22</sup>L. Zhang, T. Wu, Y. L. Guo, Y. Zhao, X. N. Sun, Y. G. Wen, G. Yu, and Y. Q. Liu, Sci. Rep. 3, 1080 (2013).

- <sup>23</sup>U. Zschieschang, F. Ante, T. Yamamoto, K. Takimiya, H. Kuwabara, M. Ikeda, T. Sekitani, T. Someya, K. Kern, and H. Klauk, Adv. Mater. 22(9), 982–985 (2010).

- <sup>24</sup>H. H. Choi, W. H. Lee, and K. Cho, Adv. Funct. Mater. 22(22), 4833–4839 (2012).