# Fabrication and Electrical Characterization of MONOS Memory with Novel High-κ Gate Stack

L. Liu, J. P. Xu\*, C. L. Chan, P. T. Lai\*

Abstract - A novel high-к gate stack structure with HfON/SiO<sub>2</sub> as dual tunneling layer (DTL), AlN as charge storage layer (CSL) and HfAlO as blocking layer (BL) is proposed to prepare the chargetrapping type of MONOS non-volatile memory device by employing in-situ sputtering method. The memory window, program/erase and retention properties are investigated and compared with similar gate stack structure with Si<sub>3</sub>N<sub>4</sub>/SiO<sub>2</sub> as DTL, HfO<sub>2</sub> as CSL and Al<sub>2</sub>O<sub>3</sub> as BL. Results show a large memory window of 3.55 V at P/E voltage of +8 V/-15 V, high retention program/erase speed and good characteristic can be achieved using the novel Au/ HfAlO/AlN/(HfON/SiO<sub>2</sub>)/Si gate stack structure. The main mechanisms lie in the enhanced electron injection through the high-k HfON/SiO2 DTL, high trapping efficiency of the high-κ AlN material and effective blocking role of the high-κ HfAlO BL.

Keywords: MONOS memory, high-κ gate stack, charge storage layer, tunneling layer, blocking layer

### I. INTRODUCTION

The challenges for non-volatile memory devices are to achieve fast program/erase (P/E) speed at low operating voltage, large memory window and good 10-year data retention simultaneously [1]. Because of the advantages in scaling, simple fabrication process and robustness against defect-related leakage, metal—oxide-nitride-oxide-silicon (MONOS) memory devices become attractive candidates [2]. Extensive researches have been performed in recent years, involving the use of high-κ HfO<sub>2</sub> [2-3] or AlN [1], [4-5] as charge storage layer (CSL), the use of Si<sub>3</sub>N<sub>4</sub>/SiO<sub>2</sub> [2] or ZrO<sub>2</sub>/SiO<sub>2</sub> [6] as dual tunneling layer (DTL) to enhance the tunneling

current, the use of Al<sub>2</sub>O<sub>3</sub> as the blocking layer (BL) instead of SiO<sub>2</sub> [7-8] and the use of high-work-function metal gate [9-10] for suppressing electron injection from gate electrode. However, less work concentrated on combining the advantages of high-k BL and CSL with the dual high-κ/SiO<sub>2</sub> band-engineered tunneling layer. In this paper, we report a novel high-κ gate stack structure Au/HfAlO/AlN/(HfON/SiO<sub>2</sub>)/Si for memory application which combines a new DTL of HfON/SiO<sub>2</sub> with the high-κ HfAlO BL and AlN CSL to comprehensively improve the performances of the devices. The electrical characteristics of this novel device are evaluated through comparison with the similar high-κ gate stack structure of Au/Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub>/ (Si<sub>3</sub>N<sub>4</sub>/SiO<sub>2</sub>)/Si. Experimental results indicate that large memory window, fast program/erase speed at low operation voltage and good retention property can be obtained using this novel high-κ gate stack structure.

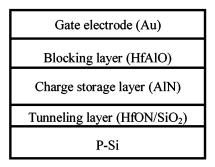

Fig. 1 Schematic cross-section of proposed gate stack.

# II. DEVICE FABRICATION

Fig. 1 is the schematic cross-section of gate stack of MONOS memory device. To improve the P/E characteristics of MONOS flash memory device, a new high-κ stack gate dielectric structure of Au/HfAlO/AlN/ (HfON/SiO<sub>2</sub>)/Si is proposed, with HfON/SiO<sub>2</sub> as double tunneling layer, AlN as charge-storage layer and HfAlO

L. Liu and J. P. Xu are with Department of Electronic Science and Technology, Huazhong University of Science and Technology, Wuhan 430074, P. R. China

<sup>\*</sup>E-mail: jpxu@mail.hust.edu.cn

P. T. Lai and C. L. Chan are with Department of Electrical & Electronic Engineering, the University of Hong Kong, Pokfulam Road, Hong Kong

<sup>\*</sup>E-mail: laip@eee.hku.hk

<sup>978-1-4244-4298-0/09/\$25.00 ©2009</sup> IEEE

as block layer, as shown in Table I. These high-κ dielectrics were consecutively deposited in-situ by reactive sputtering (or co-sputtering) method using Denton Vacuum Discovery Deposition System at room temperature. First, a 3-nm thick SiO<sub>2</sub> was thermally grown in dry O<sub>2</sub> at 900 °C on p-type Si substrate with a resistivity of 5-10 Ωcm. Then, a nominal 6-nm HfON was deposited by reactive sputtering of Hf in an Ar/N<sub>2</sub> (24:6) ambient, followed by the deposition of a nominal 12-nm AlN by reactive sputtering of Al in an Ar/N<sub>2</sub> (24:6) ambient, followed by the deposition of a nominal 10-nm HfAlO by reactive co-sputtering of HfO2 and Al in Ar ambient (24 sccm). A post-deposition annealing (PDA) was carried out in N2 at 700 °C for 60 s to the dielectric quality. For densification and high-quality tunneling layer and especially blocking layer, their deposition rates were set at low values of 0.125 nm/min and 0.1 nm/min respectively. On the contrary, the charge-storage layer was deposited at a higher rate of 2 nm/min so that more deep-level traps can be formed during deposition. For comparison, a normal high-κ gate dielectric stack of  $Au/Al_2O_3/HfO_2/(Si_3N_4/SiO_2)/Si$  (as control sample) was prepared using the same deposition procedure, with a nominal 6-nm Si<sub>3</sub>N<sub>4</sub> RF-deposited using Si<sub>3</sub>N<sub>4</sub> target at a rate of 0.1 nm/min in Ar (24 sccm), a nominal 12-nm HfO<sub>2</sub> RF-deposited using HfO<sub>2</sub> target at a rate of 0.17 nm/min in Ar (24 sccm) and a nominal 10-nm Al<sub>2</sub>O<sub>3</sub> RF-sputtered using Al target at a rate of 0.084 nm/min in Ar/O<sub>2</sub> (24/6) ambient. For avoiding the crystallization of HfO<sub>2</sub>, the PDA was performed at 500 °C for 120 s in N<sub>2</sub>. Finally, the high-work-function Au was evaporated and patterned as gate electrode and then Al was evaporated as back electrode, followed by forming-gas annealing which was completed in H<sub>2</sub>/N<sub>2</sub> (5% H<sub>2</sub>) for 20 min at 400 °C.

memory For evaluating the window and programming/erasing characteristics, high-frequency (1-MHz) C-V curves were measured using HP4284A precision LCR meter, and the programming/erasing voltages were applied by HP4156A semiconductor parameter analyzer. The flat-band voltage was extracted from the measured C-V curves by assuming  $C_{fb}/C_{ox} = 0.5$  ( $C_{fb}$  and  $C_{ox}$  are the flat-band and oxide (or accumulation) capacitances respectively).

Table I

HIGH-K GATE DIELECTRIC STACK STRUCTURE

|                      | New device              | Control device           |  |  |

|----------------------|-------------------------|--------------------------|--|--|

| Gate                 | Au                      |                          |  |  |

| Blocking layer       | HfAlO(10 nm)            | $Al_2O_3(10 \text{ nm})$ |  |  |

| Charge-storage layer | AlN (12 nm)             | $HfO_2$ (12 nm)          |  |  |

|                      | HfON (6 nm)             | $Si_3N_4$ (6 nm)         |  |  |

| Dual tunneling layer | SiO <sub>2</sub> (3 nm) | SiO <sub>2</sub> (3 nm)  |  |  |

# III. RESULTS AND DISCUSSION

#### A. Memory window and program-erase performance

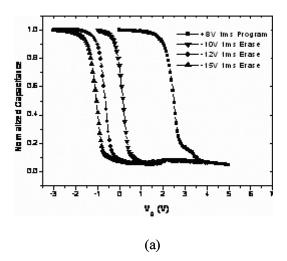

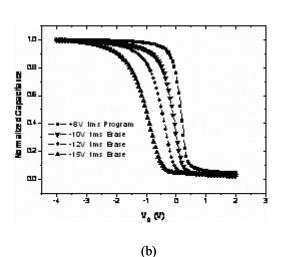

The memory window is determined from shift of the flat-band voltage which is extracted from the measured C-V curves under different P/E voltages. As can be seen from Fig. 2, the memory window of the novel device at P/E voltages of + 8 V/- 10 V, + 8 V/- 12 V, + 8 V/- 15 V is 2.35 V, 3.15 V and 3.55 V, respectively, and it becomes 0.35 V, 0.75 V and 1.35 V under the same P/E voltages for the control device. The larger memory window even at low program voltage for the novel device than the control device should be ascribed to the high trapping capability of high-κ AlN charge-storage layer [4] and suitable double tunneling layer structure.

The program/erase performances are evaluated in terms of the flatband-voltage change ( $\Delta V_{fb}$ ) by applying a P/E voltage of +/- 10 V or 15 V for 100  $\mu s$ . As shown in Table II, larger  $\Delta V_{fb}$  is obtained for the novel device than the control device under both the same program voltage and the same erase voltage, indicating higher program and erase speeds for the former than the latter. Since the P/E mechanisms are controlled by FN tunneling, the faster programming is due to the higher  $\kappa$ value of HfON than Si<sub>3</sub>N<sub>4</sub>, which results in higher electric field in SiO<sub>2</sub> and thus enhanced carrier injection from the substrate to the charge-storage layer, and on the other hand, it probably means a smaller  $\Delta E_C$  of HfON-Si than Si<sub>3</sub>N<sub>4</sub>-Si. The high erase speed is attributed to the effective blocking role of the high-κ HfAlO blocking layer, which reduces the electron injection from the gate into the AlN charge storage layer during erasing, and small equivalent oxide thickness of the HfON/SiO<sub>2</sub> double tunneling layer, which enhances the hole injection from the substrate.

Fig. 2 C-V curve of the novel device (a) and control device (b) at different P/E voltages for 1 ms.

TABLE II  $\begin{tabular}{ll} CHANGE OF $V_{fb}$ AFTER P/E OPERATION \\ FOR 100 $\mu s$ \end{tabular}$

|                                  | Program |        | Erase  |        |

|----------------------------------|---------|--------|--------|--------|

|                                  | + 10 V  | + 15 V | - 10 V | - 15 V |

| Novel device $\Delta V_{fb}/V$   | + 0.9   | + 1.35 | - 1.05 | - 1.4  |

| Control device $\Delta V_{fb}/V$ | + 0.4   | + 0.7  | - 0.5  | - 1.05 |

## B. Program-erase retention characteristics

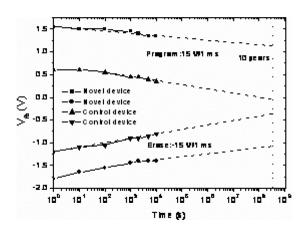

Long retention after programming or erasing is important for non-volatile memory devices. Presented in Fig. 3 is the retention characteristic of  $+V_{fb}$  and  $-V_{fb}$  extracted from the C-V curves of the two devices

measured after programming or erasing at +15 V or -15 V for 1 ms. The retention characteristic is evaluated by measuring the C-V curves after removing the program or erase voltage for 1 - 10000 s. Obviously, a small  $V_{fb}$  variation is observed for the novel device with an initial memory window of 3.35 V, which gives an extrapolated 10-year memory window of 2.1 V. The good retention characteristics are due to the strong Al-N bonds related to better trapping capability [5] and deeper trap levels. Also, the suitable high- $\kappa$  HfAlO blocking layer and HfON tunneling layer, which have reasonable barrier height when contacting with AlN respectively, are responsible for the good retention.

Fig. 3 Comparison of retention property for the two devices after programming or erasing at +15 V or -15 V for 1 ms.

#### IV. CONCLUSION

A novel high-k gate stack structure of Au/HfAlO/ AlN/(HfON/SiO<sub>2</sub>)/Si for non-volatile MONOS memory device application is fabricated by in-situ sputtering. Comparing with the Au/Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub>/(Si<sub>3</sub>N<sub>4</sub>/SiO<sub>2</sub>)/Si gate stack structure, the novel device exhibits a large memory window of 3.55 V at a P/E voltage of +8 V/-15 V, high program/erase speed and good retention characteristic with an extrapolated 10-year memory window of 2.1 V. The large memory window is related to the effective AlN charge storage layer with more deep-level traps. High P/E speed is attributed to the suitable HfON tunneling layer with higher k value and small conduction-band offset, and effective blocking role of the HfAlO blocking layer. Good retention property lies in the reasonable barrier-height match between the AlN charge-storage layer, HfAlO blocking layer and HfON tunneling layer.

Therefore, the Au/HfAlO/AlN/(HfON/SiO<sub>2</sub>)/Si gate stack structure is a promising candidate for making high-performance non-volatile MONOS flash memory devices.

# **ACKNOWLEDGES**

This work is financially supported by the National Natural Science Foundation of China (Grant no. 60976091), and the University Development Fund (Nanotechnology Research Institute, 00600009) of the University of Hong Kong.

#### **REFERENCES**

- [1] C. H. Lai, C.C. Huang et al, "Fast high-κ AlN MONOS memory with large memory window and good retention," IEEE Device Research Conference Dig., vol. 1, p. 99, 2005.

- [2] Y. Q. Wang, W. S. Hwang et al, "Electrical characteristics of memory devices with a high-κ HfO<sub>2</sub> trapping layer and dual Si<sub>3</sub>N<sub>4</sub>/SiO<sub>2</sub> tunneling layer," IEEE Transactions on Electron Devices, vol. 54, p. 2699, 2007.

- [3] Gang Zhang, Xinpeng Wang, Won Jong Yoo, Mingfu Li, "Spatial distribution of charge traps in a SONOS-type flash memory using a high-κ trapping layer," IEEE Transactions on Electron Devices, vol. 54, p. 3317, 2007.

- [4] Lai, C. H. et al, "A novel program-erasable high-κ AlN-Si MIS capacitor," IEEE Electron Device Letters, vol. 26, p. 148, 2005.

- [5] Chin, A. et al, "A novel program erasable high-κ AlN capacitor with memory functions," Non-Volatile Memory Tech. Symp. Dig., p. 18, 2004.

- [6] B. Govoreanu, P. Blomme et al, "Enhanced tunneling current effect for nonvolatile memory applications," Jpn. J. Appl. Phys., vol. 42, p. 2020, 2003.

- [7] C. H. Lee et al, "Charge-trapping device structure of SiO<sub>2</sub>/Si<sub>3</sub>N<sub>4</sub>/high-κ dielectric Al<sub>2</sub>O<sub>3</sub> for high-density flash memory," Appl. Phys. Lett., vol. 86, p. 2908, 2005.

- [8] M. Specht, H. Reisinger et al, "Retention time of novel charge trapping memories using Al<sub>2</sub>O<sub>3</sub> dielectrics," IEEE ESSDERC, P. 16, 2003.

- [9] C. H. Lee, K. I. Choi et al, "A novel SONOS structure of SiO<sub>2</sub>/SiN/Al<sub>2</sub>O<sub>3</sub> with TaN metal gate for multi-giga bit flash memories," IEDM Tech. Dig., p. 26.5.1, 2003.

- [10] Sanghun Jeon, Jeong Hee Han et al, "High work-function metal gate and high-κ dielectrics for charge trap flash memory device applications" IEEE ESSDERC, p. 325, 2005.