# Low-Voltage Polymer Thin-Film Transistors with High-k HfTiO Gate Dielectric Annealed in NH<sub>3</sub> or N<sub>2</sub>

L. F. Deng, H. W. Choi, P. T. Lai\*, Y. R. Liu and J. P. Xu

Abstract - OTFTs with P3HT as organic semiconductor and HfTiO as gate dielectric have been studied in this work. The HfTiO dielectric film was prepared by RF sputtering of Hf and DC sputtering of Ti at room temperature. Subsequently, the dielectric film was annealed in an NH<sub>3</sub> or N<sub>2</sub> ambient at 200 °C. Then a layer of OTS was deposited by spin-coating method to improve the surface characteristics of the gate dielectric. Afterwards, P3HT was deposited by spin-coating method. The OTFTs were characterized by I-V measurement and 1/f noise measurement. The OTFT with gate dielectric annealed in NH<sub>3</sub> displays higher carrier mobility, smaller threshold voltage, smaller sub-threshold swing, and lower 1/f noise level than the OTFT annealed in N2. Moreover, the HfTiO dielectric film annealed in NH3 shows higher dielectric constant. In summary, HfTiO film annealed in NH3 at low temperature is a promising candidate to act as the gate dielectric of high-quality low-voltage OTFTs.

## I. Introduction

Organic thin-film transistors (OTFTs) have got wide attention due to their potential to be applied in large-area flat-panel display, RF-ID card, electronic paper, and so on. OTFTs based on SiO<sub>2</sub> dielectric with pentacene as organic semiconductor have achieved performance which is comparable to or even exceeds that of amorphous-silicon thin-film transistors [1]. In comparison with their inorganic counterparts, organic thin-film transistors have a lot of advantages. OTFTs can be fabricated in large area, which is advantageous for the fabrication of large-area displays [2]. Besides, the fabrication temperature of OTFTs is low, which means that they can be realized on flexible substrate such as plastics. Moreover, since shadow mask can be used for the fabrication of OTFTs and lithography is unnecessary, the cost of the devices is lowered.

# Organic semiconductor material to serve as the active

L. F. Deng, H. W. Choi and P. T. Lai are with the Electrical and Electronic Department, the University of Hong Kong, Hong Kong. Y. R. Liu is with School of Electronic and Information Engineering, South China University of Technology, Guangzhou, 510640, China. J. P. Xu is with Department of Electronic Science & Technology, Huazhong University of Science and Technology, Wuhan.

\* E-mail: laip@eee.hku.hk

layer mainly includes two types. One is small-molecule organic material such as pentacene, rubrene [3], tetracene [4]. The other type is polymer semiconductor material represented by poly 3-hexylthiophene (P3HT) polydiacetylene. polythiophenes [6] and small-molecule organic material, sublimation is usually used for the deposition of organic film. By contrast, simpler spin-coating method can be used for forming the polymer organic semiconductor film. Compared with sublimation, spin-coating method real room-temperature fabrication process.

Although OTFTs have the potential to be widely used, challenges exist. Right now, the operating voltage of OTFTs with SiO<sub>2</sub> as gate dielectric is usually very high, typically 15 V or even higher. Large operating voltage often leads to high power consumption, which is unacceptable for OTFTs used in portable equipment. High operating voltage results from the small capacitance per unit area of the gate dielectric in OTFTs. There are two possible means to reduce the operating voltage of OTFTs. The first one is to scale down the thickness of the gate dielectric, but this usually causes large gate leakage of the OTFTs. The other way is to use gate insulator with high dielectric constant (k) to replace the low-k SiO<sub>2</sub>. Hafnium (Hf)-based oxides have been used in the 45-nm inorganic CMOS technology due to their excellent performance [7]. Therefore, in this study, HfTiO with very high k value is introduced as the gate dielectric of OTFTs.

### II. EXPERIMENTAL DETAILS

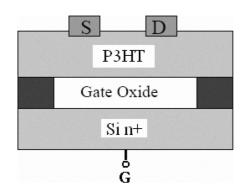

The cross sectional view of OTFTs is displayed in Fig. 1.

Fig. 1. Cross-sectional view of top-contact OTFTs

The substrate was n-type silicon <100> with a resistivity of  $0.5 \sim 0.7 \ \Omega \text{cm}$ . Firstly, the wafer was cleaned according to the standard RCA method, and the oxide on the substrate was removed by 5% hydrofluoric acid. Then, the wafer was washed by deionized water and dried in a nitrogen stream. Subsequently, the wafer was inserted into the chamber of Denton Vacuum LLC Discovery 635 to deposit a layer of HfTiO film by sputtering method at room temperature. Hf and Ti targets were used in RF mode (30 W) and DC mode (0.1 A) respectively. Argon and oxygen were injected into the chamber with flow rate of 24 sccm and 3 sccm respectively. Nitridation method was used to improve the performance of the dielectric film. In this study, the sample was annealed in NH<sub>3</sub>, and compared with another annealed in N2. For both gases, annealing temperature was 200 °C and flow rate was 1000 mL/min. Next hydrofluoric acid (20% concentration) was used to remove the back oxide on the substrate. Then OTS (octadecyltrichlorosilane) solution (OTS: toluene=1mL: 10mL) was put on the dielectric by spin-coating method to improve the surface characteristics of the dielectric film. The OTS film was hardened by drying the film at 95 °C for 5 minutes in air. Then P3HT solution (P3HT: 1,2-dichlorobenzene = 10mg:1mL) was added by spin-coating method and dried at 95 °C for 5 minutes in air. For both spin-coating processes, spinning speed was 2000 r/min and spinning time was 1 min. Next, gold was evaporated on the organic layer through a shadow mask to form the drain and source electrodes of the transistors after the vacuum was below 8×10<sup>-6</sup> Torr. Finally, the transistors were covered with a thin layer of wax to prevent them from degradation in air.

After completion of device fabrication, the transistors were measured by HP4145B Semiconductor Parameter Analyzer, Berkeley Technology Associates FET Noise Analyzer Model 9603 and HP 35665A Dynamic Signal Analyzer to get their I-V and 1/f noise characteristics. The dielectric constant of the HfTiO film was calculated by measuring the capacitance of an MOS structure formed by lithography. Also, the thickness of the film was characterized by an ellipsometer made by J.A.Woollam Co., Inc.

# III. RESULTS AND DISCUSSION

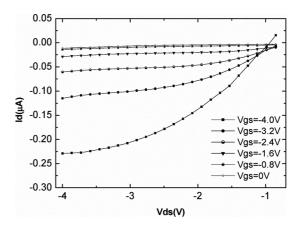

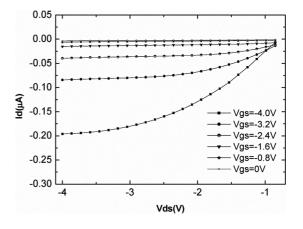

Fig. 2 and Fig. 3 show the output characteristics of the OTFTs with the gate dielectrics annealed in  $N_2$  and  $NH_3$  respectively. From the output characteristics, the OTFTs can operate at voltage as low as 4 V, which is due to the use of high-k dielectric film.

Carrier mobility and threshold voltage are key parameters for evaluating the electrical performance of OTFTs. According to the current-voltage relation for field-effect transistor operating in saturation region,

$$I_{ds} = -\frac{W}{2L} \mu C_{ox} (V_{gs} - V_{th})^2$$

(1)

which can be re-written as

$$\sqrt{-I_{ds}} = \sqrt{\frac{W}{2L}} \,\mu C_{ox} \left( V_{gs} - V_{th} \right) \tag{2}$$

or

$$\mu = \frac{2L}{WC_{ox}} \left( \frac{\partial \sqrt{-I_{ds}}}{\partial V_{gs}} \right)^2 \tag{3}$$

where W and L are the width and length of the channel respectively;  $C_{ox}$  is the capacitance per unit area of the gate dielectric. So, the carrier mobility can be obtained from (3). The threshold voltage can be derived through extrapolating the  $\sqrt{-I_{ds}}=f(V_{gs})$  graph to the x-axis, and the interception at the x-axis gives the threshold voltage. In the case of OTFT with NH<sub>3</sub>-annealed dielectric, the mobility is  $0.0119 \ cm^2/V_S$ , which is higher than  $0.0094 \ cm^2/V_S$  of the OTFT with N<sub>2</sub>-annealed gate dielectric. In terms of threshold voltage, the value for the former is -0.23 V, which is lower than 0.34 for the latter.

Fig. 2. Output characteristics of OTFT with  $N_2$ -annealed HfTiO gate dielectric

Fig. 3. Output characteristics of OTFT with NH<sub>3</sub>-annealed HfTiO gate dielectric

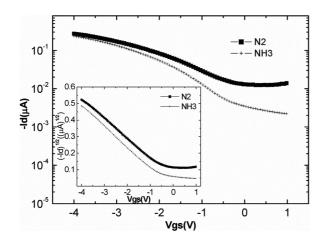

Fig. 4. Transfer characteristics of the OTFTs with HfTiO gate dielectric annealed in N<sub>2</sub> or NH<sub>3</sub>. Inset is the (-Id)<sup>1/2</sup>-Vgs curve.

In order to further evaluate the switching characteristics of OTFTs, sub-threshold swing (SS) is calculated according to

$$SS = \frac{1}{\frac{\partial Log(-I_d)}{\partial V_g}} \tag{4}$$

From Fig. 4 the sub-threshold swing for the OTFT with  $NH_3$ -annealed dielectric is 1.35 V/decade, which is smaller than 1.98 V/decade of the OTFT with  $N_2$ -annealed dielectric. Consequently, OTFT with  $NH_3$ -annealed gate dielectric shows better switching characteristics than its  $N_2$ -annealed counterpart.

1/f noise is an important parameter for further evaluating the electrical performance of the OTFTs. Noise spectral density and Hooge parameter are usually expressed as [8]

$$\frac{S_{id}(f)}{I_d^2} = \frac{\alpha}{Nf} \tag{5}$$

where  $S_{id}(f)$  is the noise spectral density corresponding to the frequency f;  $\alpha$  is the Hooge parameter;  $I_d$  is the current in the channel; N is the total number of carriers in the channel. In the case of organic thin-film transistors, formula (5) can be approximated as [9]

$$\alpha = \frac{f^{\gamma} S_{id}(f) L^2}{e \mu V_{ds} I_d} \tag{6}$$

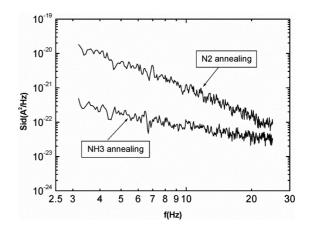

where  $\gamma$  is the slope of the noise spectrum in logarithmic scale; e is the electron charge. After calculation, the Hooge parameter for the OTFT with NH<sub>3</sub>-annealed HfTiO film is 9.00, which is much smaller than  $7.33 \times 10^3$  of the OTFT N<sub>2</sub>-annealed HfTiO film. On the other hand, the

noise spectral density for the  $NH_3$ -annealed OTFT is approximately one order lower than that of the  $N_2$ -annealed OTFT. This means that the interfacial properties between the gate dielectric and organic semiconductor of the  $NH_3$ -annealed OTFT are superior to those of the  $N_2$ -annealed OTFT.

Fig. 5. 1/f noise comparison of the OTFTs with HfTiO gate dielectric annealed in  $N_2$  or  $NH_3$

TABLE I

DEVICE PARAMETERS OF THE OTFTS ANNEALED IN

N2 OR NH3

| -                                   | Annealing gas        |                 |

|-------------------------------------|----------------------|-----------------|

|                                     | $N_2$                | NH <sub>3</sub> |

| $C_{ox}(\mu F/cm^2)$                | 0.396                | 0.394           |

| $t_{ox}(nm)$                        | 34.6                 | 35.3            |

| k                                   | 15.5                 | 15.7            |

| $\mu(cm^2/Vs)$                      | 0.0094               | 0.0119          |

| $V_{th}(V)$                         | 0.341                | -0.228          |

| SS (V/decade)                       | 1.99                 | 1.35            |

| on/off ratio                        | 22.2                 | 107             |

| $Id\big _{Vds=Vgs=-4V} (10^{-7} A)$ | 2.29                 | 1.96            |

| α                                   | $7.33 \times 10^{3}$ | 9.00            |

In summary, the OTFT with NH<sub>3</sub>-annealed dielectric has higher carrier mobility, smaller sub-threshold swing, smaller noise level than its counterpart with N<sub>2</sub>-annealed dielectric. Moreover from Table 1, the former has a much larger on/off current ratio than the latter. All these can be attributed to the lower trap density in the channel / at the surface of the gate dielectric for the former than the latter because both the N and H atoms dissociated from NH<sub>3</sub> can passivate these traps inside the device. Also, the dielectric constant of the NH<sub>3</sub>-annealed HfTiO film is slightly larger than that of the N<sub>2</sub>-annealed HfTiO film. This results from N atoms entering the dielectric film during the NH<sub>3</sub> annealing, hence enhancing the dielectric constant of the insulator.

# IV. CONCLUSION

P3HT OTFT with HfTiO gate dielectric annealed in NH<sub>3</sub> displays higher carrier mobility, on/off current ratio than its counterpart annealed in N<sub>2</sub>. Moreover, the former shows smaller threshold voltage, 1/f noise level and sub-threshold swing than the latter. As a result, The former has better electrical performance than the latter due to passivation of dielectric surface by NH<sub>3</sub> gas. The dielectric constant of the HfTiO film prepared by sputtering method is as high as around 15. In summary, HfTiO dielectric prepared by sputtering method and annealed in NH<sub>3</sub> at low temperature is a promising candidate to act as the gate dielectric of high-performance low-voltage organic thin-film transistors.

### ACKNOWLEDGEMENT

This work is supported by the RGC of HKSAR, China (Project No. HKU 7133/07E), the URC for Seed Fund for Strategic Research Theme of HKU on Molecular Materials, and the University Development Fund (Nanotechnology Research Institute, 00600009) of the University of Hong Kong.

### REFERENCES

- Jin Jang, and Seung Hoon Han, "High-performance OTFT and its application," Current Applied Physics, vol.6, p.e17, 2006

- [2] C. D. Dimitrakopoulos, and P. R. L. Malenfant, "Organic thin film transistors for large area electronics," Adv. Mater., vol.14, p.99, 2002.

- [3] Se-W. Park, Jung Min Hwang, Jeong-M. Choi, D. K. Hwang, M. S. Oh, Jae Hoon Kim, and Seongil Im,

- "Rubrene thin-film transistors with crystalline and amorphous channels," *Appl. Phys. Lett.*, vol.90, p. 153512.2007.

- [4] Young-Se Jang, Hoon-Seok Seo, Ying Zhang and Jong-Ho Choi, "Characteristics of tetracene-based field-effect transistors on pretreated surfaces," *Organic Electronics*, vol.10, p.222, 2009.

- [5] S.M. Goetz, C.M. Erlen, H. Grothe, B. Wolf, P. Lugli, and G. Scarpa, "Organic field-effect transistors for biosensing applications", *Organic Electronics*, vol.10, p.573, 2009.

- [6] B. S. Ong, Y. Wu, P. Liu, and S. Gardner, "Structurally Ordered Polythiophene Nanoparticles for High-Performance Organic Thin-Film Transistors", Adv. Mater., vol.17, p.1141, 2005.

- [7] Huey-liang Hwang, C.W. Wang, K.H. Chang, C.H. Tsai, K.C. Leou, Kuei-Shu, Chang-Liao, Chun-Chang Lu, S.C. Chang, F.C. Chiu, C.H. Liu, Albert Chin, Kow-Ming Chang, and Bwo-Ning Chen, "National Project on 45 to 32 nm Metal Oxide Semiconductor Field Effect Transistors for Next Century IC Fabrications", 2008 IEEE International Conference on Electron Devices and Solid-State Circuits, EDSSC, art.no.4760691, 2008.

- [8] F. N. Hooge, "1/f noise source," IEEE TRANSACTIONS ON ELECTRON DEVICES. Vol.41, p.1926, 1994.

- [9] M. J. Deen, O. Marinov, J. F. Yu, S. Holdcroft, and W. Woods, "Low-Frequency Noise in Polymer Transistors," IEEE TRANSACTIONS ON ELECTRON DEVICES, vol.48, p.1688,2001.