# Low-Operating-Voltage Polymer Thin-Film Transistors Based on Poly(3-Hexylthiophene) With Hafnium Oxide as the Gate Dielectric

Y. R. Liu, L. F. Deng, R. H. Yao, and P. T. Lai, Senior Member, IEEE

Abstract—The effects of hafnium oxide (HfO2) gate dielectric annealing treatment in oxygen (O<sub>2</sub>) and ammonia (NH<sub>3</sub>) ambient on the electrical performance of polymer thin-film transistors (PTFTs) based on poly(3-hexylthiophene) are investigated. The PTFTs with HfO<sub>2</sub> gate dielectric and also octadecyltrichlorosilane surface modification, prepared by spin-coating process, exhibit good performance, such as a small threshold voltage of -0.5 Vand an operating voltage as low as -4 V. Results indicate that the PTFT with NH<sub>3</sub>-annealed HfO<sub>2</sub> shows higher carrier mobility, larger ON/OFF current ratio, smaller subthreshold swing, and lower threshold voltage than the PTFT with O2-annealed HfO<sub>2</sub>. Capacitance-voltage analysis for metal-polymer-oxidesilicon structures indicates that the better electrical performance of the PTFT with NH<sub>3</sub>-annealed HfO<sub>2</sub> is attributed to improved dielectric/polymer interface and reduced series resistance in the transistor.

Index Terms—Capacitance-voltage characteristics, high-k, poly(3-hexylthiophene) (P3HT), polymer thin-film transistor (PTFT).

# I. INTRODUCTION

In THE last two decades, solution-processed polymer thin-film transistors (PTFTs) have attracted much attention due to their potential applications in a variety of large-area electronic applications, such as flat-panel display, low-cost flexible integrated circuits, and sensors [1]–[3]. Among various solution-processed polymer semiconductors that are currently in use, poly(3-hexylthiophene) (P3HT) has been the most extensively studied p-type polymer material due to its relative high carrier mobility [4], [5]. So far, many researches of P3HT PTFTs have been focusing on the enhancement of field-effect mobility and the improvement of air stability by material and device engineering [6], [7]. Moreover, most of the studies on P3HT PTFTs were done by using silicon dioxide (SiO<sub>2</sub>) as gate dielectric [8]–[10]. However, conventional PTFTs require a

high operating voltage and show a large threshold voltage and a poor subthreshold swing (SS), which limit their suitability in integrated-circuit applications. In addition, high operating voltage usually leads to high power consumption and causes inconvenience to the development of portable equipment. In order to address these issues, high-k gate dielectrics [e.g., tantalum pentoxide (Ta<sub>2</sub>O<sub>5</sub>)] have been applied in PTFTs to obtain a higher drive current at lower voltage operation [11], [12]. Hafnium-based oxides [e.g., HfO<sub>2</sub> and hafnium oxynitride (HfON)] are being actively investigated to act as the gate dielectric of inorganic transistors due to their better interface quality with the silicon semiconductor [13], [14] as well as higher dielectric constant. The performance of PTFTs depends particularly on the quality of the interface between the gate dielectric and polymer semiconductor, as well as the electrical properties of the polymer semiconductor thin film. In order to decrease the gate-oxide leakage and acquire highquality interface, one common method is performing a proper passivation treatment on the gate dielectric prior to spin-coating the polymer semiconductor layer. In this paper, in order to realize a low operating voltage and a small threshold voltage, HfO<sub>2</sub> dielectric layer prepared by sputtering method and then annealing in O2 or NH3 is applied to form the gate dielectric of the P3HT PTFT. I-V characteristic measurements are performed to characterize the electrical performance of the devices, such as field-effect carrier mobility, threshold voltage, SS, and ON/OFF current ratio. Capacitance-voltage analysis for a metal-polymer-oxide-silicon (MPOS) structure is presented to explain the difference in the electrical properties of the P3HT PTFTs with O<sub>2</sub>-annealed or NH<sub>3</sub>-annealed HfO<sub>2</sub> gate dielectric.

# II. EXPERIMENTAL DETAILS

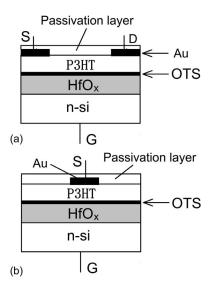

The PTFTs based on P3HT were fabricated using a bottom-gate top-contact configuration. The cross sections of the PTFT and MPOS structure are shown in Fig. 1. N-type  $\langle 100 \rangle$  silicon wafers with a resistivity of 0.2–0.5  $\Omega$  · cm acted as substrate and gate electrode. They were first cleaned according to the standard RCA method, and then, 10% hydrofluoric acid was used to remove the native SiO2 layer. After cleaning, HfO2 gate dielectric was deposited onto the wafers by radio frequency (RF) sputtering (Denton Vacuum LLC Discovery 635) at room temperature. RF power and Ar gas flow rate were kept at 30 W and 24 sccm, respectively, at a deposition pressure of 3.5 mbar. Before the deposition, the vacuum in the chamber was

Manuscript received November 19, 2009; revised January 6, 2010; accepted January 24, 2010. Date of publication February 5, 2010; date of current version June 4, 2010. This work was supported in part by the Natural Science Foundation of Guangdong province (Project 8451064101000257), by the RGC of HKSAR, China (Project HKU 7133/07E), and by the URC for Seed Fund for Strategic Research Theme of HKU on Molecular Materials.

Y. R. Liu and R. H. Yao are with the School of Electronic and Information Engineering, South China University of Technology, Guangzhou 510640, China (e-mail: phlyr@scut.edu.cn; phrhyao@scut.edu.cn).

L. F. Deng and P. T. Lai are with the Department of Electrical and Electronic Engineering, The University of Hong Kong, Hong Kong (e-mail: lfdeng@eee.hku.hk; laip@eee.hku.hk).

Digital Object Identifier 10.1109/TDMR.2010.2042297

Fig. 1. Schematic diagrams of the (a) PTFT and (b) MPOS structure.

kept below  $2 \times 10^{-6}$  torr. The material of the target was HfO<sub>2</sub>. Subsequently, the samples were divided into two groups, each annealed in O2 and NH3, respectively, at 400 °C for 20 min. Hydrofluoric acid with 20% concentration was used to remove the back oxide of the silicon substrate. To improve the interfacial characteristics, all samples were pretreated with a 0.1-ml/ml octadecyltrichlorosilane (OTS) solution in toluene to grow a self-assembling monolayer of OTS by spin coating, and then, the samples were baked in the oven at 90 °C for 10 min. Subsequently, a 10-mg/ml solution of P3HT in chloroform was spin-coated as the semiconducting active layer on the HfO<sub>2</sub> layer at a spin speed of 2000 r/min for 60 s in air. The P3HT obtained from Aldrich was 95% head-to-tail regioregular and 99.995% trace metal basis and used without any additional purification. The molecular weight of P3HT was about 25 000. The P3HT film was then annealed at 90 °C in air for 5 min. Finally, gold was evaporated on the P3HT layer through a shadow mask to form the drain and source electrodes. In order to avoid the performance degradation of the polymer semiconductor due to air exposure, a thin solid paraffin was dissolved to form a thin passivation layer at 80  $^{\circ}\text{C}$  . The shadow mask defined the channel lengths (L) and widths (W) as 30 and 800  $\mu$ m, respectively.

The thickness of the HfO $_2$  layer was measured to be 20 nm by ellipsometry. The thickness of the polymer thin film was determined to be 85 nm by surface profilometry. The electrical characteristics of the PTFT devices and MPOS structures were measured in a light-shielded box without gas protection at room temperature by using an Agilent 4156C semiconductor parameter analyzer and a conventional LCR meter (Agilent 4284A), respectively, combined with a probe station. The conventional field-effect transistor model in the saturation regime was used to extract the field-effect mobility ( $\mu$ ) and threshold voltage ( $V_{\rm th}$ ) of the devices, i.e., using the following equation:

$$I_{D,\text{sat}} = \frac{W}{2L} \mu C_i (V_{\text{GS}} - V_{\text{th}})^2 \tag{1}$$

where  $I_{D,\mathrm{Sat}}$  is the saturation current,  $C_i$  is the capacitance of the gate dielectric per unit area, and  $V_{\mathrm{GS}}$  is the applied

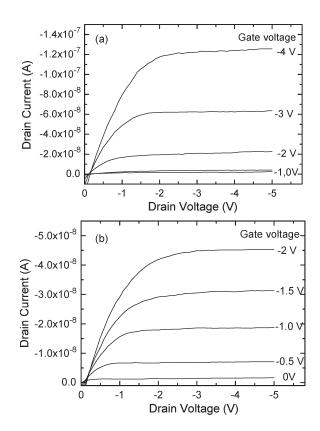

Fig. 2. Output characteristic curves of PTFTs with  $HfO_2$  gate dielectric annealed in (a)  $O_2$  and (b)  $NH_3$  for variable gate voltages.

gate voltage. The ON/OFF current ratio and the SS were also extracted from the transfer characteristic curves.

### III. RESULTS AND DISCUSSION

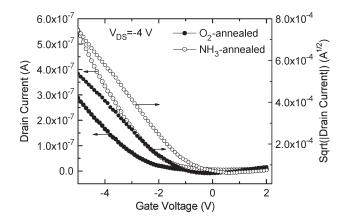

Fig. 2 shows the output characteristics of the PTFTs with  $O_2$ -annealed and  $NH_3$ -annealed  $HfO_2$  as gate dielectric. The two devices show good saturation behavior at low operating voltages ( $V_{\rm GS}=0$  to -5 V). For the  $O_2$ -annealed device, a drain current of 20 nA can be achieved in the saturation region for a gate voltage of -2 V, while for the  $NH_3$ -annealed device, a larger drain current of 45 nA can be achieved in the saturation region for the same gate-bias voltage. Fig. 3 shows the transfer characteristics of the two PTFTs. By utilizing (1), the field-effect mobility of the PTFTs can be deduced from the plot of  $I_D^{1/2}$  versus  $V_{\rm GS}$  according to the following equation:

$$\mu = \frac{2LB^2}{WC_i} \tag{2}$$

where  $B=\partial(I_D)^{1/2}/\partial V_{\rm GS}$  is the slope of the  $I_D^{1/2}$  versus  $V_{\rm GS}$  plot. According to (2), for the  $O_2$ -annealed device, the field-effect mobility calculated from Fig. 3 is  $4.3\times 10^{-3}~{\rm cm^2/V\cdot s}$  in the saturation region for a drain voltage of  $-4~{\rm V}$ , while for the NH<sub>3</sub>-annealed one, the field-effect mobility calculated from Fig. 3 is  $6.2\times 10^{-3}~{\rm cm^2/V\cdot s}$  in the saturation region for the same drain voltage. From Fig. 3, the threshold voltage is deduced to be -1.0 and  $-0.5~{\rm V}$  for the  $O_2$ - and NH<sub>3</sub>-annealed devices, respectively. The parameters of the two devices extracted from their transfer characteristics are summarized in

Fig. 3. Transfer characteristic curves of PTFTs with HfO $_2$  gate dielectric annealed in  $O_2$  and NH $_3$  at a drain voltage of -4 V.

### TABLE I

Summarized Device Parameters of the P3HT PFETs With O<sub>2</sub>-Annealed HfO<sub>2</sub> and NH<sub>3</sub>-Annealed HfO<sub>2</sub>.  $t_{\rm ox}$ ,  $\varepsilon_i$ ,  $\mu$ ,  $V_{\rm th}$ , SS, and  $I_{\rm on}/I_{\rm off}$  Represent the Dielectric Thickness, Relative Dielectric Constant, Field Effect Mobility, Threshold Voltage, Subthreshold Swing, and the on/off Current Ratio, Respectively

| Treatment condition                            | O <sub>2</sub> -annealed | NH <sub>3</sub> -annealed |

|------------------------------------------------|--------------------------|---------------------------|

| $t_{OX}(\text{nm})$                            | 20                       | 19.5                      |

| $C_i  (\text{nF/cm}^2)$                        | 280                      | 332                       |

| $arepsilon_i$                                  | 6.3                      | 7.3                       |

| $\mu (\times 10^{-3} \text{ cm}^2/\text{V s})$ | 4.3                      | 6.2                       |

| $V_{th}(V)$                                    | -1.0                     | -0.5                      |

| SS (V/decade)                                  | 1.8                      | 1.7                       |

| $I_{on}/I_{off}$                               | 80                       | 150                       |

Table I. Compared with the O<sub>2</sub>-annealed device, the NH<sub>3</sub>-annealed device presents better electrical performance, such as higher field-effect mobility, larger ON/OFF current ratio, reduced threshold voltage, and smaller SS.

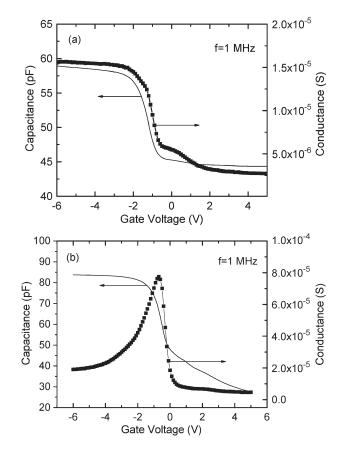

To identify the origin of the differences in the electrical properties of the two P3HT PTFTs, capacitance-voltage measurements are made to analyze the properties of the MPOS structures with O<sub>2</sub>-annealed HfO<sub>2</sub> and NH<sub>3</sub>-annealed HfO<sub>2</sub>, particularly the difference of trapped charges in the bulk semiconductor and at the insulator/semiconductor interface. Fig. 4 shows the capacitance and equivalent parallel conductance measured at 1 MHz as a function of gate bias for the MPOS structures with  $O_2$ -annealed  $HfO_2$  and  $NH_3$ -annealed HfO<sub>2</sub>. For the O<sub>2</sub>-annealed device, the absence of a peak in the conductance–voltage (G-V) curve [Fig. 4(a)] means that series resistance  $(R_s)$  produces the dominant loss, completely masking the interface-trap loss. On the other hand, a clear peak in the G-V curve is shown in Fig. 4(b) for the NH<sub>3</sub>-annealed device, indicating that there is a small series resistance in the MPOS structure. The series resistance can be expressed as [15]

$$R_s = \frac{G_{\rm ma}}{G_{\rm ma}^2 + \omega^2 C_{\rm ma}^2} \tag{3}$$

where  $G_{\rm ma}$  and  $C_{\rm ma}$  are the equivalent parallel conductance and the capacitance when the MPOS structure is biased into strong accumulation. According to (3), the series resistances

Fig. 4. Capacitance and equivalent parallel conductance measured at 1 MHz as a function of gate bias for the MPOS structures with (a)  $O_2$ -annealed  $HfO_2$  and (b)  $NH_3$ -annealed  $HfO_2$ . Gate area is  $2.5 \times 10^{-4}$  cm<sup>-2</sup>.

extracted from the G-V and C-V curves in Fig. 4(a) and (b) are 210.1 and 68.6  $\Omega$ , respectively. Here, the smaller series resistance in the MPOS structure with NH<sub>3</sub>-annealed HfO<sub>2</sub> is mainly attributed to the smaller contact resistance between metal and polymer or smaller bulk resistance between the back contact to the polymer and the depletion layer edge underneath the gate, because a larger current can be obtained between source and drain electrodes when the gate electrode is open.

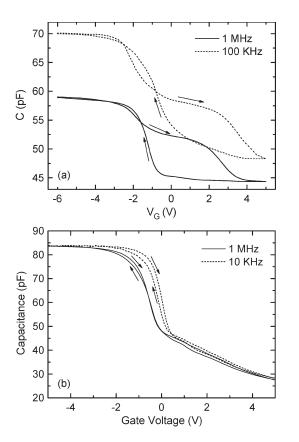

Fig. 5 shows the C-V hysteresis curves of the MPOS structures with O<sub>2</sub>-annealed HfO<sub>2</sub> and NH<sub>3</sub>-annealed HfO<sub>2</sub> for two test frequencies. For the O2-annealed sample, the frequency dependence of the capacitance is observed obviously, i.e., the capacitance decreasing with increasing test frequency in the accumulation region, which is due to long relaxation time for the polymer semiconductor bulk [16] or charge trapping in the states at the polymer/dielectric interface [17]. In addition, the C-V curve in Fig. 5(a) shows a clear kink in the depletion region for the sweep direction from accumulation to depletion, and the kink effect becomes more obvious as the test frequency decreases. However, the kink effect disappears for the opposite sweep direction from depletion to accumulation, indicating that the kink effect originates from the trap effect of majority carriers (holes) at the dielectric/polymer interface or within the polymer bulk. However, for the NH<sub>3</sub>-annealed sample, the capacitance of the MPOS structure in accumulation region does not depend on the test frequency, indicating that the trap

Fig. 5. C-V hysteresis curves of the MPOS structures with (a)  $O_2$ -annealed  $HfO_2$  and (b)  $NH_3$ -annealed  $HfO_2$  for various frequencies. The arrows indicate the sweep direction of the gate-bias voltage.

states at the interface or in the bulk of the polymer in the MPOS structure with  $NH_3$ -annealed  $HfO_2$  are less than those in the  $O_2$ -annealed counterpart. Moreover, a slight hysteresis can be observed, and the hysteresis effect becomes larger with the decrease of the test frequency. Normally, the hysteresis is mainly associated with charge trapping at the  $P3HT/HfO_2$  interface. The interface trap state density can be estimated by

$$N_t = \frac{C_i \Delta V}{q} \tag{4}$$

where q is the electronic charge,  $C_i$  is the capacitance per unit area of the dielectric layer, and  $\Delta V$  is the flatband voltage shift in the C--V hysteresis curves. According to (4), the interface trap state density can be estimated as  $7.0 \times 10^{12}~\text{cm}^{-2}$  at a frequency of 100 kHz for the  $O_2$ -annealed sample, while the value is  $4.2 \times 10^{11}~\text{cm}^{-2}$  at a frequency of 10 kHz for the NH<sub>3</sub>-annealed sample. Based on the aforementioned analysis of the electrical characteristics for the two MPOS structures, it can be deduced that the better electrical performance of the PTFT with NH<sub>3</sub>-annealed HfO<sub>2</sub> should be due to lower trap states at the interface or in the bulk of the polymer and smaller series resistance in the transistor.

# IV. CONCLUSION

We have investigated P3HT PTFTs with HfO<sub>2</sub> as gate dielectric, which is deposited by RF sputtering and then annealed at 400 °C in  $\rm O_2$  and  $\rm NH_3$ , respectively. Both PTFTs show a small threshold voltage and a low operating voltage, arising from the high gate capacitance per unit area of the  $\rm HfO_2$  gate dielectric. Compared with the PTFT with  $\rm O_2$ -annealed  $\rm HfO_2$ , the PTFT with  $\rm NH_3$ -annealed  $\rm HfO_2$  displays higher carrier mobility, larger  $\rm ON/OFF$  current ratio, lower threshold voltage, and smaller SS due to reductions of interface trap states and series resistance in the transistor. The results suggest that the PTFT is suitable for low-voltage and low-power applications in organic electronics.

# REFERENCES

- P. Andersson, R. Forchheimer, P. Tehrani, and M. Berggren, "Printable all-organic electrochromic active-matrix displays," *Adv. Funct. Mater.*, vol. 17, no. 16, pp. 3074–3082, 2007.

- [2] Y. X. Liu and T. H. Cui, "Polymeric integrated AC follower circuit with a JFET as an active device," *Solid State Electron.*, vol. 49, no. 3, pp. 445– 448, Mar. 2005.

- [3] H. N. Raval, S. P. Tiwari, R. R. Navan, and V. R. Rao, "Determining ionizing radiation using sensors based on organic semiconducting material," *Appl. Phys. Lett.*, vol. 94, no. 12, p. 123 304, Mar. 2009.

- [4] H. C. Yang, T. J. Shin, L. Yang, K. Cho, C. Y. Ryu, and Z. N. Bao, "Effect of mesoscale crystalline structure on the field-effect mobility of regioregular poly(3-hexyl thiophene) in thin-film transistors," *Adv. Funct. Mater.*, vol. 15, no. 4, pp. 671–676, 2005.

- [5] J. H. Park, S. J. Kang, J. W. Park, B. Lim, and D. Y. Kim, "Enhancement of field effect mobility of poly(3-hexylthiophene) thin film transistors by soft-lithographical nanopatterning on the gate-dielectric surface," *Appl. Phys. Lett.*, vol. 91, no. 22, p. 222 108, Nov. 2007.

- [6] Y. D. Park, D. H. Kim, J. A. Lim, J. H. Cho, Y. Jang, W. R. Lee, J. H. Park, and K. Cho, "Enhancement of field-effect mobility and stability of poly(3-hexylthiophene) field-effect transistors by conformational change," J. Phys. Chem. C, vol. 112, no. 5, pp. 1705–1710, 2008.

- [7] L. A. Majewski and A. M. Song, "Extended storage time of poly(3-hexylthiophene) field-effect transistors via immersion in common solvents," *J. Appl. Phys.*, vol. 102, no. 7, p. 074 515, Oct. 2007.

- [8] D. H. Kim, Y. D. Park, Y. S. Jang, H. C. Yang, Y. H. Kim, J. I. Han, D. G. Moon, S. J. Park, T. Y. Chang, C. W. Chang, M. K. Joo, C. Y. Ryu, and K. W. Cho, "Enhancement of field-effect mobility due to surface-mediated molecular ordering in regioregular polythiophene thin film transistors," *Adv. Funct. Mater.*, vol. 15, no. 1, pp. 77–82, 2005.

- [9] S. Grecu, M. Roggenbuck, A. Opitz, and W. Brutting, "Differences of interface and bulk transport properties in polymer field-effect devices," *Org. Electron.*, vol. 7, no. 5, pp. 276–286, Oct. 2006.

- [10] S. Cho, K. Lee, J. Yuen, G. M. Wang, D. Moses, A. J. Heeger, M. Surin, and R. Lazzaroni, "Thermal annealing-induced enhancement of the field-effect mobility of regioregular poly(3-hexylthiophene) films," *J. Appl. Phys.*, vol. 100, no. 11, p. 114503, Dec. 2006.

- [11] C. Bartic, H. Jansen, A. Campitelli, and S. Borghs, "Ta<sub>2</sub>O<sub>5</sub> as gate dielectric material for low-voltage organic thin-film transistors," *Org. Electron.*, vol. 3, no. 2, pp. 65–72, Jun. 2002.

- [12] H. N. Raval, S. P. Tiwari, R. R. Navan, S. G. Mhaisalkar, and V. R. Rao, "Solution-processed bootstrapped organic inverters based on P3HT with a high-K gate dielectric material," *IEEE Electron Device Lett.*, vol. 30, no. 5, pp. 484–486, May 2009.

- [13] N. Wu, Q. C. Zhang, C. X. Zhu, D. S. H. Chan, M. F. Li, N. Balasubramanian, A. Chin, and D.-L. Kwong, "Alternative surface passivation on germanium for metal-oxide-semiconductor applications with high-k gate dielectric," *Appl. Phys. Lett.*, vol. 85, no. 18, pp. 4127–4129, Nov. 2004.

- [14] T. J. Park, S. K. Kim, J. H. Kim, J. Park, M. J. Cho, S. W. Lee, S. H. Hong, and C. S. Hwang, "Electrical properties of high-k HfO<sub>2</sub> films on Si<sub>1-x</sub>Ge<sub>x</sub> substrates," *Microelectron. Eng.*, vol. 80, no. 1, pp. 222– 225, Jun. 2005.

- [15] E. H. Nicollian and J. R. Brews, MOS (Metal Oxide Semiconductor) Physics and Technology. New York: Wiley, 1982, ch. 5.

- [16] E. J. Meijer, A. Mangnus, C. Hart, and D. M. de Leeuw, "Frequency behavior and the Mott-Schottky analysis in poly(3-hexyl thiophene) metal-insulator-semiconductor diodes," *Appl. Phys. Lett.*, vol. 78, no. 24, pp. 3902–3904, Jun. 2001.

- [17] Î. Torres, D. Taylor, and E. Itoh, "Interface states and depletion-induced threshold voltage instability in organic metal-insulator-semiconductor structures," Appl. Phys. Lett., vol. 85, no. 2, pp. 314–316, Jul. 2004.

Y. R. Liu received the B.S. degree in semiconductor physics from Jiangxi University, Ganzhou, China, in 1991, the M.Sc. degree in condensed physics from Sichuan University, Sichuan, China, in 1996, and the Ph.D. degrees in microelectronics and solid state electronics from South China University of Technology, Guangzhou, China, in 2007.

He is currently an Associate Professor with the School of Electronic and Information Engineering, South China University of Technology. His current research interests include inorganic/organic thin-film

transistors, solar cells, and microsensors.

**R. H. Yao** received the B.S. degree in sciences from Sun Yat-Sen University, Kaohsiung, Taiwan, in 1982 and the Ph.D. degree from the Chinese Academy of Sciences, Beijing, China, in 2004.

He was previously a Professor with the Department of Physics and the Dean of the School of Sciences, Shantou University, Shantou, China. Since 2002, he has been a Professor with the Institute of Microelectronics, South China University of Technology, Guangzhou, China, where he is currently the Vice-Dean of the School of Electronic and Infor-

mation Engineering. He has published well over 100 papers to journals and international conferences and is the holder of four patents. His current research interests include semiconductor device and microelectronics techniques.

L. F. Deng received the B.S. degree in applied physics from Hefei University of Technology, Hefei, China, in 2003 and the M.Sc. degree in microelectronics from Huazhong University of Science and Technology, Wuhan, China, in 2007. He is currently working toward the Ph.D. degree in the Department of Electrical and Electronic Engineering, The University of Hong Kong, Hong Kong.

His current research concentrates on organic thinfilm transistors.

P. T. Lai (M'90–SM'04) received the B.Sc.(Eng.) and Ph.D. degrees from The University of Hong Kong, Hong Kong. His Ph.D. research was on the design of small-sized MOS transistor with emphasis on narrow-channel effects. The work involved the development of both analytical and numerical models, the study of this effect in relation to different isolation structures, and the development of efficient numerical algorithms for device simulation.

He was a Postdoctoral Fellow with the University of Toronto, Toronto, ON, Canada. He has proposed

and implemented a novel self-aligned structure for bipolar transistor and designed and implemented an advanced polyemitter bipolar process with emphasis on self-alignment and trench isolation. He is currently a Professor with the Department of Electrical and Electronic Engineering, The University of Hong Kong. His current research interests are on thin gate dielectrics for FET devices based on Si, SiC, GaN, Ge, and organics and on microsensors for detecting gases, heat, light, and flow.